1、背景

最近在某个项目中,遇到输入给FPGA管脚的外部触发信号因为有毛刺产生,导致FPGA接收到的外部触发信号数量多于实际值。比如:用某个信号源产生1000个外部触发信号(上升沿触发方式)给到FPGA输入IO,实际上FPGA内部逻辑判定接收到的触发信号数量大于1000个,且数量为随机性。因为毛刺的产生的个数具有随机性。

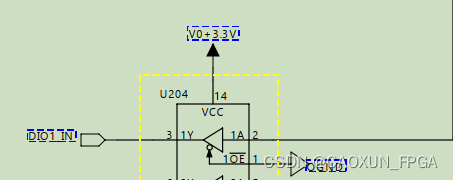

2、原理图设计

外部触发信号经过Buffer器件(74HCT125D)输入端整形后,输出端DIO1_IN连接到FPGA的输入管脚。

3、测试过程

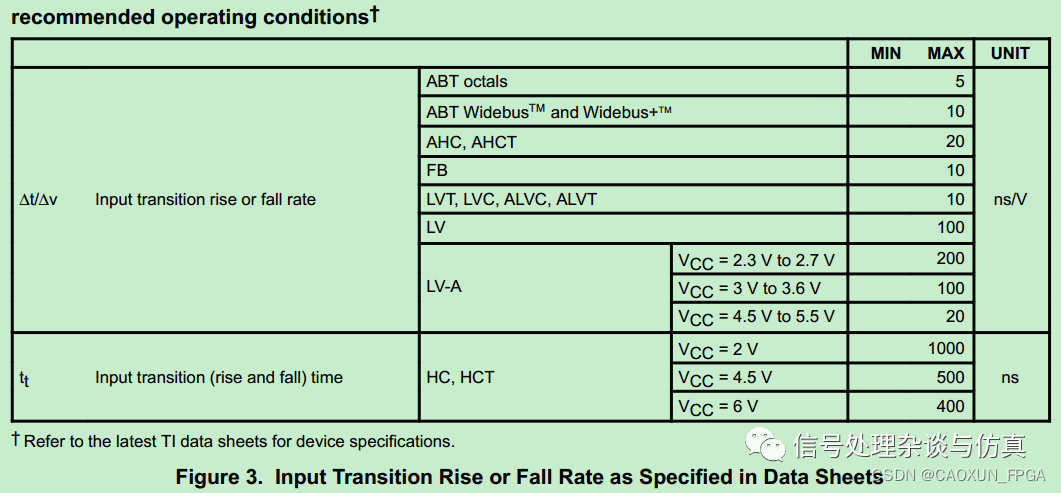

外部上升沿触发信号特征为:高电平脉宽为10us,上升沿时间为5us,故该触发信号对于数字IO输入信号而言,属于一个上升时间缓慢的输入信号。远远不满足输入信号的上升/下降转换时间指标要求。参见下图所示。

实测发现,这个上升时间缓慢的输入信号会导致Buffer(74HCT125D)器件额外产生一个上升沿毛刺。以前没有遇到过这种情况,这次算是增加了一个经验。

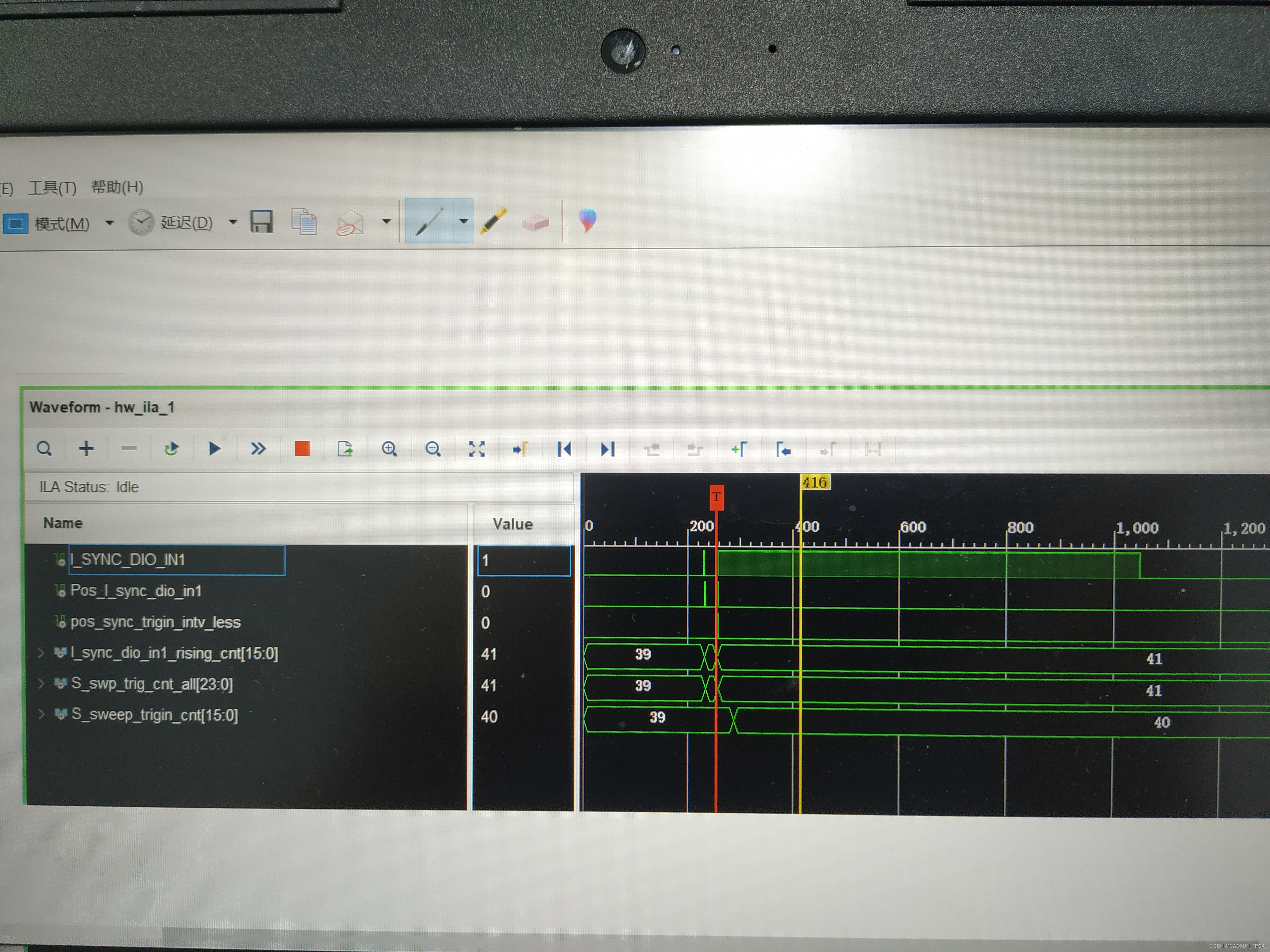

上图中,I_SYNC_DIO_IN1为FPGA管脚,用于接收经过BUFFER器件的外部触发信号。由

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7524

7524

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?