摘要

本文关于基于fpga的cmos工业相机项目工程概览与总结,涉及以下内容:

1、模块总结:整体设计方案、子模块划分、关键技术点/信号

2、调试:关键模块、信号的仿真、调试总结

3、硬件布局:引脚配置、核心供电等硬件、结构设计总结

4、方案优化:现有方案的优化、改造及向新方案的靠拢分析

1模块总结

1.1概述

●CMOS CL0402 作为图像传感芯片,曝光后产生一定格式的图像数据;

●FPGA ZYNQ7020 作为主控芯片负责cmos驱动控制、图像像素的采集、cmos寄存器的配置、cameralink协议的实现、上位机串口通信的实现;

●Cameralink端子实现图像数据的高速串行发送,将数据传送至采集卡PC端。

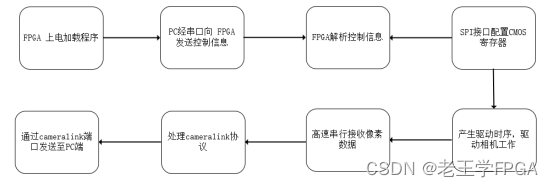

系统工作流程如下: FPGA 上电加载配置程序,计算机通过异步串口向 FPGA 发送控制信息,FPGA对接收的控制信息进行分析判断。通过SPI接口设 置 CMOS 工 作 模 式,通过判断的信息产生相机的驱动时序,实现相机的正常工作。相机被驱动后,数字图像数据通过 LVDS 信号输 出给主控芯片 FPGA,FPGA 将接收的图像数据进行处理,转换为 Camera-Link 标准数据,通过 Camera-Link 接口芯片输给后端装有 Camera-Link 采集卡的计算机,计算机对接收的数据进行处理、存储。

图 1-1 项目工作流程

1.1.1顶层端口

顶层的端口主要包括几个部分,分别是cmos触发端口、cmos寄存器配置端口、cmos图像数据端口、cameralink端口、串口通信端口

表1-1 顶层模块端口描述

| 端口名 | 方向/位宽 | 描述 |

| etgr_in | I/1bit | 外部触发源信号输入 |

| triggle | O/1bit | cmos触发信号输出 |

| cmos_rstn | O/1bit | cmos复位信号 |

| cp | I/4bit | 采集卡输出的控制信号p端,作为外触发方式之一 |

| cn | I/4bit | 采集卡输出的控制信号n端,作为外触发方式之一 |

| spi_clk | O/1bit | Spi接口时钟信号 |

| spi_in | O/1bit | spi写信号 |

| spi_cs | O/1bit | Spi片选信号,高有效 |

| spi_out | I/1bit | spi读信号线 |

| CMOS_O_Cp | I/12bit | Cmos输出12通道像素数据P |

| CMOS_O_Cn | I/12bit | Cmos输出12通道像素数据n |

| CMOS_p | I/1bit | cmos输出240M像素时钟p |

| CMOS_p | I/1bit | cmos输入240M像素时钟p |

| clkp_in | O/1bit | cmos输入480M参考时钟p |

| clkn_in | O/1bit | cmos输入480M参考时钟n |

| clk_to_pins_p | O/1bit | Cameralink输入时钟p(40M) |

| clk_to_pins_n | O/1bit | Cameralink输入时钟n(40M) |

| data_out_to_pins_p | O/4bit | cameralink的4组串行数据通道 |

| data_out_to_pins_p | O/4bit | cameralink的4组串行数据通道 |

| sertc_p | I/1bit | 串口输入p端,与PC通信 |

| sertc_n | I/1bit | 串口输入n端,与PC通信 |

| sertfg_p | O/1bit | 串口输出p端,与PC通信 |

| sertfg_n | O/1bit | 串口输出n端,与PC通信 |

| p_e1 | O/1bit | Cmos VDD1 上电使能 |

| p_e2 | O/1bit | Cmos VDD2 上电使能 |

| p_e3 | O/1bit | Cmos VDD3 上电使能 |

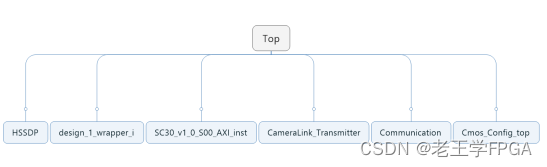

1.1.2模块划分

整个fpga编程主要划分为以下几个部分或模块:

- cmos 高速串行数据采集模块HSSDP

- Cameralink传输模块 CameraLink_Transmitter

- Cmos寄存器配置模块Cmos_Config_top

- PC通信模块Communication

- AXI协议模块

- Zynq 系统配置核

将各子模块分别封装成独立模块,在顶层中例化使用。

图 1-3 模块划分结构图

表1-2 子模块功能描述

| 模块名 | 功能描述 |

| HSSDP | 采集图像数据,Cmos高速串行数据转并行 |

| CameraLink_Transmitter | 实现cmeralink协议,将数据送至cmeralink端口 |

| Cmos_Config_top | 实现spi读写时序、上电时序,对cmos的寄存器进行配置 |

| Communication | 实现串口读写时序、解析上位机通信协议、根据触发模式生成cmos触发信号等。 |

| design_1_wrapper_i | Zynq system 配置顶层 |

| SC30_v1_0_S00_AXI_inst | AXI 协议,实现PS端对PL端的读写 |

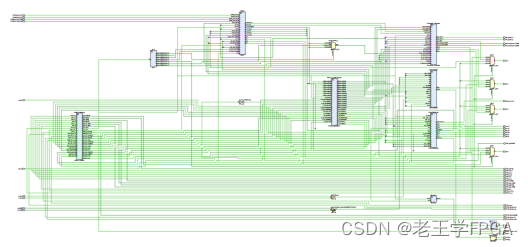

图 1-4 项目的RTL视图

1.2主要子模块介绍

1.2.1 Cmos_Config_top 模块

主要负责寄存器的配置、实现spi读写协议、实现上电顺序控制。

图 2-1 Cmos_Config_top端口示意图

表 2-1 Cmos_Config_top主要端口描述

| 端口名 | 方向/位宽 | 描述 |

| Read_add | I/8bit | Fpga读cmos寄存器的地址 |

| Rxbuff | O/32bit | Fpga读出的cmos寄存器数据(返回到PS端处理) |

| spi_out | I/1bit | Fpga读cmos寄存器spi端口 |

| Rx_en | I/1bit | Fpga读cmos寄存器使能信号 |

| Write_add | 1/8bit | Fpga写cmos寄存器的地址 |

| Write_data | I/8bit | Fpga写cmos寄存器数据 |

| tx_en | I/1bit | Fpga写cmos寄存器使能信号 |

| spi_in | O/1bit | Fpga写cmos寄存器spi端口 |

| Spi_bit_rate | I/6bit | Spi的比特率 |

| Spi_cs | O/1bit | spi片选信号,高有效 |

| Spi_clk | O/1bit | Spi时钟,最大5M |

| Stream_en | O/1bit | 寄存器配置完成标志信号 |

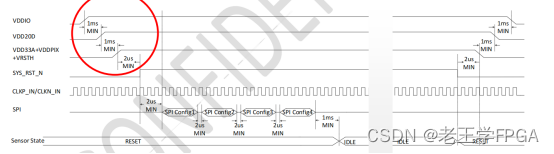

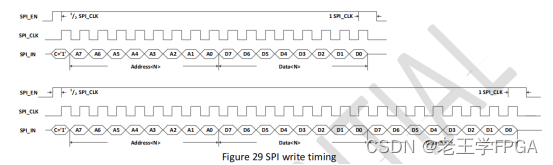

Cmos配置时序:

图 2-2 Cmos上电时序图

图 2-3 spi写cmos寄存器时序

图 2-4 spi读cmos寄存器时序

1.2.2 HSSDP 模块

端口描述:

图 2-4 HSSDP端口示意图

表 2-2 HSSDP主要端口描述

| 端口名 | 方向/位宽 | 描述 |

| CMOS_SLVS_Cn | I/1bit | cmos输出像素采样时钟n端 |

| CMOS_SLVS_Cp | I/1bit | cmos输出像素采样时钟p端 |

| CMOS_SLVS_n | I/12bit | cmos像素输出通道n端 |

| CMOS_SLVS_p | I/12bit | cmos像素输出通道p端 |

| m_axis_tdata | O/8bit | Axis 数据线 |

| m_axis_tkeep | O/1bit | 字节有效标志。1:数据线高8位有效 |

| m_axis_tlast | O/1bit | 行结束标志 |

| m_axis_tuser | O/1bit | 帧结束标志 |

| m_axis_tvalid | O/1bit | 数据有效 |

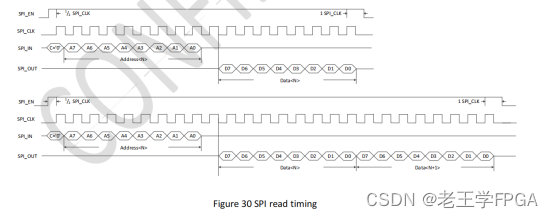

Cmos数据格式:

图 2-5 cmos的数据读出格式

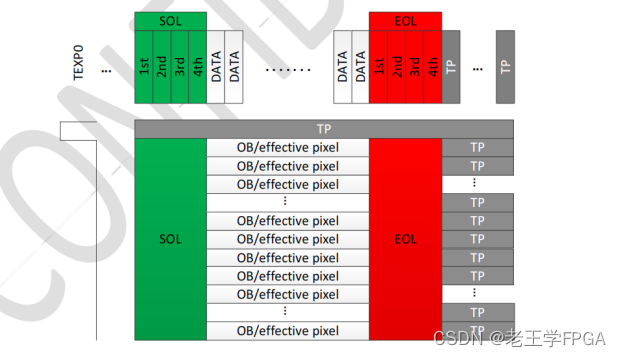

FPGA处理:

图 2-6 HSSDP 模块处理步骤

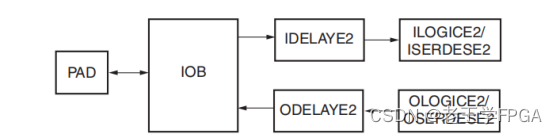

通过clk和data两对差分线进行传输,由于clk的布线与data的布线存在长短上的差异,主机传输到从机后clk和data的延时各不相同。如果我们希望在时钟上升沿上采集数据,但由于线的延时,可能在时钟上升沿时数据处于变化状态,这将会导致采集的数据错误。通过IDELAYE2原语可将某根信号线进行延时操作(目前状态延时1092ps),以达到在时钟上升沿数据处于稳定的操作。如果当clk和data信号延时较大时,仅仅使用IDELAYE2无法达到预期,此时ISERDESE2就派上用途。

图 2-6 xilinx的SelectIO Logic Resources

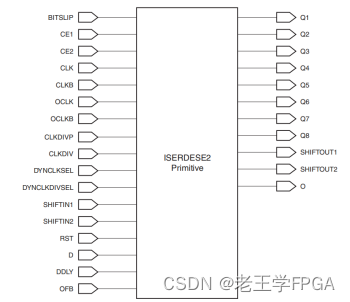

当ISERDESE2(例化12个)的输出端口为8位时,由于cmos的像素时12位的,需要进行bit拼接。

图 2-7 xilinx的ISERDES2 示意图

图 2-8 缓存排序仿真

1.2.3 CameraLink_Transmitter模块

端口描述:

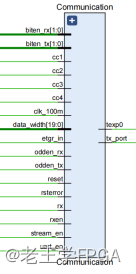

图 2-15 communication模块端口示意图

表 2-3 communication模块主要端口描述

| 端口名 | 方向/位宽 | 描述 |

| cc1、cc2、cc3、cc4 | I/1bit | PC端采集卡触发 |

| data_width | I/20bit | 串口位脉宽(表征波特率) |

| etgr_in | I/1bit | 外部触发信号 |

| rsterror | I/1bit | 接收校验错误后复位 |

| rx | 1/1bit | 串口接收 |

| stream_en | I/1bit | cmos配置完后使能触发模块 |

| tx_port | O/1bit | 串口发送 |

| tex_p0 | O/1bit | cmos触发信号(trigger) |

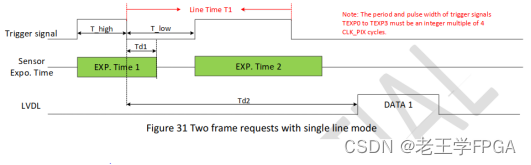

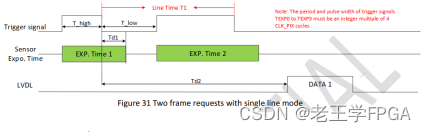

cmos 触发时序:

内部触发

定义:相机通过设备内部信号采集每行图像,并根据相关参数的设置输出每帧图像。

图 2-16 cmos触发信号时序

● Trigger signal:fpga内部根据时序和上位机参数要求产生

● 触发源:无

● 参数:每帧的行数、帧/行频、曝光时间

相关参数:

1)每帧行数

帧触发时,用来控制输出图像的高度

2)曝光时间

曝光时间=T_high+Td1

3)行/帧频

行时间=T_high+T_low;行频=1/(T_high+T_low)

帧时间=Hwidth*行时间;帧频=1/帧时间。

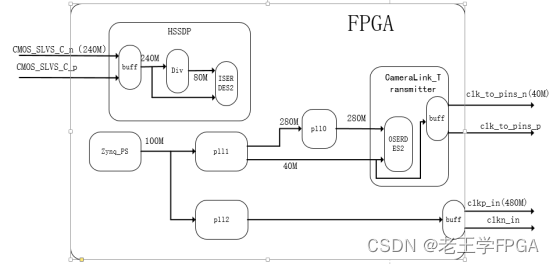

1.2.5 时钟部分

时钟概述:

图 2-17 主要时钟信号示意图

时钟说明:

CMOS_SLVS_C_n(p):cmos 输出的像素采样时钟,240M,为DDR差分对时钟信号。用于串行像素数据信号的采样。

Clk_to_pins_n(p):cameralink接口的时钟输入40M

Clkp(n)_in: cmos的驱动时钟480M。

HSSDP:将输入的差分时钟转单端,再利用分频器将其分频为80M时钟,作为ISERDES2的快、慢时钟输入。

Cameralink_Transmitter: pll1生成两路时钟分别是280M和40M,pll0对pll1输出的280M时钟进行相位调整。280M和40M分别作为OSERDES2的快。慢时钟输入。

457

457

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?