最近后台收到大量关于“Vivado安装包”的私信,发现不少小伙伴还在苦苦搜寻第三方网盘资源。其实,Vivado完全可以通过官网直接下载,安全高效!第三方网盘不仅速度慢,还可能存在版本混乱、捆绑插件等风险。今天就来聊聊如何科学获取Vivado,并揭秘各版本特点,最后安利一个“轻量神器”——Lab版,仅1GB就能完成程序下载!

一、Vivado的正确下载方式

为什么推荐官网下载?

-

版本齐全Xilinx(现AMD)官网提供所有历史版本,从经典版到最新版一应俱全 。

-

安全可靠 避免第三方网盘可能携带的病毒或插件

-

更新及时 官网会同步发布补丁和新功能支持,如UltraScale+和Versal架构优化

官网下载步骤:

-

访问Xilinx官网,选择所需版本

-

注册账号后即可下载完整安装包(需注意官网下载需登录,注册使用自己的QQ邮箱即可)

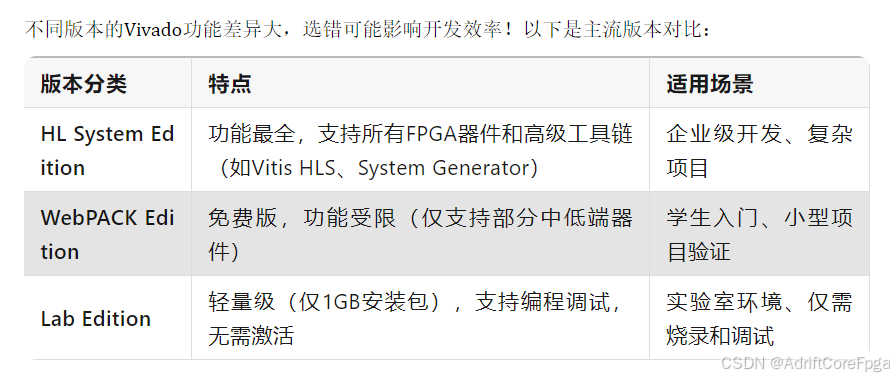

二、Vivado版本怎么选?看这一张表就懂!

不同版本的Vivado功能差异大,选错可能影响开发效率!以下是主流版本对比:

版本选择Tips:

偶数版本更稳定:如2020.2、2022.2,修复了奇数版本的Bug 。

新版本优化明显:2023.2编译速度提升20%,且支持最新UltraScale+器件

Linux编译更快:相同项目在Linux下速度可提升30%

三、Vivado Lab Edition

如果你只需要烧录程序或调试硬件,不必安装几十GB的完整版!Lab Edition堪称“小而美”的解决方案

体积仅1GB:安装后占用约2.4GB空间,对低配电脑友好 。

功能专精:支持比特流下载、硬件管理器调试(如ILA、VIO核) 无需许可证:直接使用,适合实验室多人共享环境 适用场景:

-

已生成比特流(.bit文件),仅需烧录到FPGA。

-

调试已部署的硬件设计,无需重新编译。

安装方法:在官网下载Unified Installer时勾选“Lab Edition”即可

四、安装避坑指南

系统要求:Windows需64位,推荐Win10/Win11,内存≥8GB,硬盘空间≥50GB ,关闭杀毒软件,避免安装拦截

路径设置:安装路径和工程目录避免中文或特殊符号

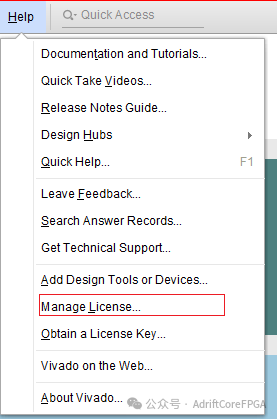

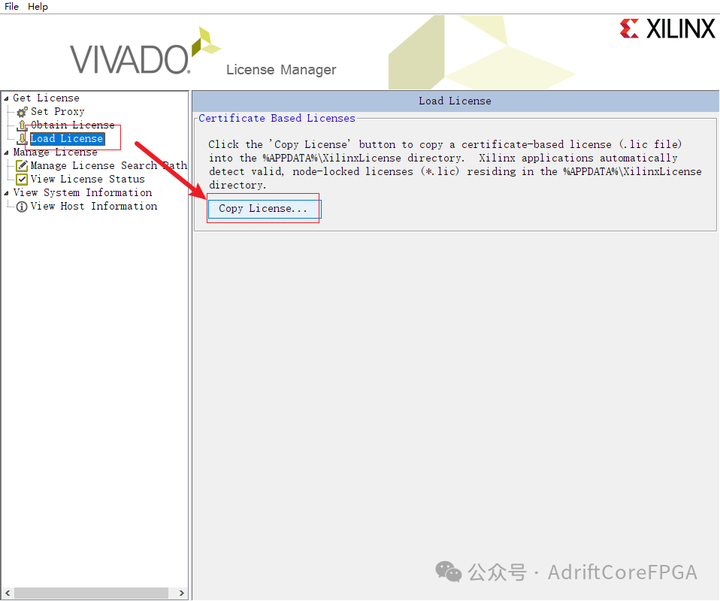

许可证激活:企业版需加载.lic文件,可联系官方或学校获取

往期回顾

用Python给Verilog设计自仿(一):Cocotb环境初探

用Python给Verilog设计自仿(二):用D触发器解锁自动化验证的「第一个波形」

用Python给Verilog设计自仿(三):Cocotb高频语法,从此告别SV手写

用Python给Verilog设计自仿(四):协程调度全解析,仅需三行代码构建以太网帧

欢迎关注微信公众号【AdriftCoreFpga】,获取第一时间更新

5144

5144

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?