点击下方卡片,关注“3D视觉之心”公众号

第一时间获取3D视觉干货

更多干货,欢迎加入国内首个具身智能全栈学习社区:具身智能之心知识星球(戳我),这里包含所有你想要的。

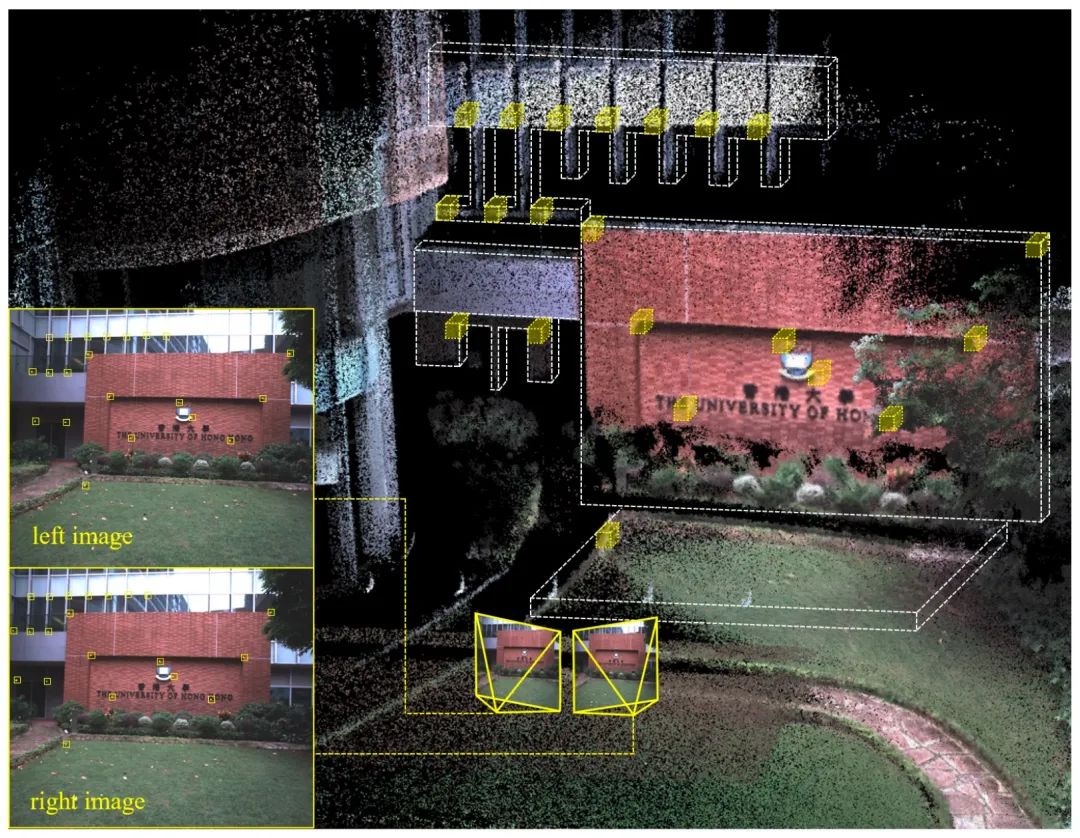

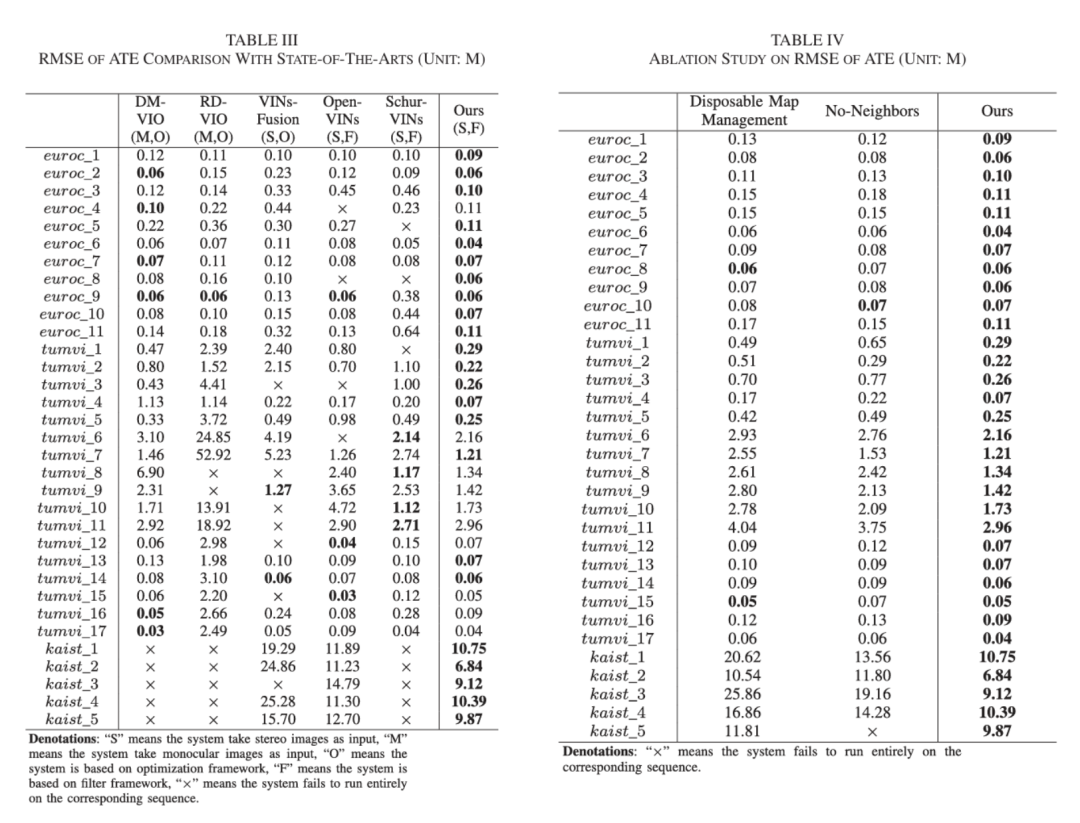

Voxel-SVIO是一种基于体素地图的立体视觉-惯性里程计框架,该框架能够高效筛选出最适合参与优化的地图点,从而确保将计算资源优先分配给对状态优化最为关键的变量。如下图所示,绿色体素内的地图点会被输入至估计器,用于基于MSCKF的状态更新。

快速使用

论文链接:Voxel-SVIO: Stereo Visual-Inertial Odometry Based on Voxel Map | IEEE Journals & Magazine | IEEE Xplore

源码链接(含Demo演示):ZikangYuan/voxel_svio: [RA-L 2025 Accept without Revision] A stereo visual-inertial odometry system based on voxel map

方法概述

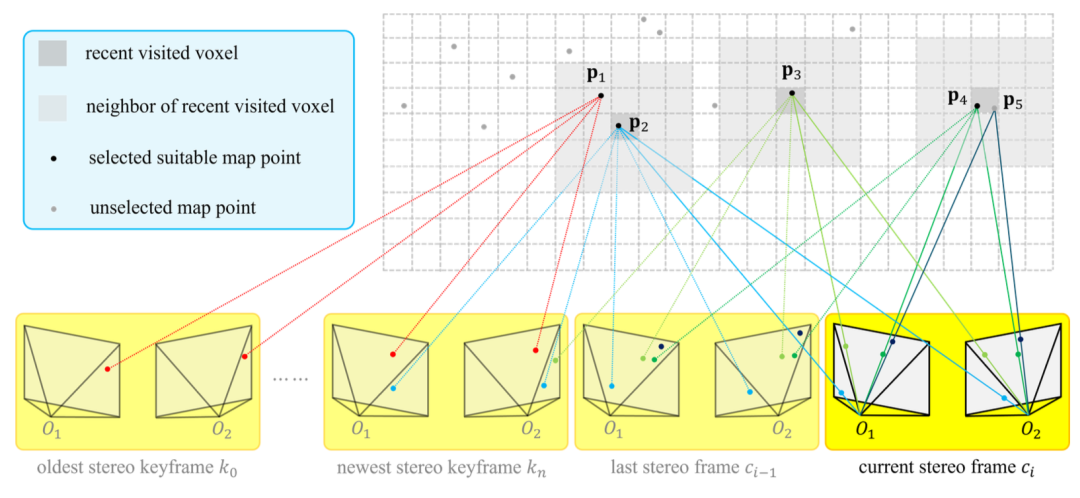

在视觉-惯性里程计(VIO)系统中,将有限的计算资源优先分配给新帧的约束更有利于提升状态估计的精度,因为旧帧已经历过多次更新。为使VIO系统能够高效索引新帧在三维空间中观测到的地图点,本文首次将体素地图管理引入VIO领域,并自主开发了名为Voxel-SVIO的立体视觉-惯性里程计系统。基于当前立体图像特征匹配的三角化结果,我们可以直接索引三维空间中最近访问的体素单元。这些体素单元内的地图点能为新帧提供充足约束条件,因此适合输入至状态估计器。

基于当前立体图像(彩色实线表示)特征匹配的三角化结果,我们可以直接索引三维空间中最近访问的体素(深灰色网格)及其邻近体素(浅灰色网格)。这些体素内的地图点能够为新帧(彩色虚线表示)提供足够的约束条件,因此被选为合适的地图点(黑色点 p1 ∼ p5)。为确保合适地图点的均匀分布并控制计算负载,每个体素最多选取一个特征点。

系统框架简介

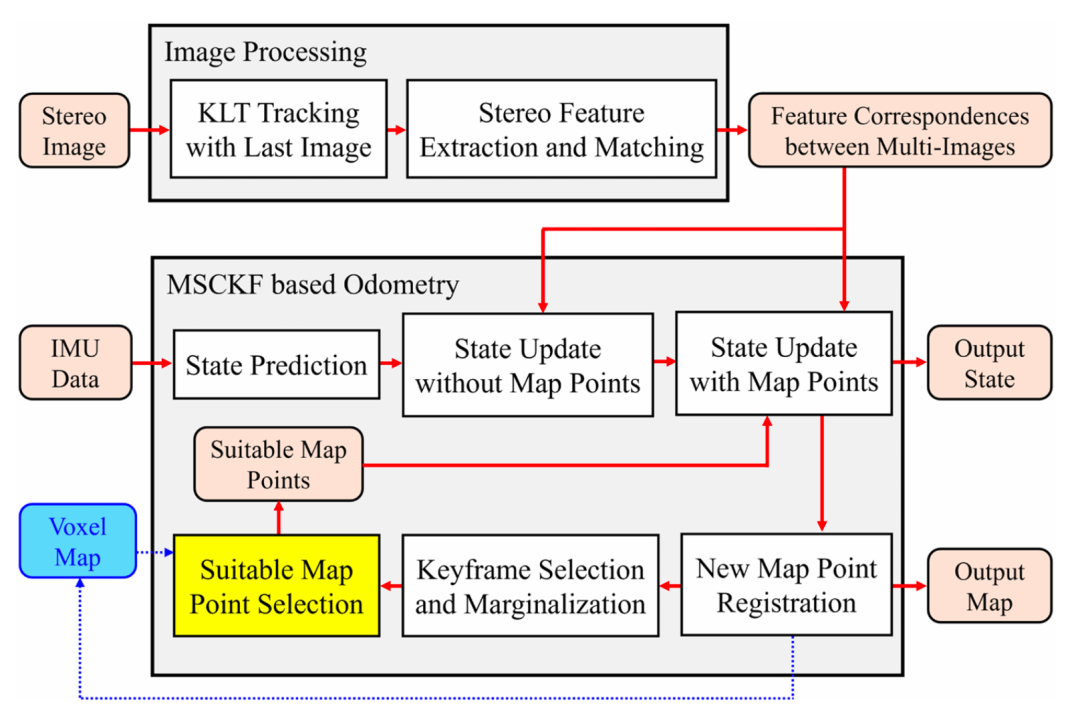

当立体图像输入时,图像处理模块采用KLT光流法追踪当前帧与上一帧之间的特征匹配点。随后,系统会对当前帧中特征点稀疏区域进行补充检测,并通过左右图像立体匹配获取多视角特征对应关系。

基于这些特征匹配点,MSCKF里程计模块的处理流程如下:

状态预测:先利用惯性测量数据进行运动状态预测

临时三角化:对滑动窗口内所有帧的2D特征匹配点进行临时三角化

状态更新:更新这些帧的运动状态

约束构建:通过体素地图筛选的合适地图点(suitable map points)及其在滑动窗口中的跨帧特征匹配构建约束

全局优化:进一步更新滑动窗口内所有帧的状态,并优化选定地图点的全局3D坐标

状态更新完成后,当前帧的新特征点会被三角化并注册到体素地图中。关键帧判定依据当前帧与上一关键帧的视差决定,随后执行边缘化操作。最终,系统会利用当前立体图像的特征匹配点索引体素地图中最近访问的体素单元,将其包含的地图点标记为合适地图点,供下一次状态更新时使用。

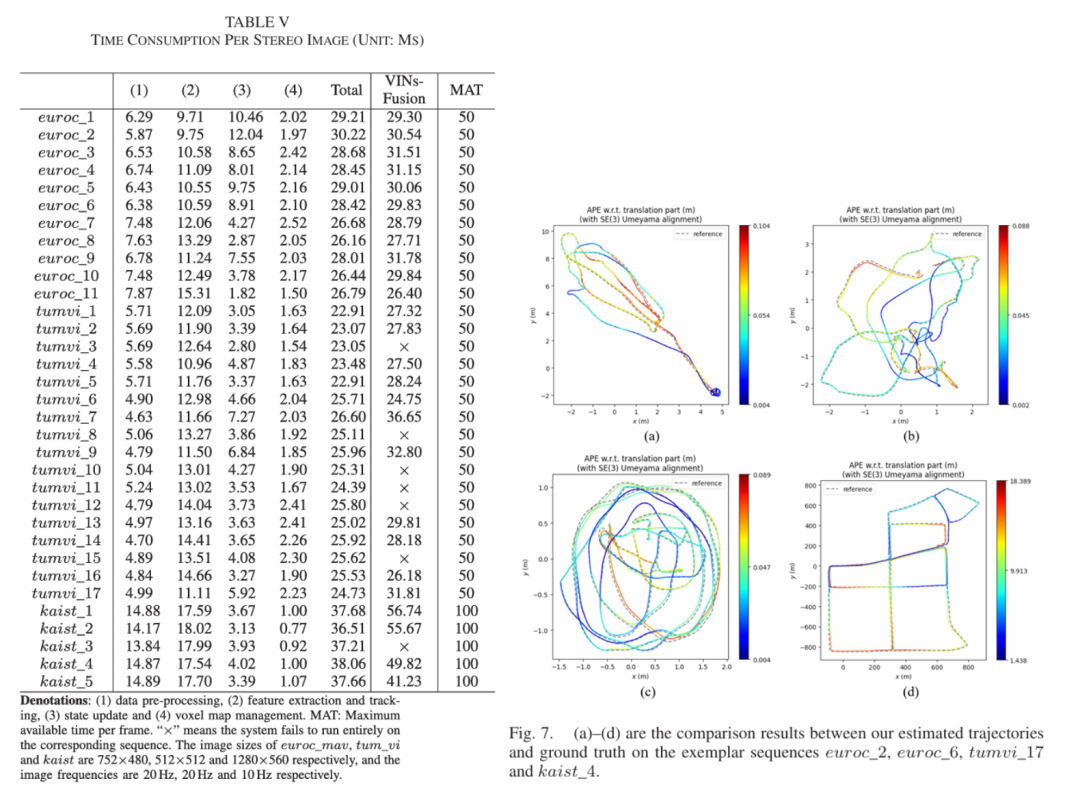

实验效果

总结

Voxel-SVIO提出将体素地图管理方法引入视觉-惯性里程计(VIO)领域,旨在高效筛选能与新帧建立约束的地图点并纳入状态估计器,从而实现计算资源的优化分配。实验表明,该系统在三个公开数据集(包括无人机,车载平台及手持)上达到了当前最优的精度水平,并实现了超越其他方法的鲁棒性。

参考文献

Yuan Z, Lang F, Deng J, et al. Voxel-SVIO: Stereo Visual-Inertial Odometry based on Voxel Map[J]. IEEE Robotics and Automation Letters, 2025.

【3D视觉之心】技术交流群

3D视觉之心是面向3D视觉感知方向相关的交流社区,由业内顶尖的3D视觉团队创办!聚焦三维重建、Nerf、点云处理、视觉SLAM、激光SLAM、多传感器标定、多传感器融合、深度估计、摄影几何、求职交流等方向。扫码添加小助理微信邀请入群,备注:学校/公司+方向+昵称(快速入群方式)

扫码添加小助理进群

【具身智能之心】知识星球

具身智能之心知识星球是国内首个具身智能开发者社区,也是最专业最大的交流平台,近1500人。主要关注具身智能相关的数据集、开源项目、具身仿真平台、VLA、VLN、Diffusion Policy、强化学习、具身智能感知定位、机器臂抓取、姿态估计、策略学习、轮式+机械臂、双足机器人、四足机器人、大模型部署、端到端、规划控制等方向。星球内部为大家汇总了近40+开源项目、近60+具身智能相关数据集、行业主流具身仿真平台、各类学习路线等,涉及当前具身所有主流方向。

扫码加入星球,享受以下专有服务:

1. 第一时间掌握具身智能相关的学术进展、工业落地应用;

2. 和行业大佬一起交流工作与求职相关的问题;

3. 优良的学习交流环境,能结识更多同行业的伙伴;

4. 具身智能相关工作岗位推荐,第一时间对接企业;

5. 行业机会挖掘,投资与项目对接;

2139

2139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?