目录

一、要求:

利用Altera公司的FPGA开发软件Quartus 13.1采用混合设计实现方波信号频率和占空比测量。

二、指标要求

1) 待测方波信号频率范围1Hz~1MHz,测量精度优于0.1Hz

2) 待测方波信号占空比范围1%~95%,测量精度优于1%

3) 频率数据显示精度0.1Hz,给出8位数字的BCD码结果

4) 占空比给出2位整数百分比的BCD码结果

三、 等精度测频设计原理

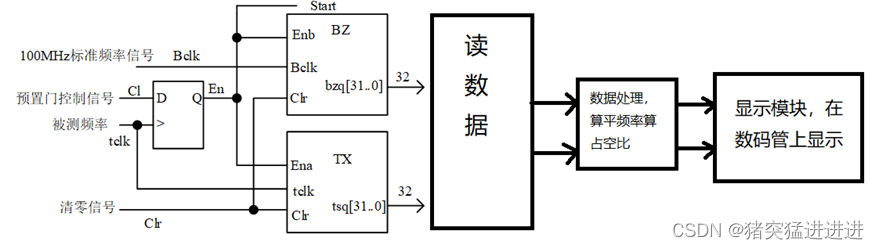

设计原理流程图如图 1:

图 1设计原理流程图

将在相同时间内对被测信号和标准信号同时计数 ,D触发器保证实际闸门时间与被测信号同步,消除被测信号计数误差;读数据模块两个技术模块数据同时读入送进数据处理模块处理;数据处理模块将读入的数据计算出频率与占空比后送入显示模块;显示模块将频率与占空比显示在数码管上。

等精度测频率原理:

等精度测频法本质上是多周期同步测频,它是在直接测频基础上发展起来的,在目前的测频系统中得到了越来越广泛的应用。等精度测频时,同时对标准信号和待测信号计数,而且实际闸门时间不是固定的,而是被测信号的整数倍,即与被测信号保持同步,因此消除了对被测信号计数所产生的士1个数字误差,使测量精度大为提高。

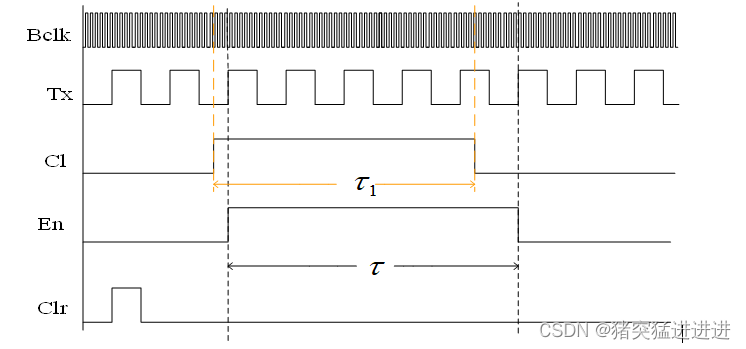

四、时序分析:

如图 2所示,Tx待测型号在Cl的预置闸门信号期间进行采样计数,使得在En为高时Tx总是整数倍出现。

图 2时序分析图

设在一次实际闸门时间τ中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。标准信号的频率为fs,则被测信号的频率为:

fx=(Nx/Ns)·fs (1)

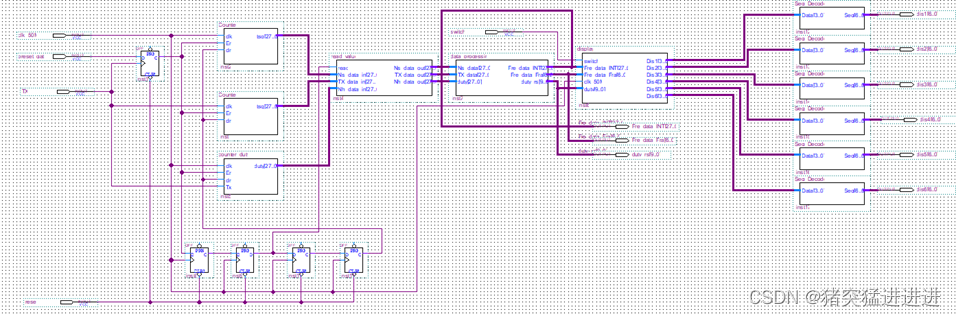

五、模块设计

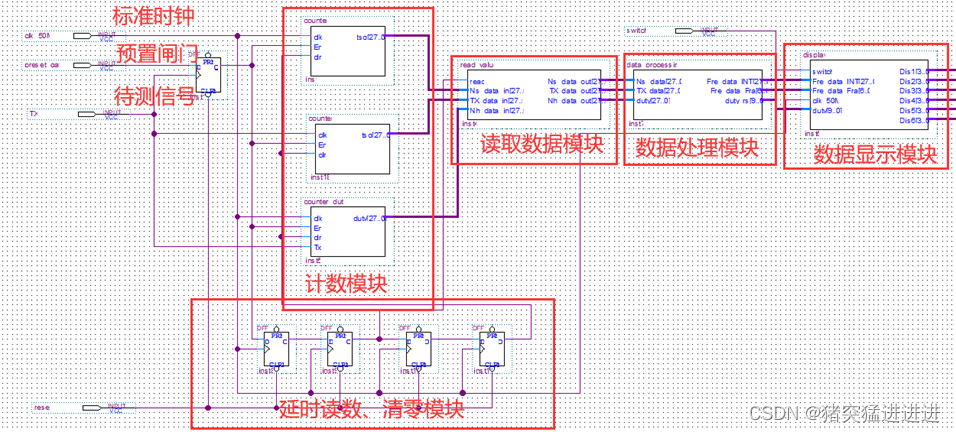

如图 3所示,计数器模块同时计数频率Ns、Nx值与占空比Nh值,数值传给数据处理模块,由数据模块switch信号切换显示数据的不同位,数值传给数码管显示模块显示。

由一个D触发器实现预置闸门与待测信号的同步,触发信号为Tx,后面四个D触发器为读信号和清零信号延时,由50Mhz标准信号触发,延时两个标准信号单元为Read信号,延时四个标准单元为clr信号;复位信号控制五个D触发器的使能信号。

图 3系统总体设计图

模块代码展示:

1、计数器

频率计数器:

module counter(clk,En,clr,tsq);

input clk,clr,En;

output reg [27:0]tsq;

always@(posedge clk or negedge clr)

begin

if(!clr)

begin

tsq<=28'b0;

end

else

begin

if(En)

begin

tsq<=tsq+1;

end

end

end

endmodule

占空比计数器:

module counter_duty(clk,En,clr,Tx,duty,tsq);

input clk,clr,En,Tx;

output reg [27:0]duty;

output reg [27:0]tsq;

always@(posedge clk or negedge clr)

begin

if(!clr)

begin

duty<=28'b0;

tsq<=28'b0;

end

else

begin

tsq<=tsq+1;

if(En&Tx)

duty<=duty+1;//高电平数

end

end

endmodule

2、读数据

module read_value(read,Ns_data_in,Ns_data_out,TX_data_in,TX_data_out,Nh_data_in,Nh_data_out);

input read;

input [27:0] Ns_data_in,TX_data_in,Nh_data_in;

output reg [27:0] Ns_data_out,TX_data_out,Nh_data_out;

always@(negedge read)

begin

TX_data_out<= TX_data_in;

Ns_data_out<=Ns_data_in+28'd4;

Nh_data_out<=Nh_data_in+28'd4;

end

endmodule

3、数据处理

module data_processing(Ns_data,TX_data,Fre_data_INT,Fre_data_Fra,duty,duty_rs);

input [27:0] Ns_data,TX_data,duty;

reg [55:0] temp;

reg [27:0] remainder;

output reg [9:0]duty_rs; //占空比

output reg [27:0] Fre_data_INT; // 频率整数部分

output reg [6:0] Fre_data_Fra; // 频率小数部分

always@(Ns_data,TX_data)

begin

temp = 50_000_000*TX_data;

Fre_data_INT = temp/Ns_data;

remainder = temp%Ns_data;

Fre_data_Fra= remainder*100/Ns_data; // 保留2位小数

duty_rs =(duty*1000)/Ns_data;

end

endmodule

4、数码管显示模块

module display(switch,Fre_data_INT,Fre_data_Fra,clk_50M,duty,Dis1,Dis2,Dis3,Dis4,Dis5,Dis6);

input [27:0] Fre_data_INT;

input [6:0] Fre_data_Fra;

input [9:0] duty;

input switch;

input clk_50M;

output reg [3:0] Dis1;

output reg [3:0] Dis2;

output reg [3:0] Dis3;

output reg [3:0] Dis4;

output reg [3:0] Dis5;

output reg [3:0] Dis6;

reg [27:0] Ns_data;

always@(clk_50M)

begin

if(switch)//前六位

begin

Dis1[3:0]<= Fre_data_INT/1_000_000;

Dis2[3:0]<= (Fre_data_INT%1_000_000)/100000;

Dis3[3:0]<= (Fre_data_INT%100000)/10000;

Dis4[3:0]<= (Fre_data_INT%10000)/1000;

Dis5[3:0]<= (Fre_data_INT%1000)/100;

Dis6[3:0]<= (Fre_data_INT%100)/10;

end

else//后六位(其中最后三位为占空比数据)

begin

Dis1[3:0]<= Fre_data_INT%10;

Dis2[3:0]<= 0;

Dis3[3:0] <= Fre_data_Fra/10;

Dis4[3:0]<=duty/100;

Dis5[3:0]<=(duty%100)/10;

Dis6[3:0]<=duty%10;

end

end

endmodule

六、仿真分析

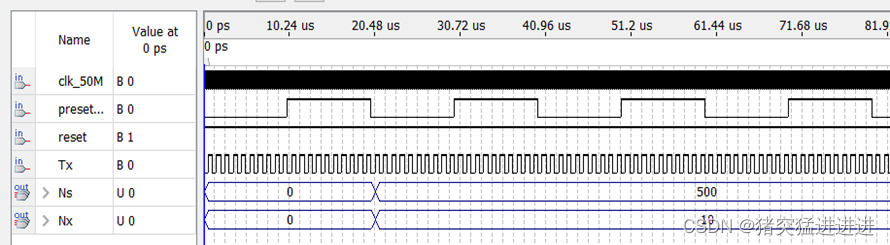

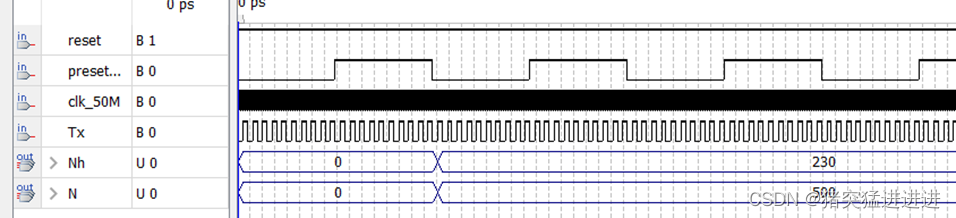

1、计数模块

在计数模块中Ns为标准信号个数,Nx为待测信号个数,Nh为高电平计数个数,tsq为频率值,duty为占空比值。

计算公式tsq = 50_000_000*Nx/Ns; duty=Nh/Ns;用quartus自带仿真,仿高频信号。

A、测量1Mhz频率占空比为50%的信号的频率。

设置Tx为1Mhz,预置闸门preset_gate周期为20us,clk_50M为标准50Mhz,reset为使能信号,始终为高。

理论测得tsq=500。

实际仿真测得tsq=496,由于clr信号延时四个标准信号周期,所以tsq=500-4,后期数据处理模块会将Ns补4,符合理论结果,如图 4所示。

图 4计数器模块频率计数仿真图

图 4计数器模块频率计数仿真图

B、Em设置为1Mhz,占空比为46%的信号的占空比

理论测得Nh=230,Ns=500,duty计算得460(乘以1000后的结果,以便显示)实际仿真测得duty=460,Nh补4后符合理论结果(原因同上),如图 5所示。

图 5计数器模块占空比计数仿真图

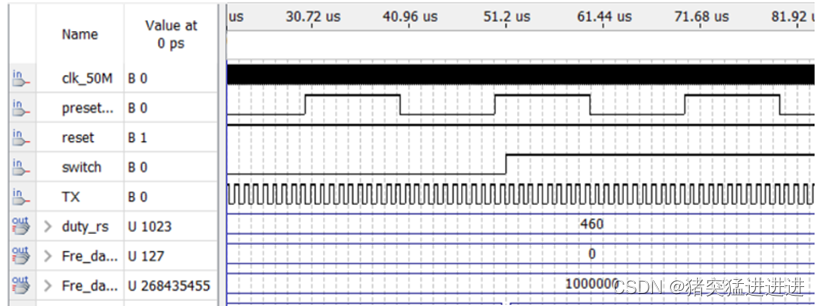

2、数据处理模块

Duty_rs为占空比值*1000,Fre_data_INT为频率整数值,Fre_data_Fra为频率小数值Read为读信号,switch为显示位输出转换开关。

仿真1MHz,占空比为46%的信号。

根据公式tsq = 50_000_000*Nx/Ns; duty=Nh/Ns。

理论测得Duty_rs=460,fre_data_INT=1000000,fre_data_Fra=0。

实际仿真测得Duty_rs=460,fre_data_INT=1000000,fre_data_Fra=0如图 6。

图 6数据处理模块仿真图

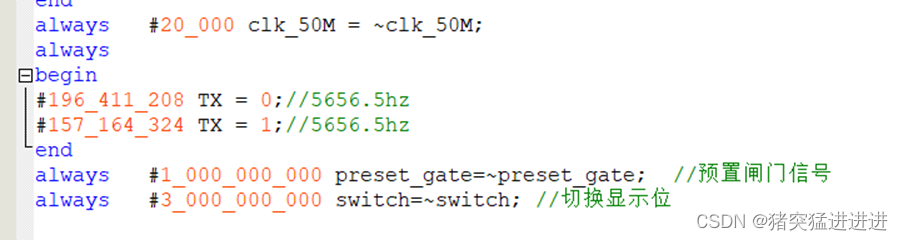

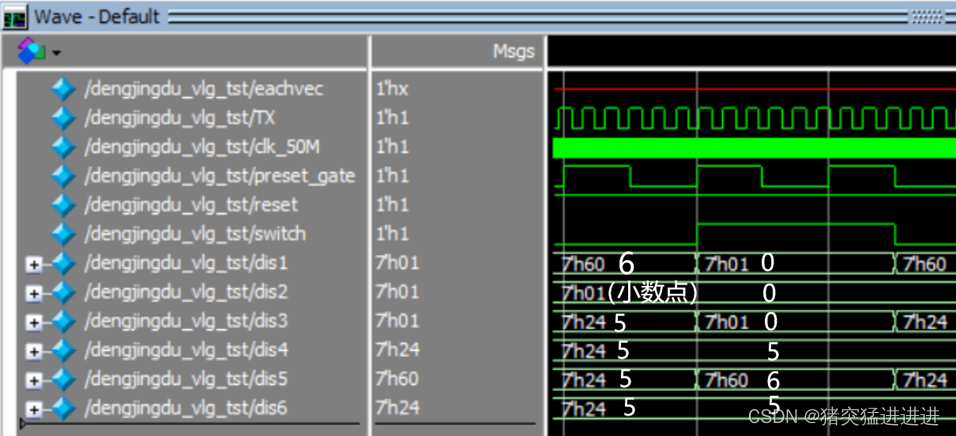

3、总体仿真

总体仿真电路图如图 7所示,随机选取了5656.5Hz占空比为55.5%的信号测试,仿真结果如下图所示。频率仿真得到fre =5656.5hz,占空比为55.5%符合题目设计要求。

图 7总体仿真电路图

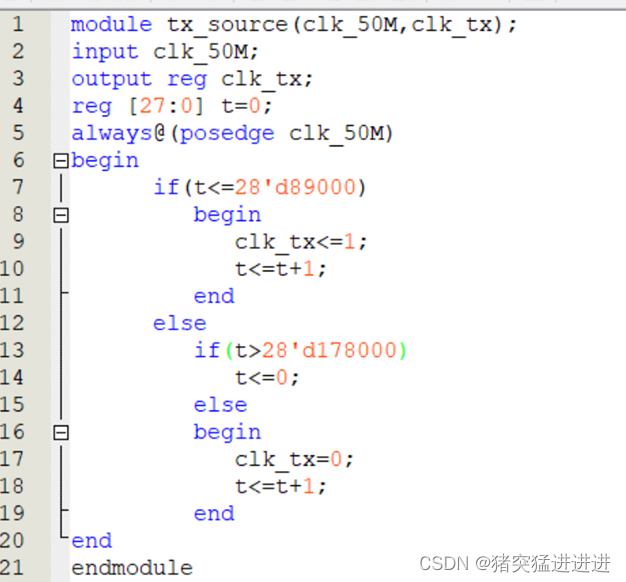

测试文件设置如图 8

单位1ps,精度1ps。

图 8测试文件图

图 9总体仿真测试图

Switch为1时输出频率高六位,为0时输出低一位和小数点后一位,以及用0代替小数点(此模块小数点没接管脚),和占空比(最后一位为小数后一位)。如上图9所示。

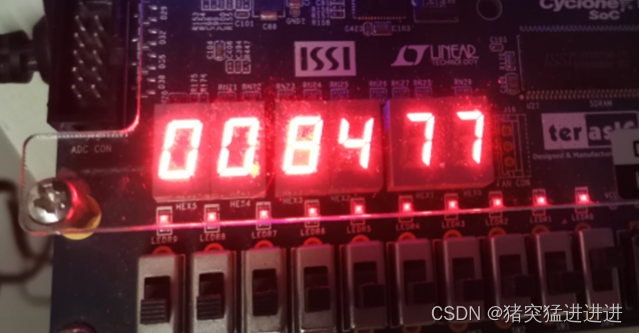

七、实测展示

用50Mhz分频的待测信号,测量280.8hz,占空比50%信号。(随机选择)

图 10生成待测信号分频器设计

图 11前六位显示

图 12后六位显示

如图 11前六为分别是频率的小数点前2至7位,如图 12第一位是频率的小数点前1位,第二位是用来当小数点的0(此块板子没有接小数点管脚),第三位是频率的小数点后一位,后三位用于表述占空比,其中最后一位是占空比小数点后一位;可见测得数据位,频率:280.8hz,占空比为50.0%。

将图 10中的第7行89000改为85000,可改变其占空比,理论计算得89000/178000=47.7%,实际测得也为47.7%,如下图所示。

图 13改变占空比后的后六位显示

八、说明

因为实际测量信号不是由信号发生器生成的标准信号,而是通过50Mhz分频产生而得, 根据实际测量结果可知,较高频的测量误差较大,其原因是因为其待测信号是由标准50Mhz分频而得,在生成较高频时由于 (数据处理+程序运行时间)/理论分频的周期 的比值较大,数据处理时间+程序运行时间使实际分频周期偏大,使得实际测得信号频率偏小,误差较大;待测频率越高误差越大。

如果使用信号发生器作为标准输入信号,误差应该符合题目需求,但是没有实测过。

641

641

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?