Vitis 入门指南

一. 安装环境准备

1.1 系统选择及安装建议(以下部分都是在ubuntu22.04环境下进行测试,vitis2024.1)

- 推荐系统:使用 Linux 系统进行开发,避免 Windows 环境下的长编译时间问题。

- 安装包选择:

- 安装 Vitis 时自动包含 Vivado;

- 若只安装 Vivado,Vitis 不会被安装;

- 根据需求选择设备支持包,避免安装全部而占用约 100GB 空间。

- Cable 驱动:Linux 系需手动安装硬件调试的 cable 驱动。

- 串口调试问题:

- 注意可能的驱动冲突(如 CH341);

- 出现问题时,可尝试卸载无关依赖或禁用一些冲突程序。

二. License 与工具配置

2.1 Xilinx 许可证管理

- 许可证申请与安装:

- 通过 Vivado License Manager 导入许可证。

- 网上自行寻找链接

三. Vivado 设计开发与vitis基本使用

3.1 项目创建与结构

- 创建新工程:

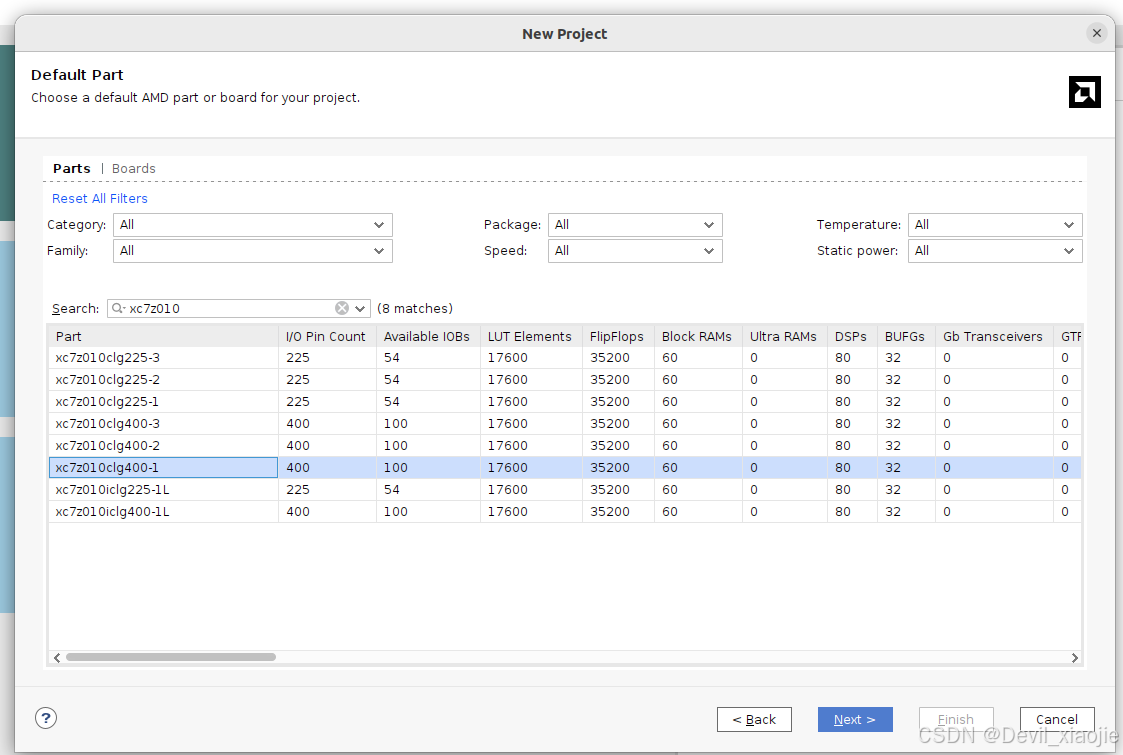

- 启动 Vivado,选择板卡和设备;

- 设置工程名和存储路径。

- 模块配置:

- 配置必要模块,如 Zynq-PS、DDR、PS_UART。(DDR用来做为系统运行的必要设备,UART可以方便用于串口调试)

以下内容参考正点原子启明星开发板第二期资料(我使用的是vitis2024.1,资料是2022.1,vivado操作方面无不同,vtis差别较大,可以参考一下不同的地方)

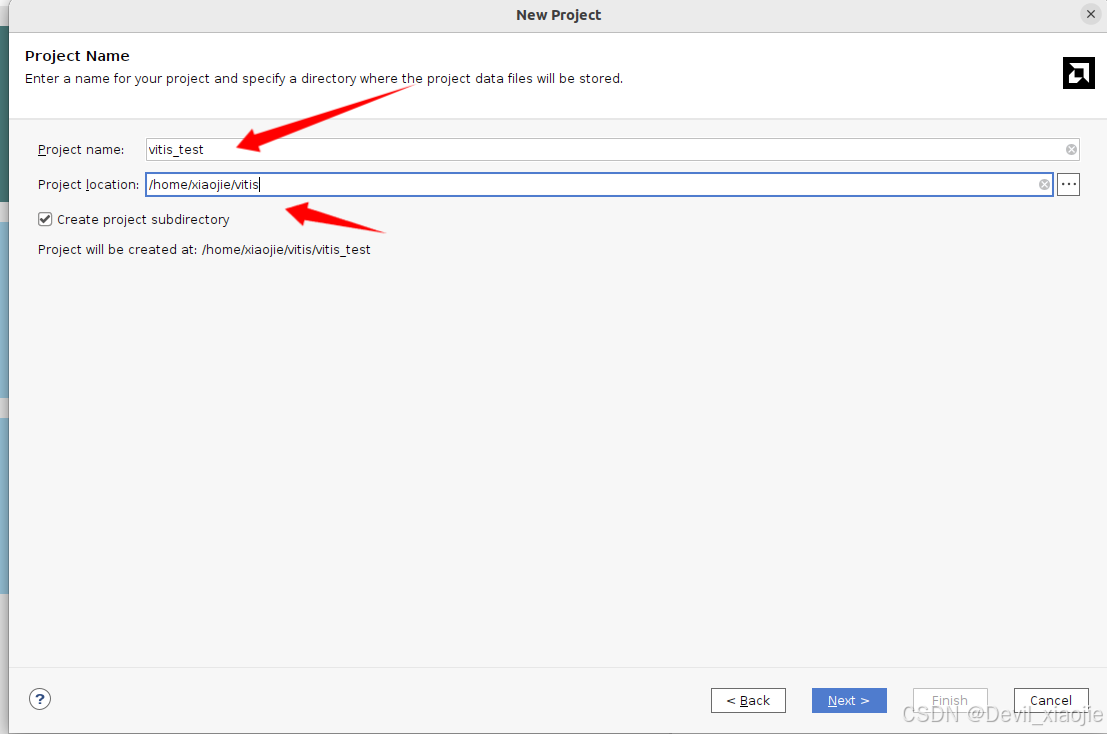

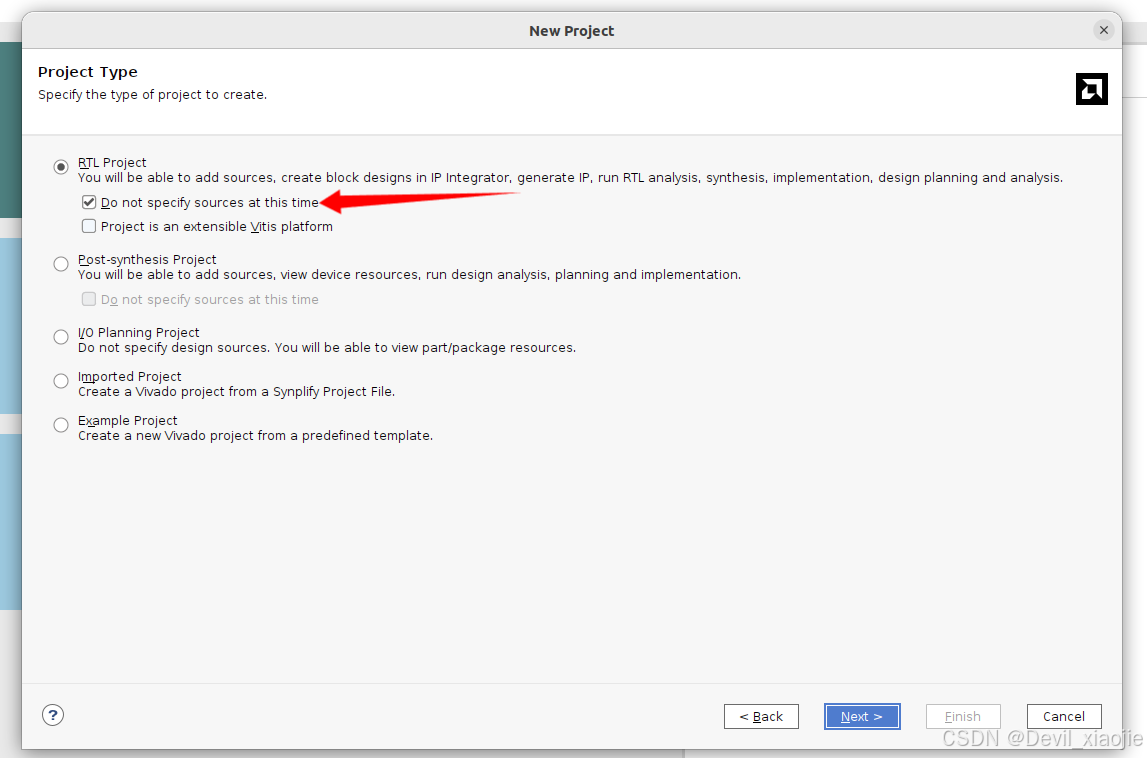

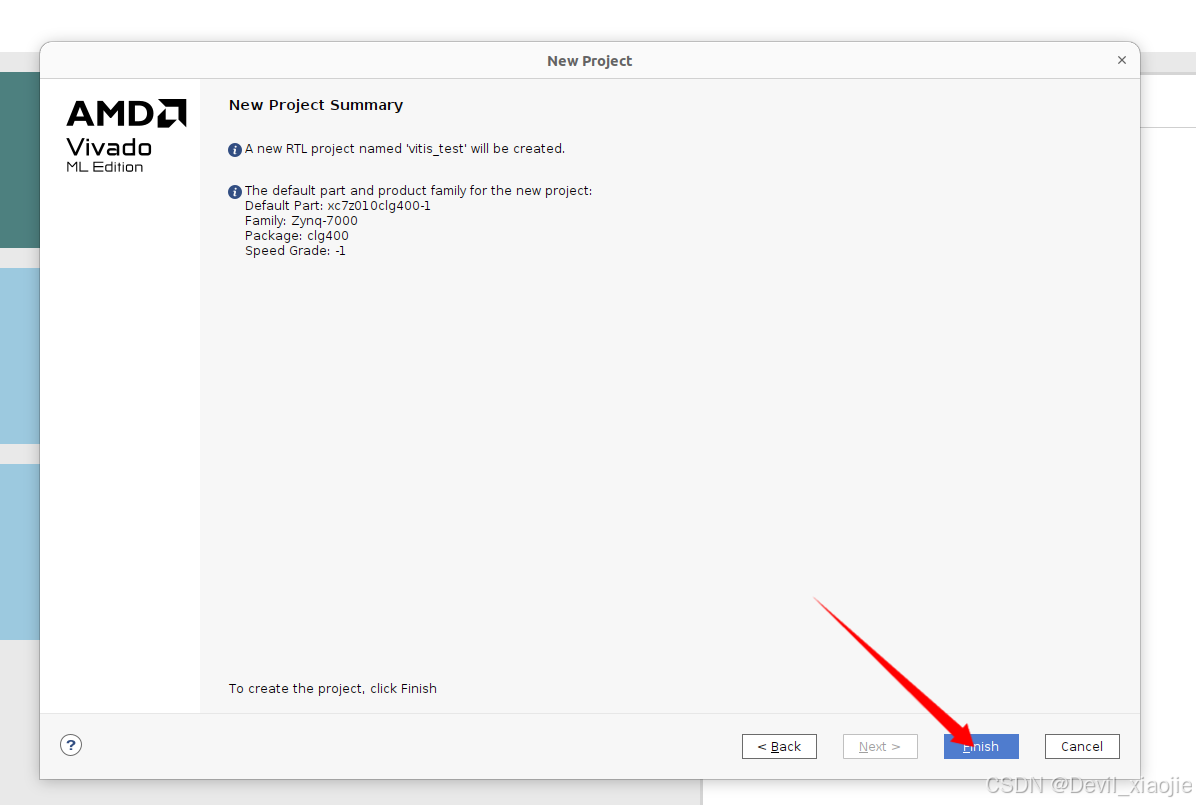

创建新工程

选择路径和名称

选择器件型号

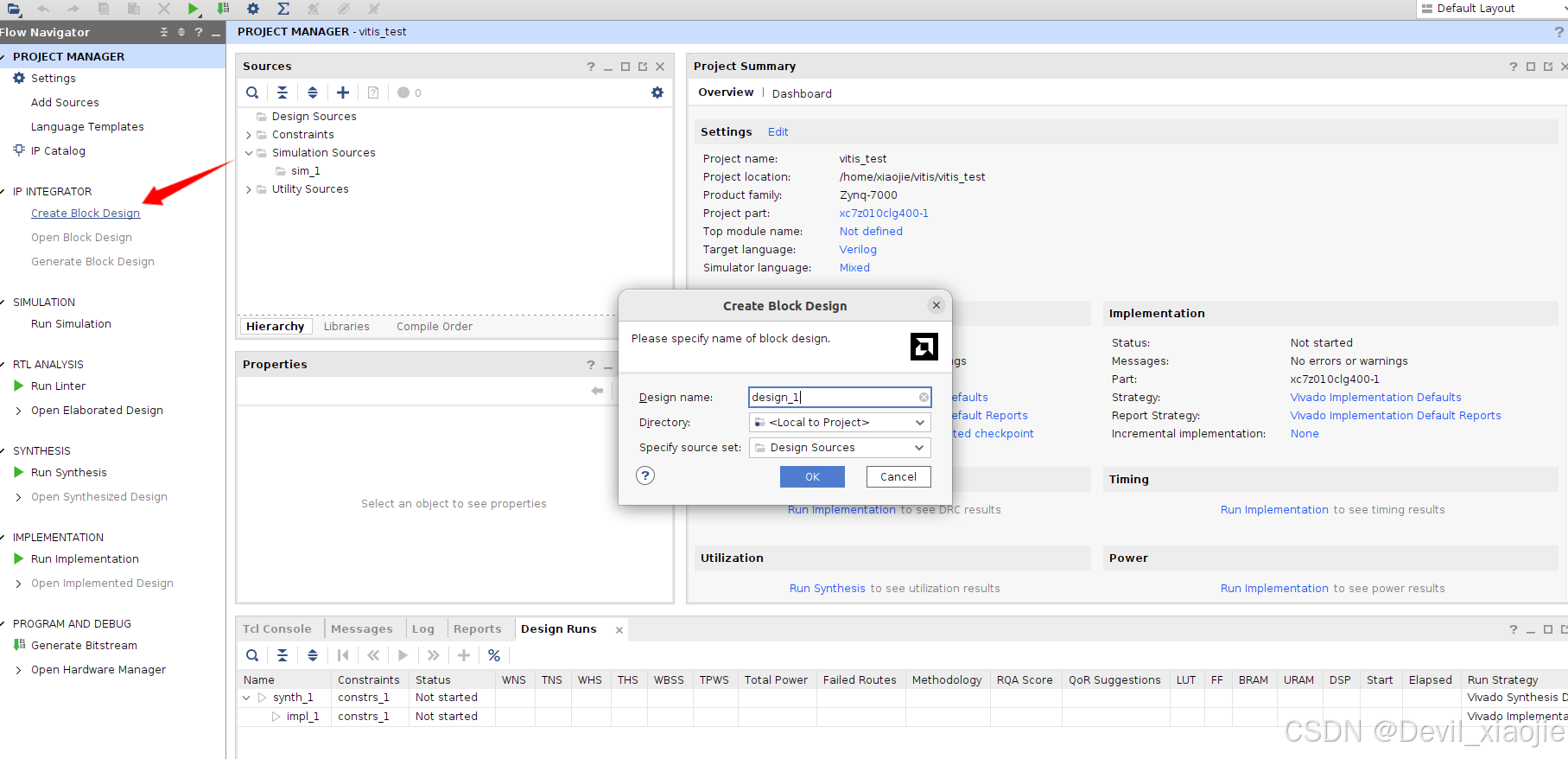

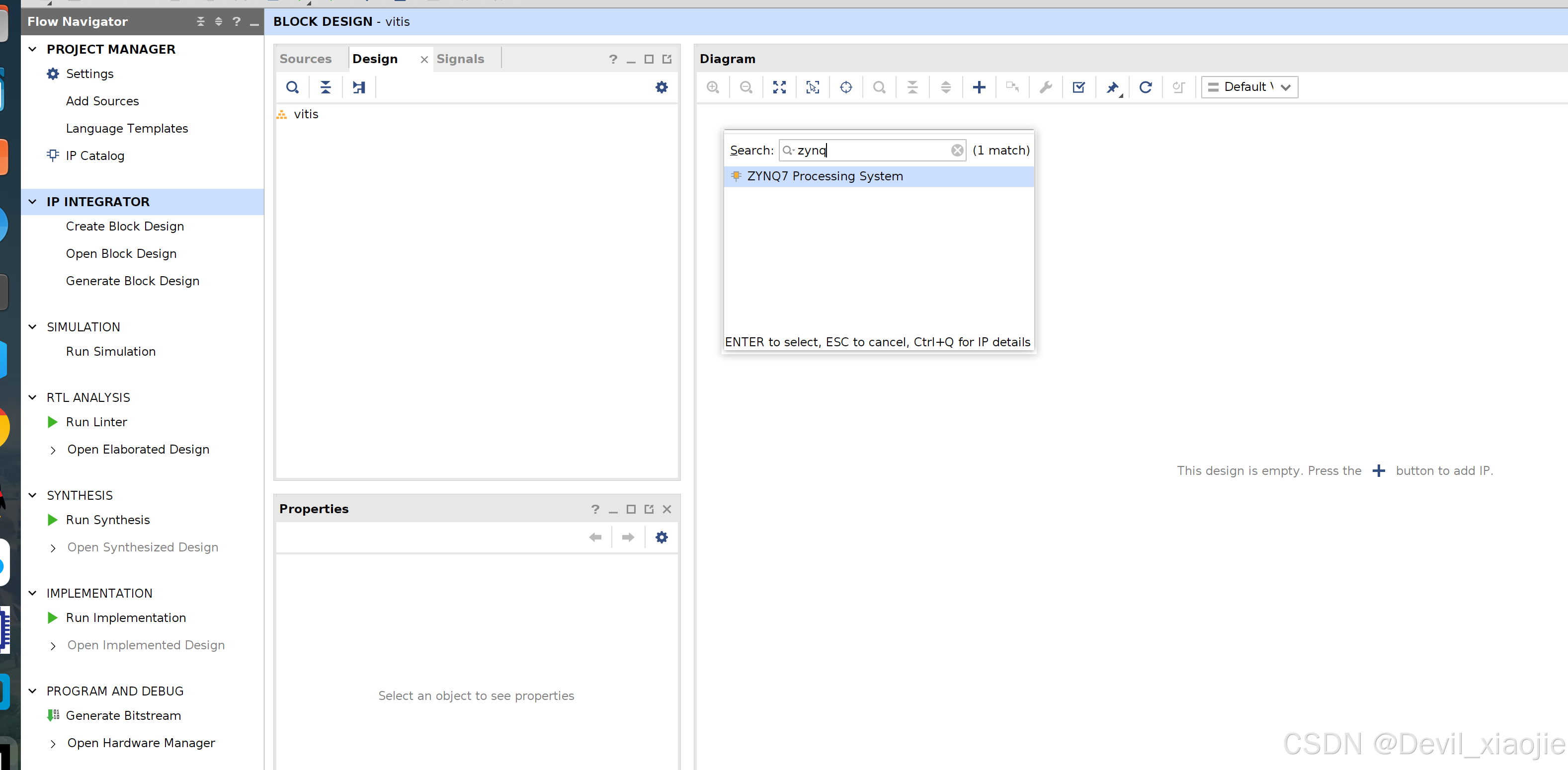

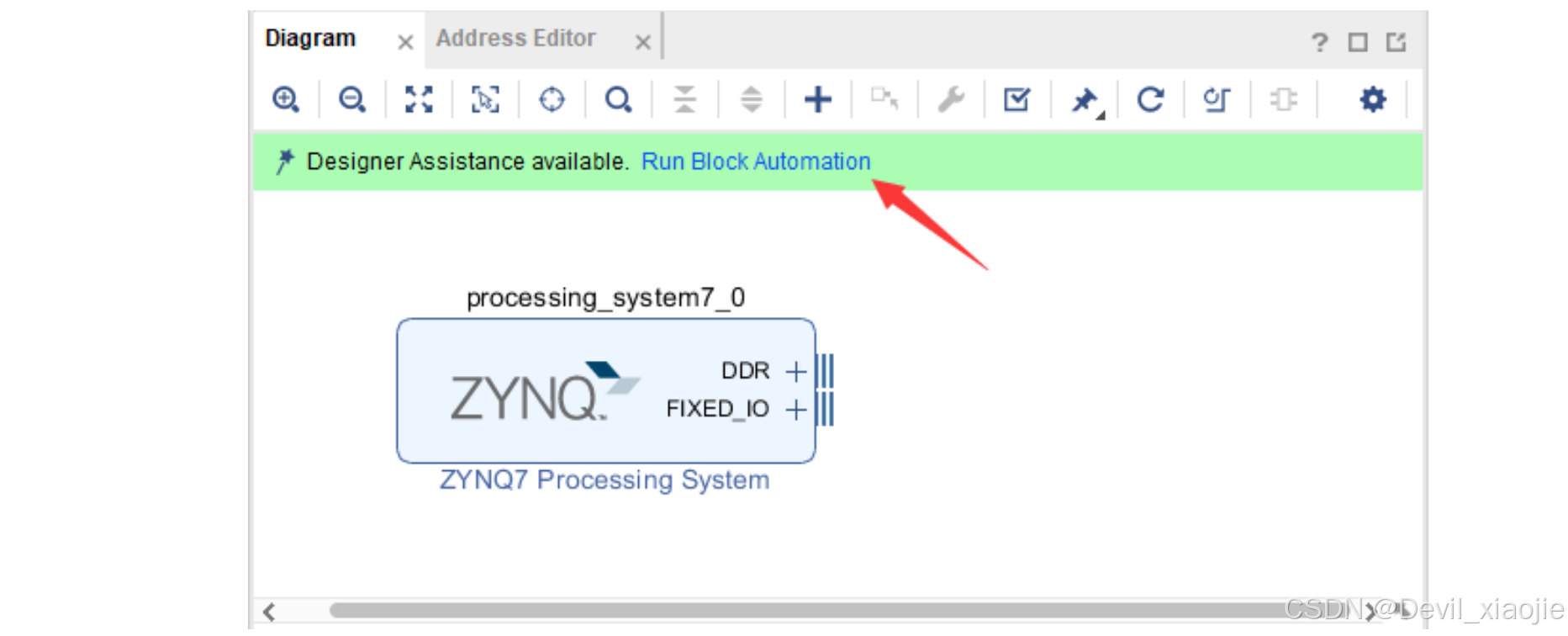

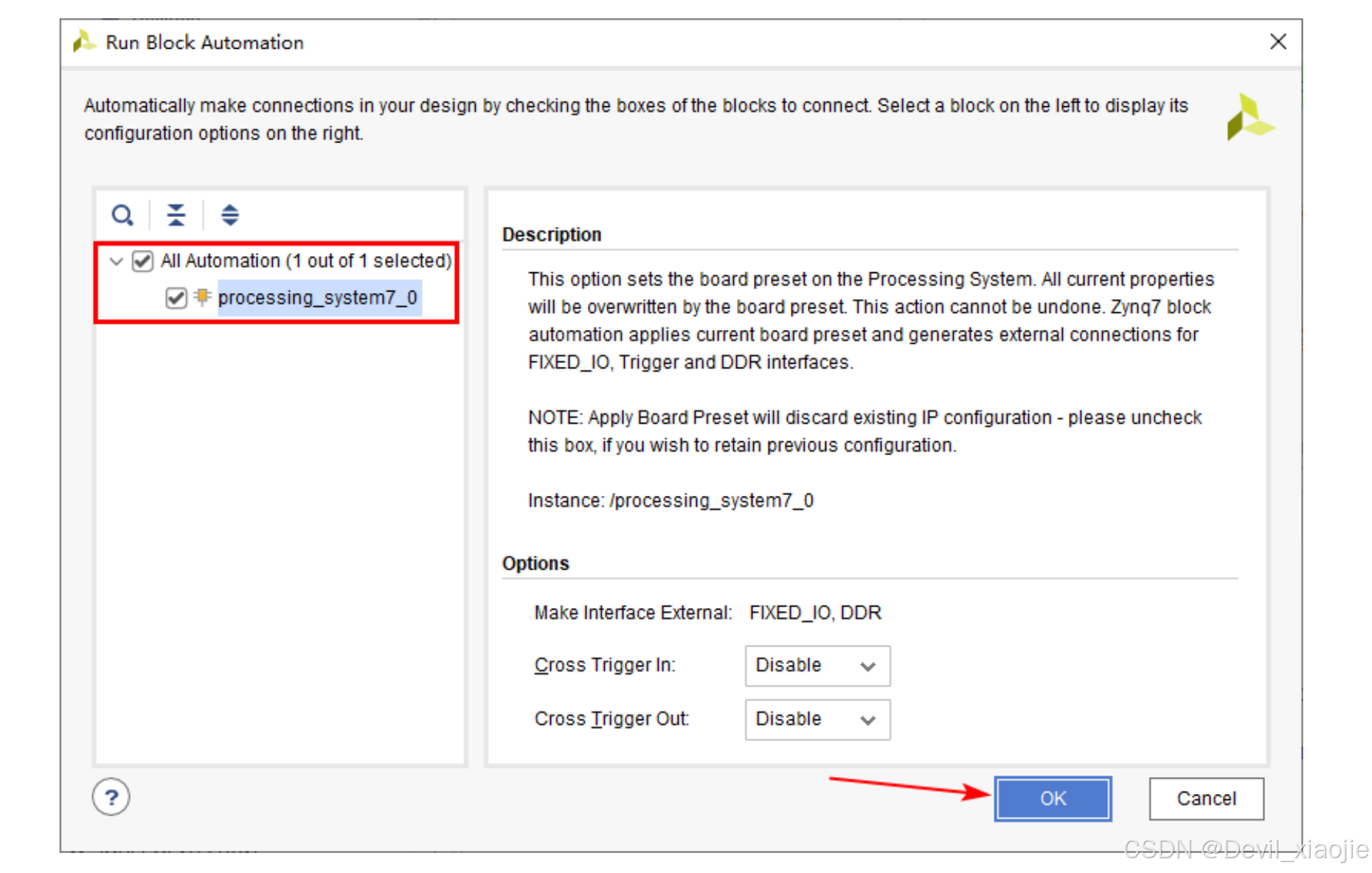

添加ps处理器

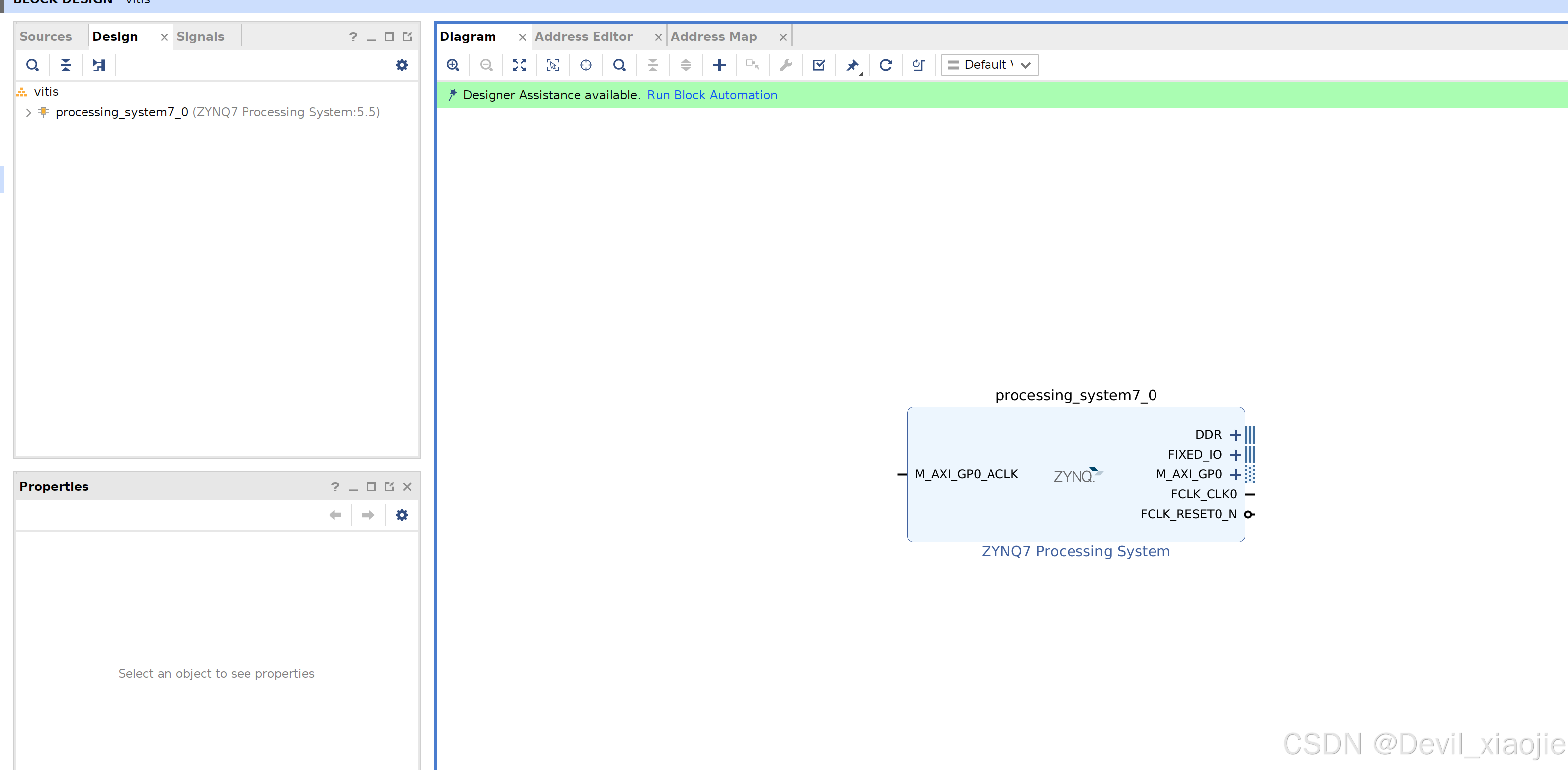

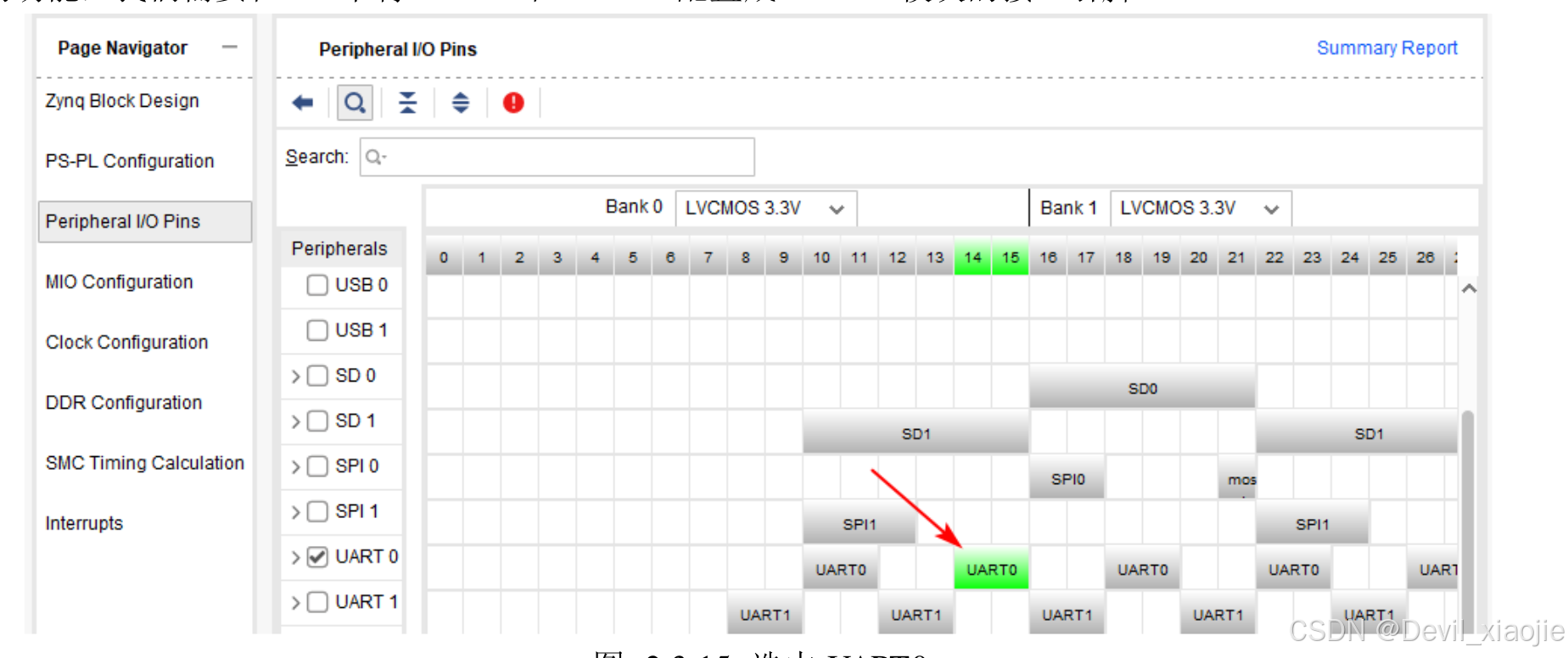

双击打开配置基础外设配置一个uart方便调试,配置ddr来作为处理器运行的必要内存组件。

选中uart,uart的参数可以保持默认即可,也可以自行修改。注意引脚要符合芯片手册以及跟板卡对应。

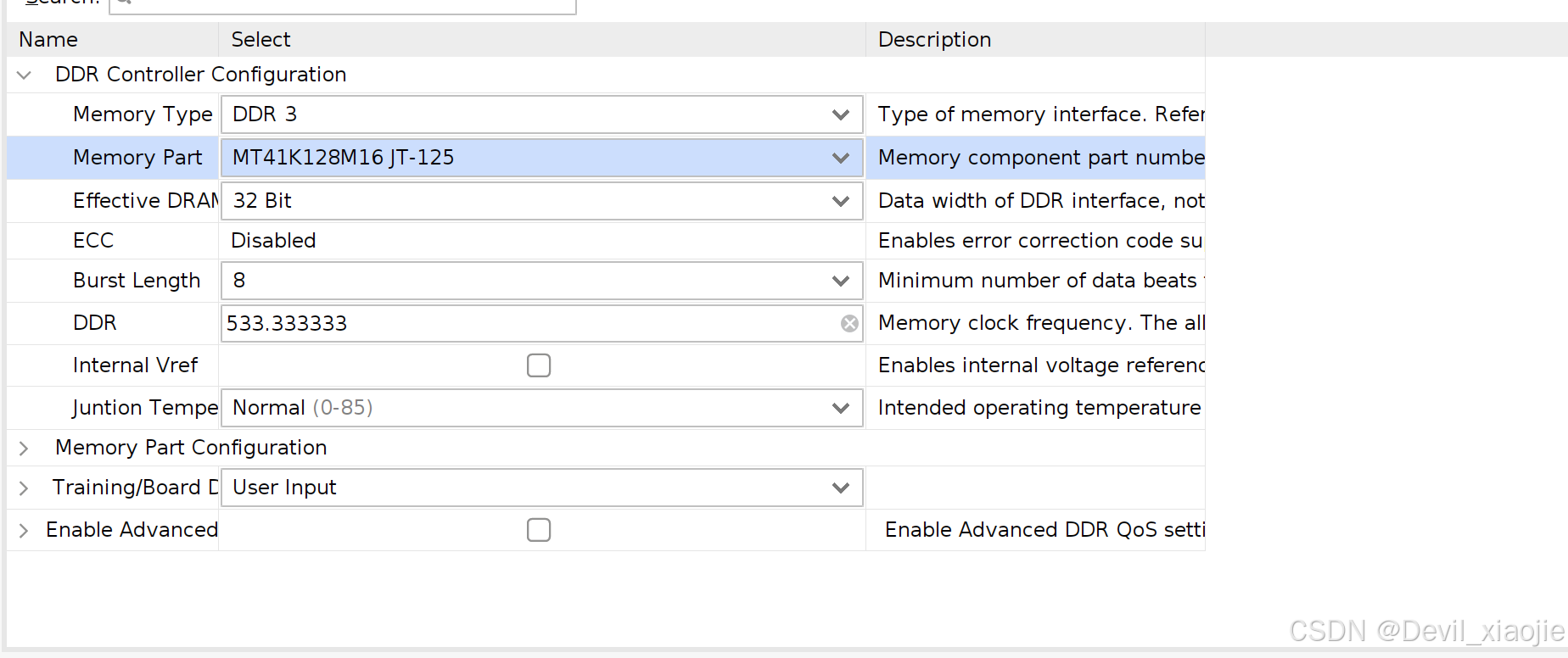

根据实际配置运行内存。

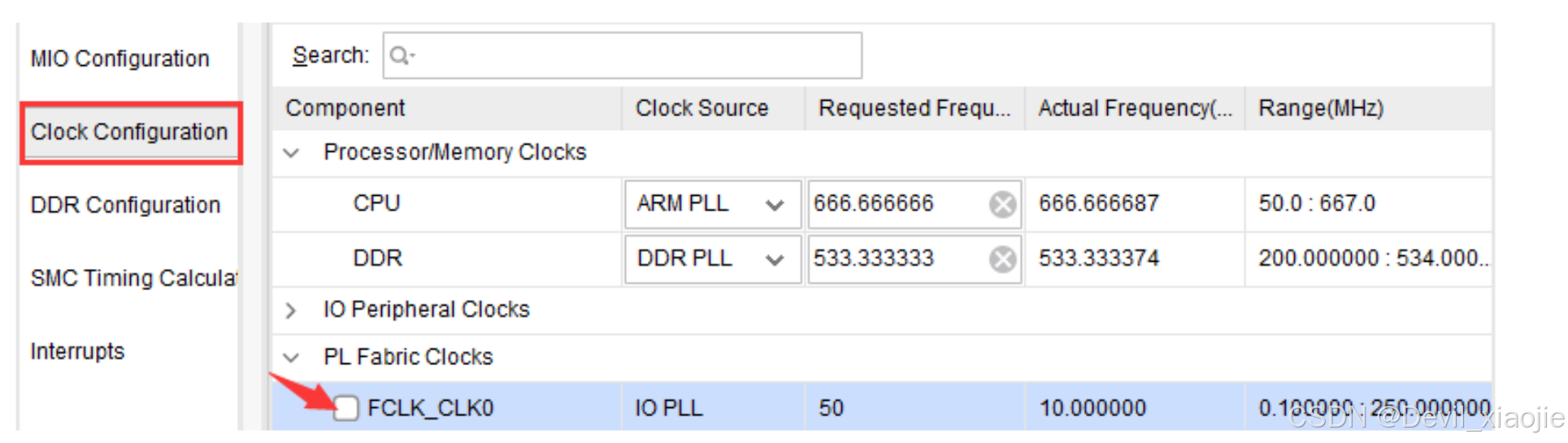

本实验未用到该时钟,取消勾选

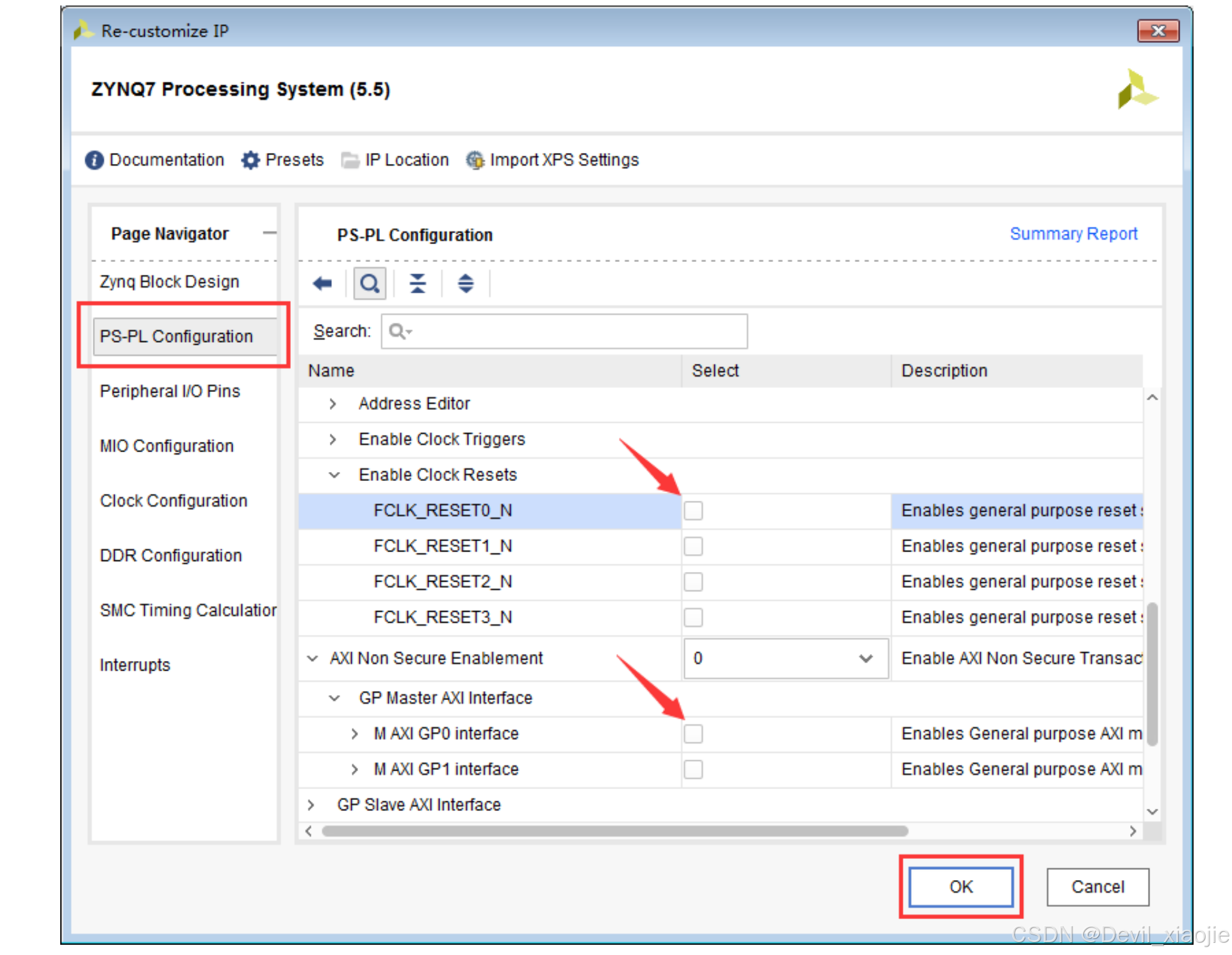

取消勾选 FCLK_RESET0_N 和 M AXI GP0 interface

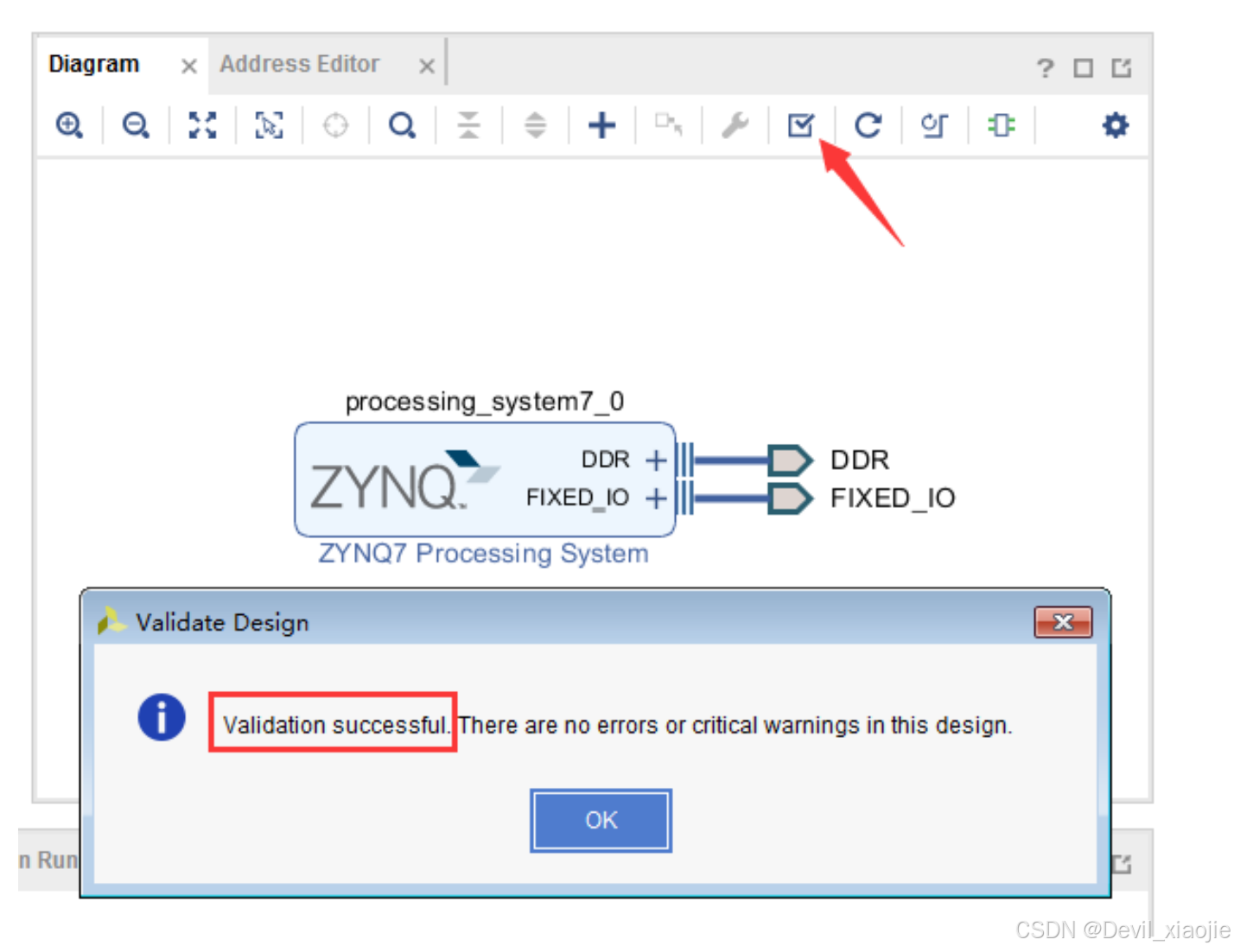

验证设计

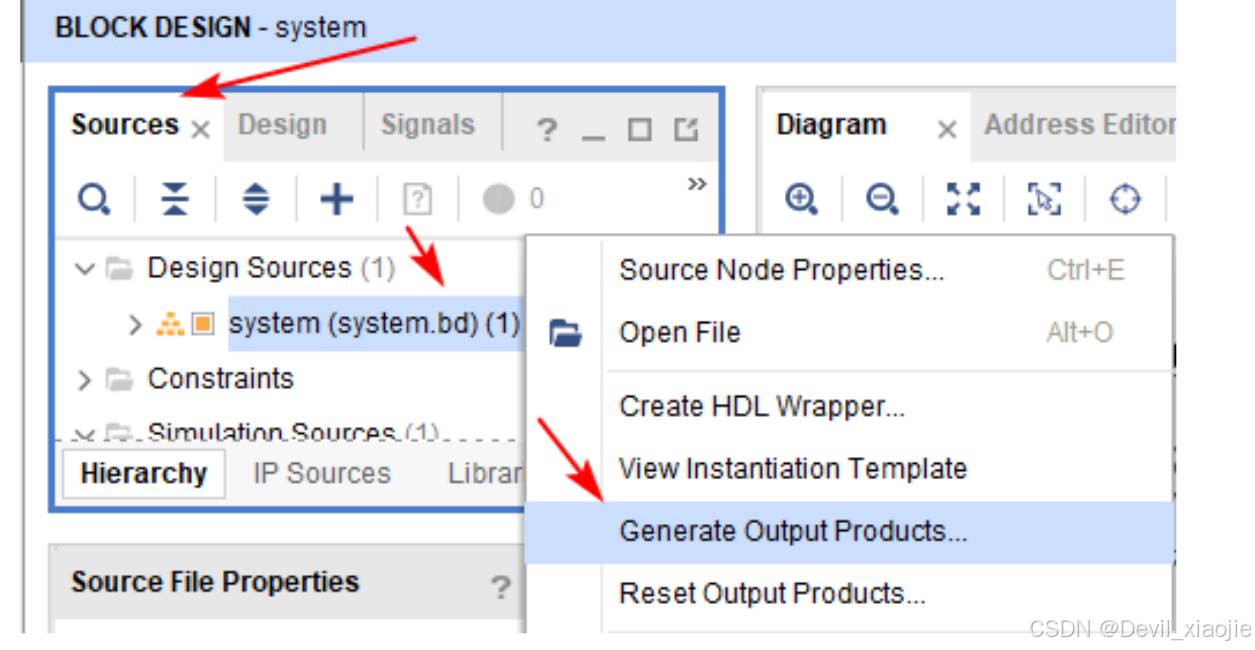

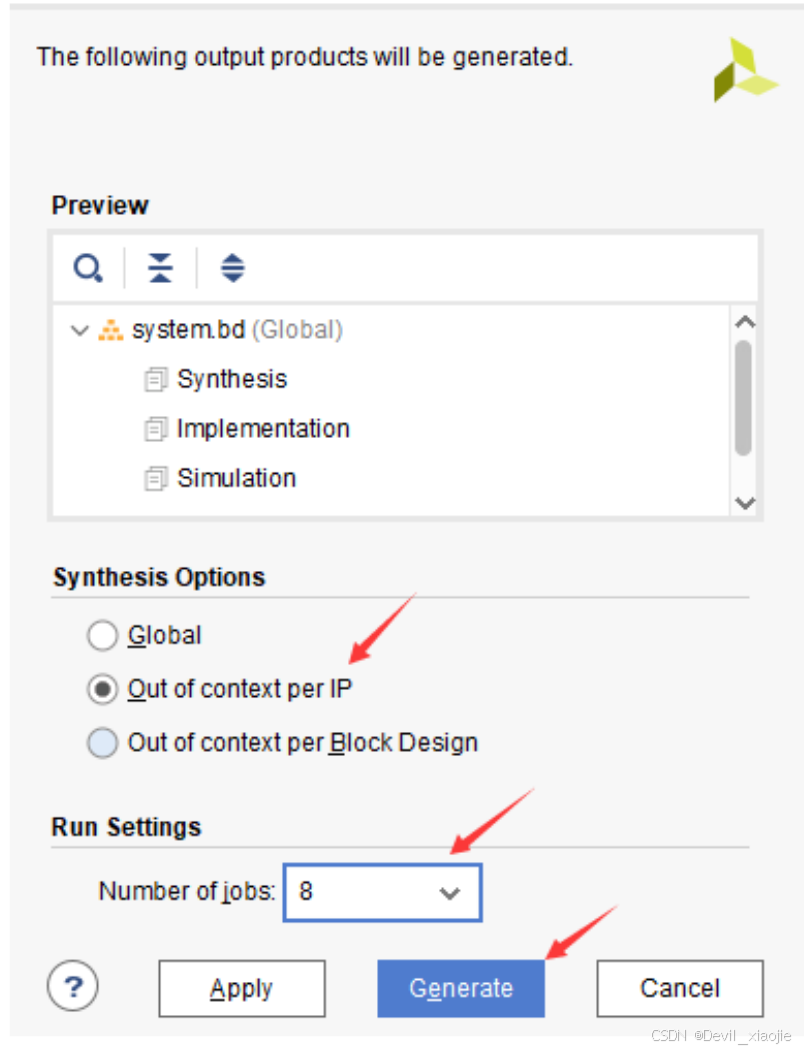

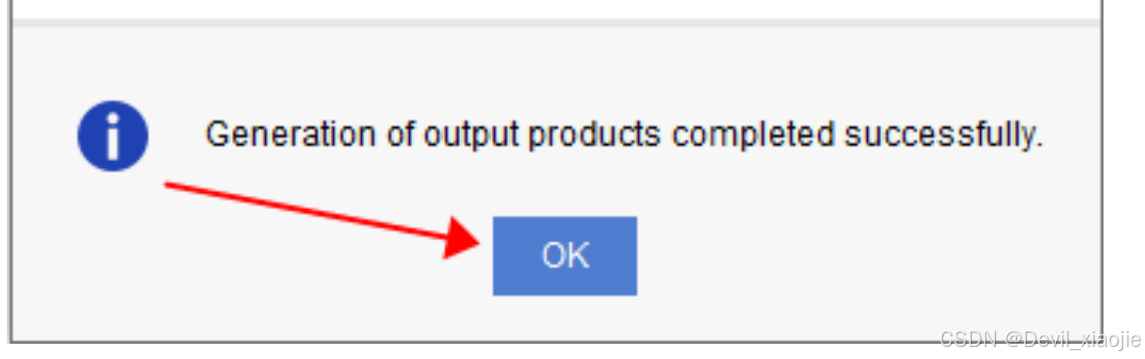

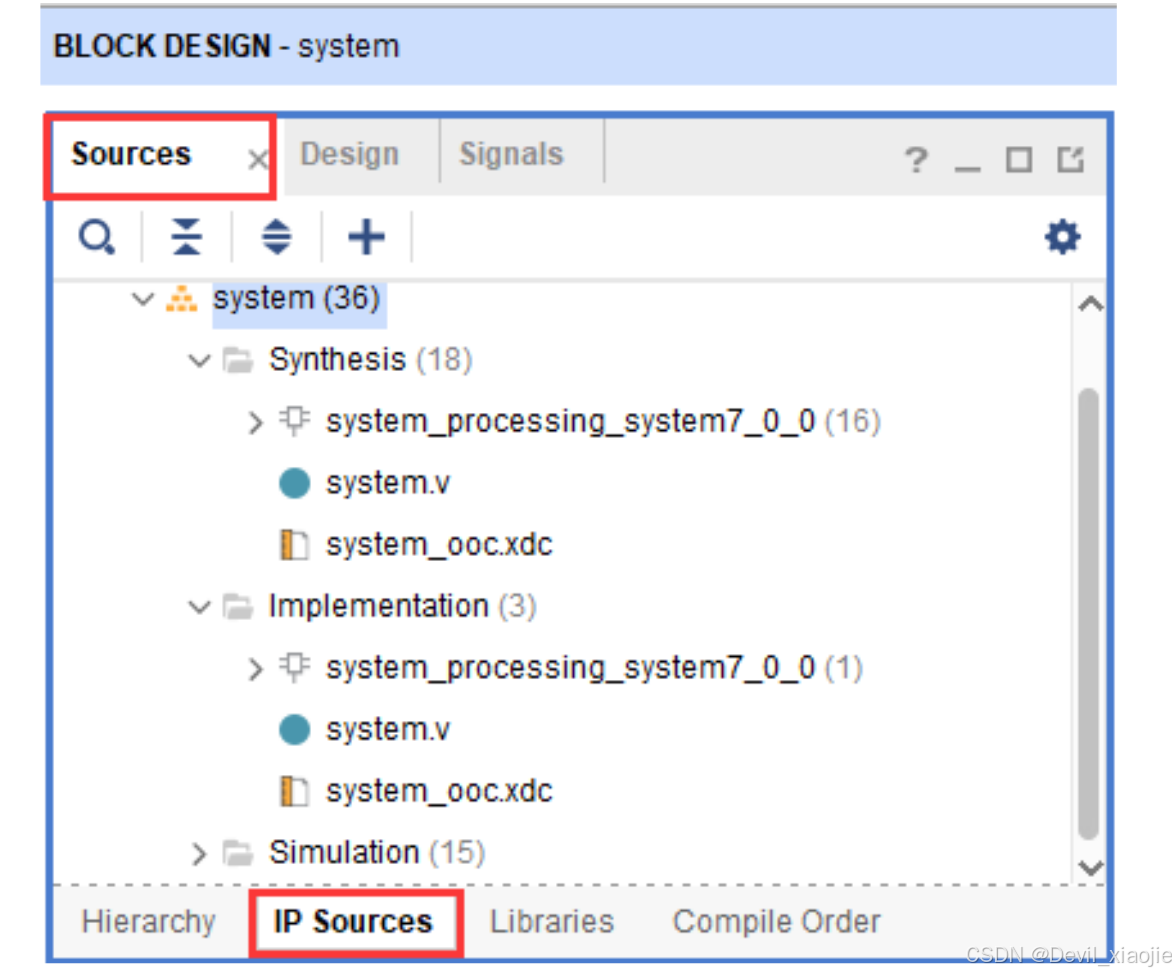

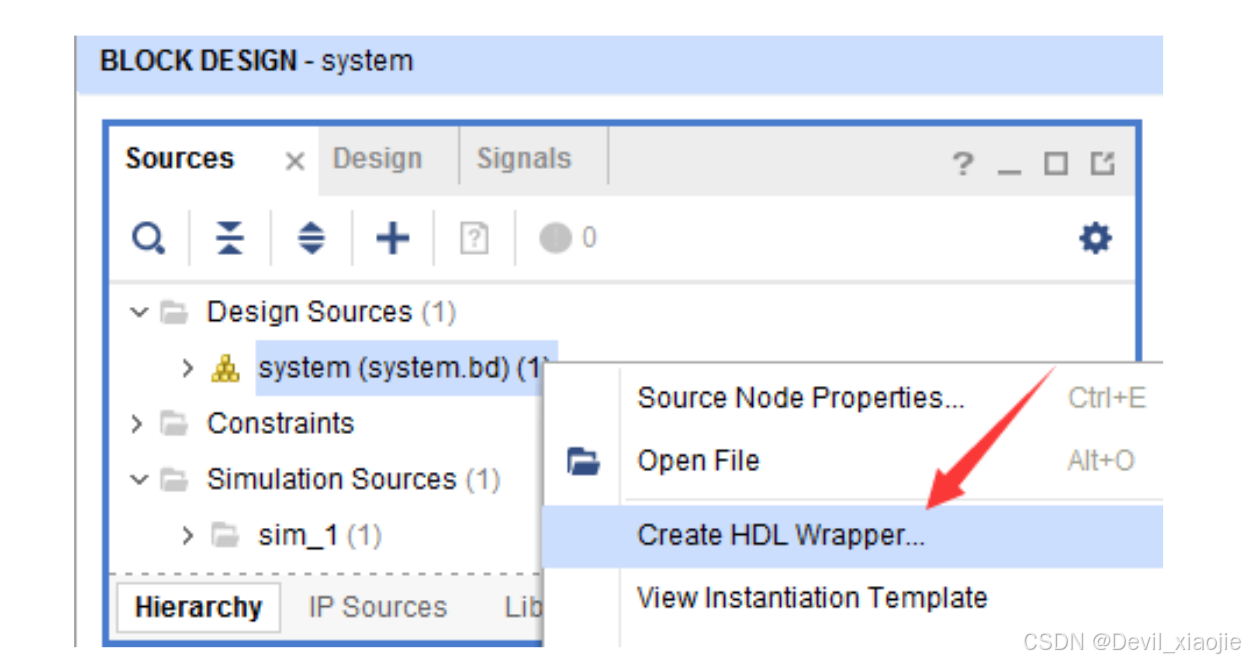

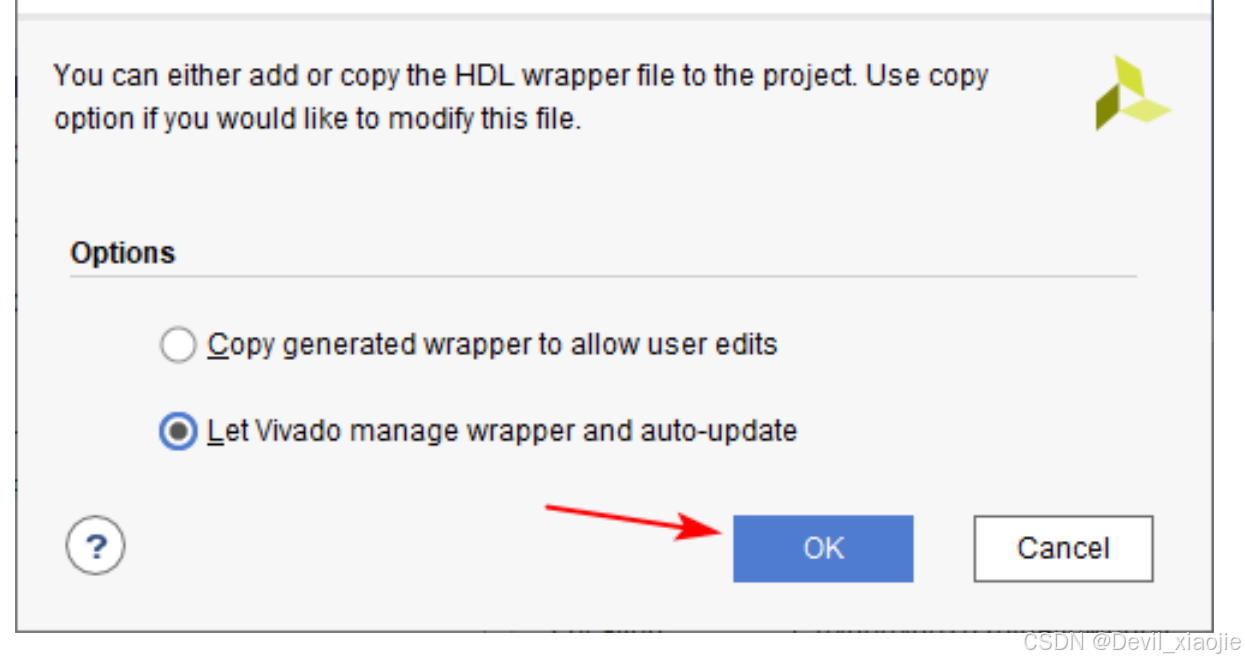

生成HDL

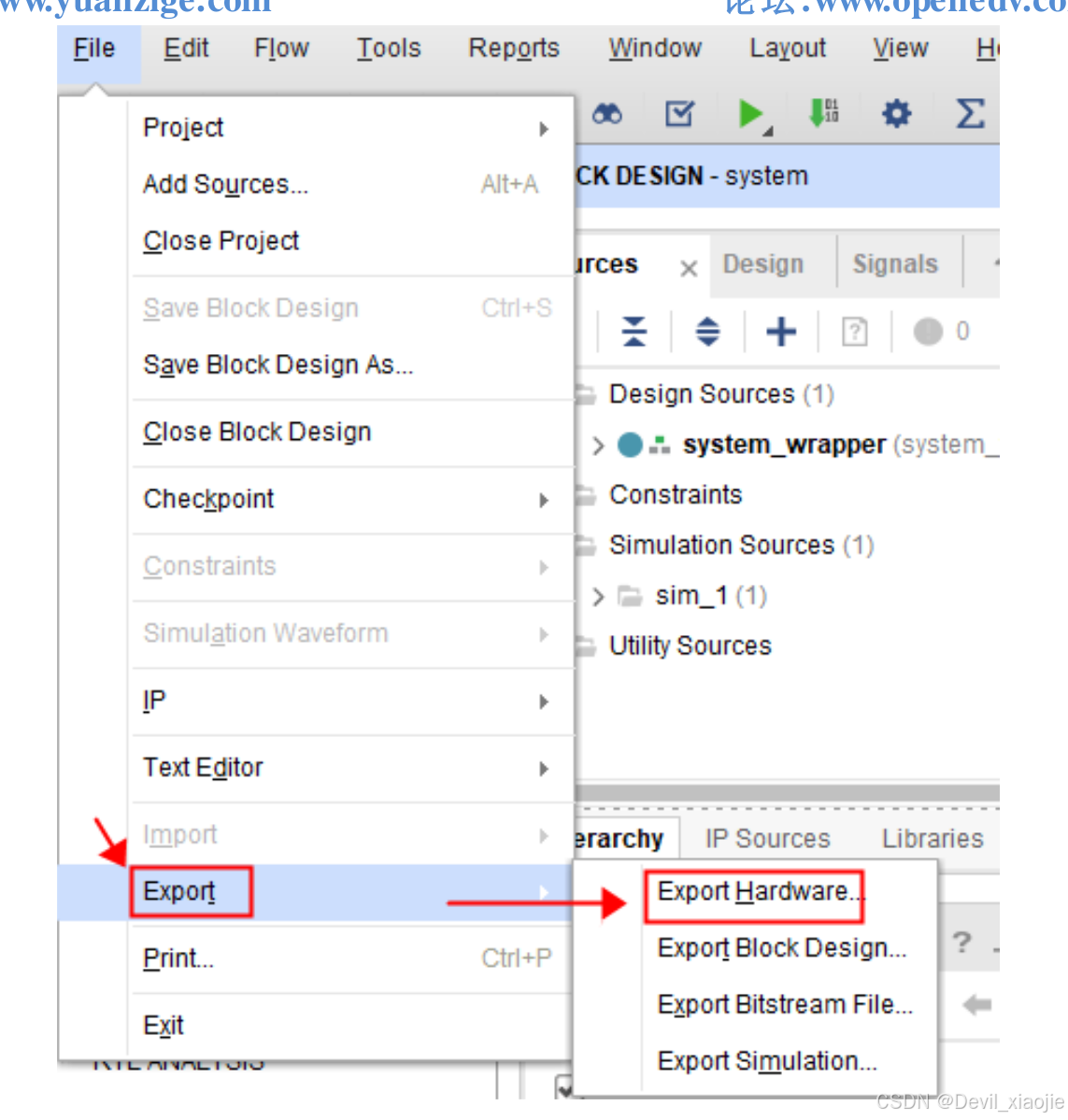

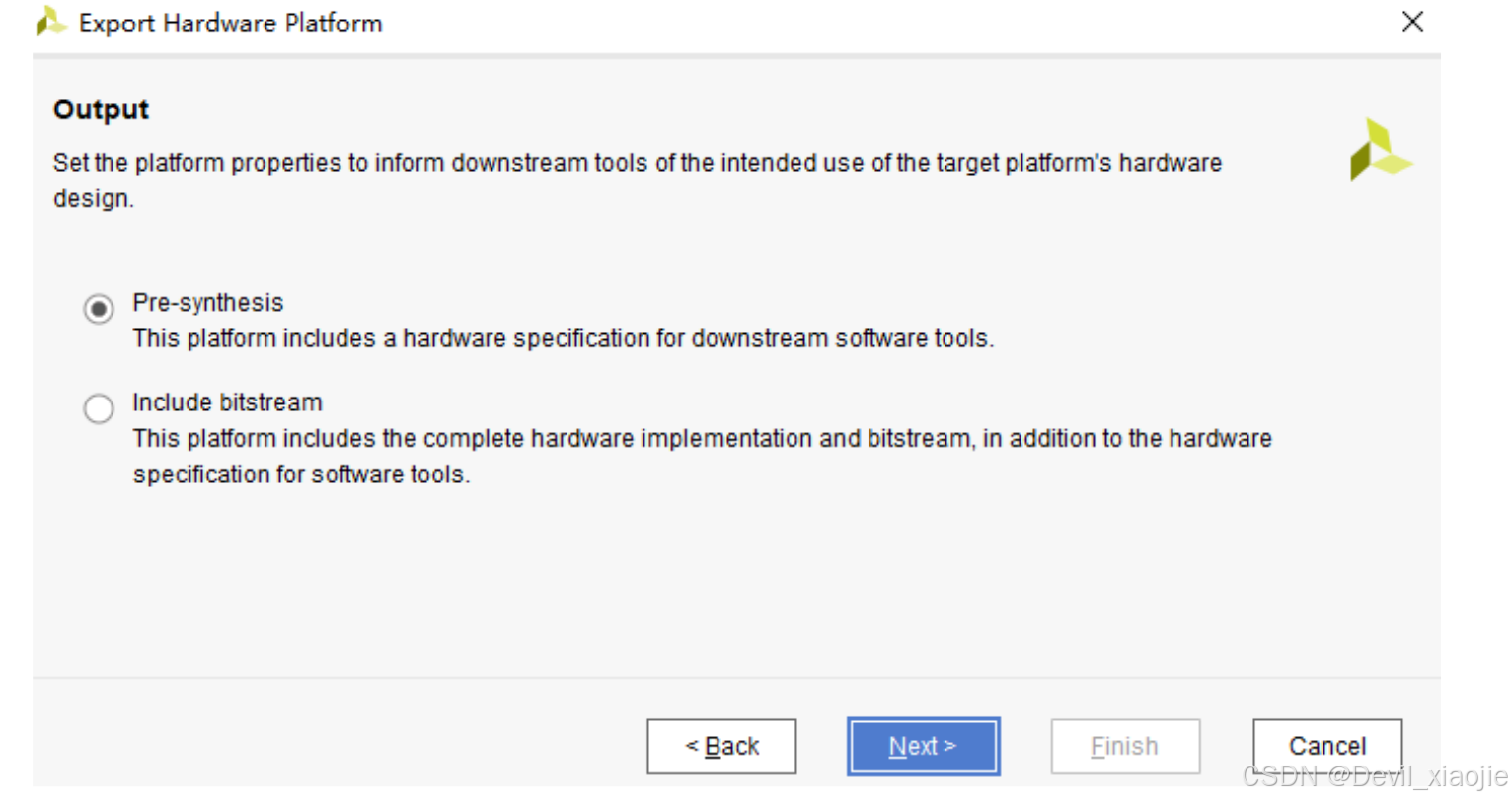

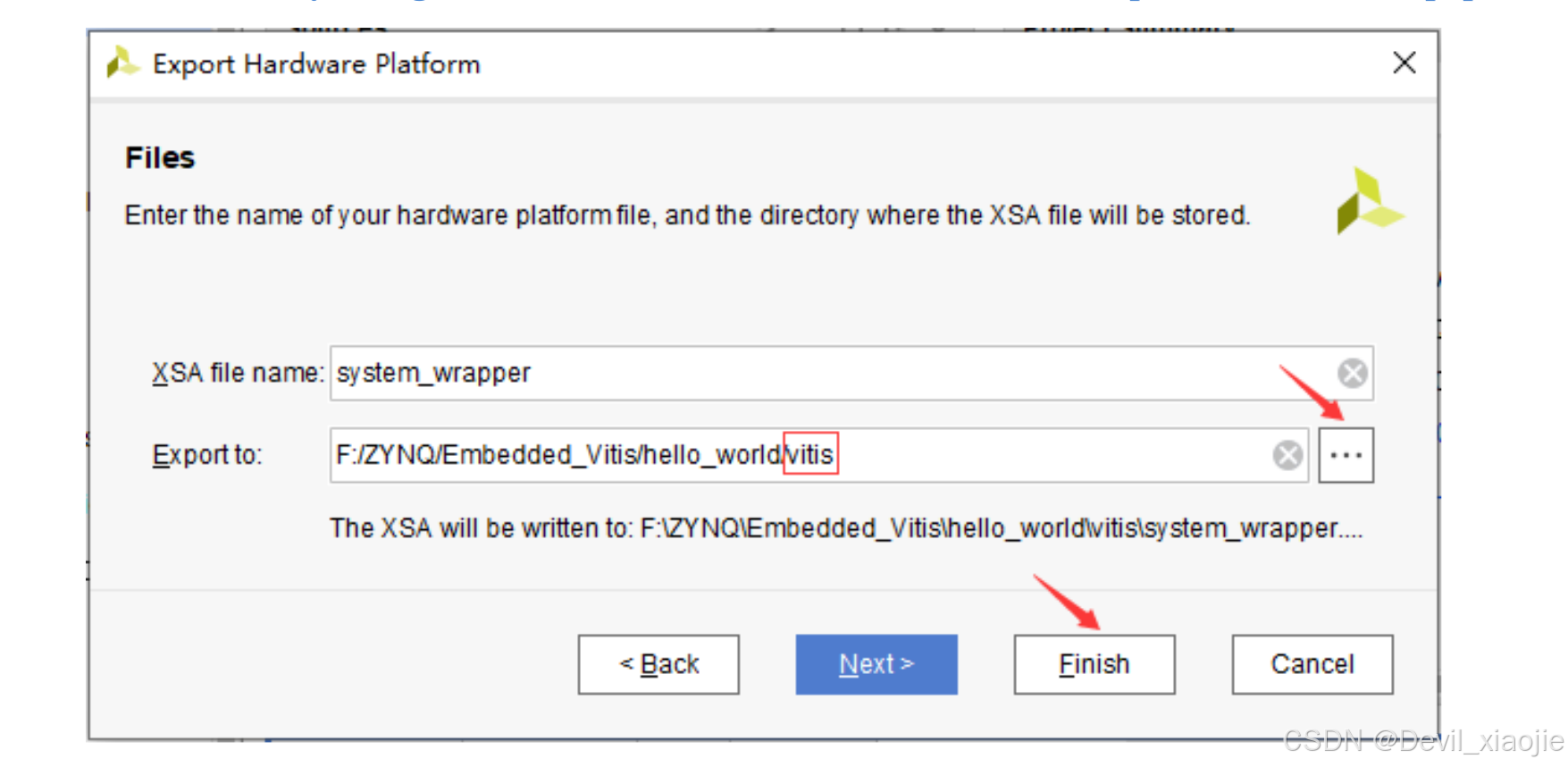

导出硬件描述文件(xsa文件,很重要,在vitis和petalinux开发时是必要的)

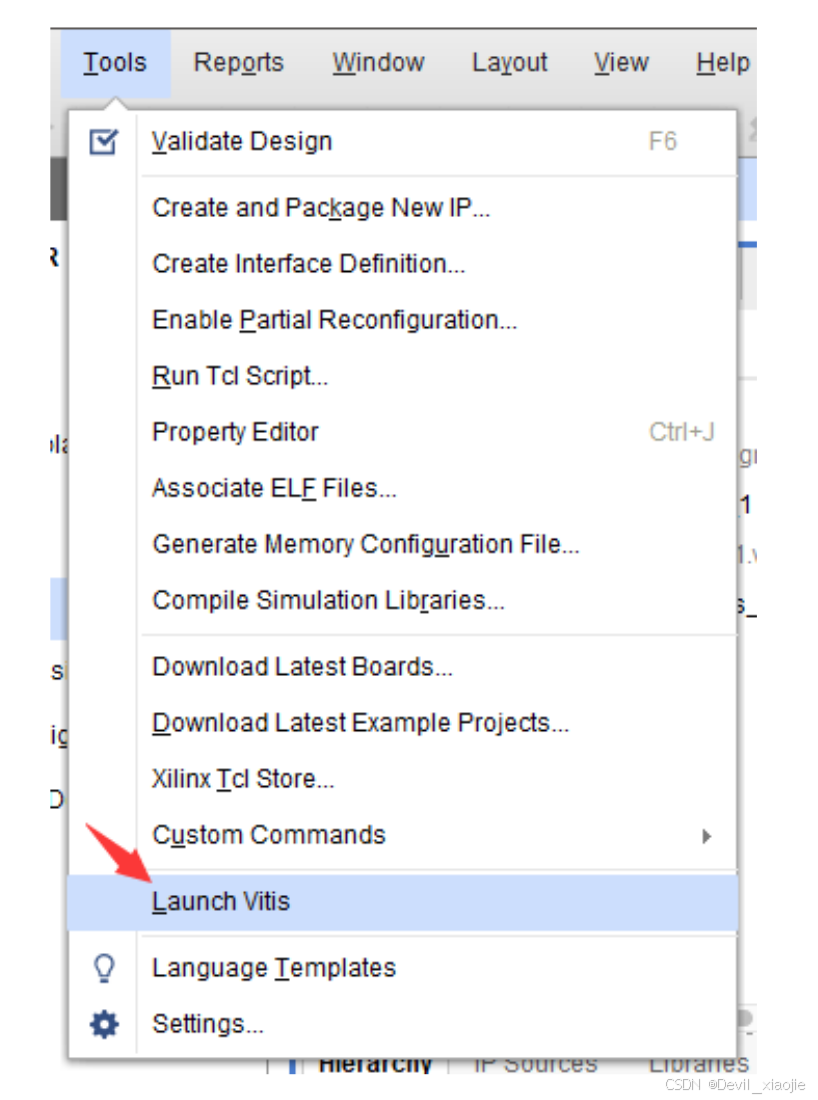

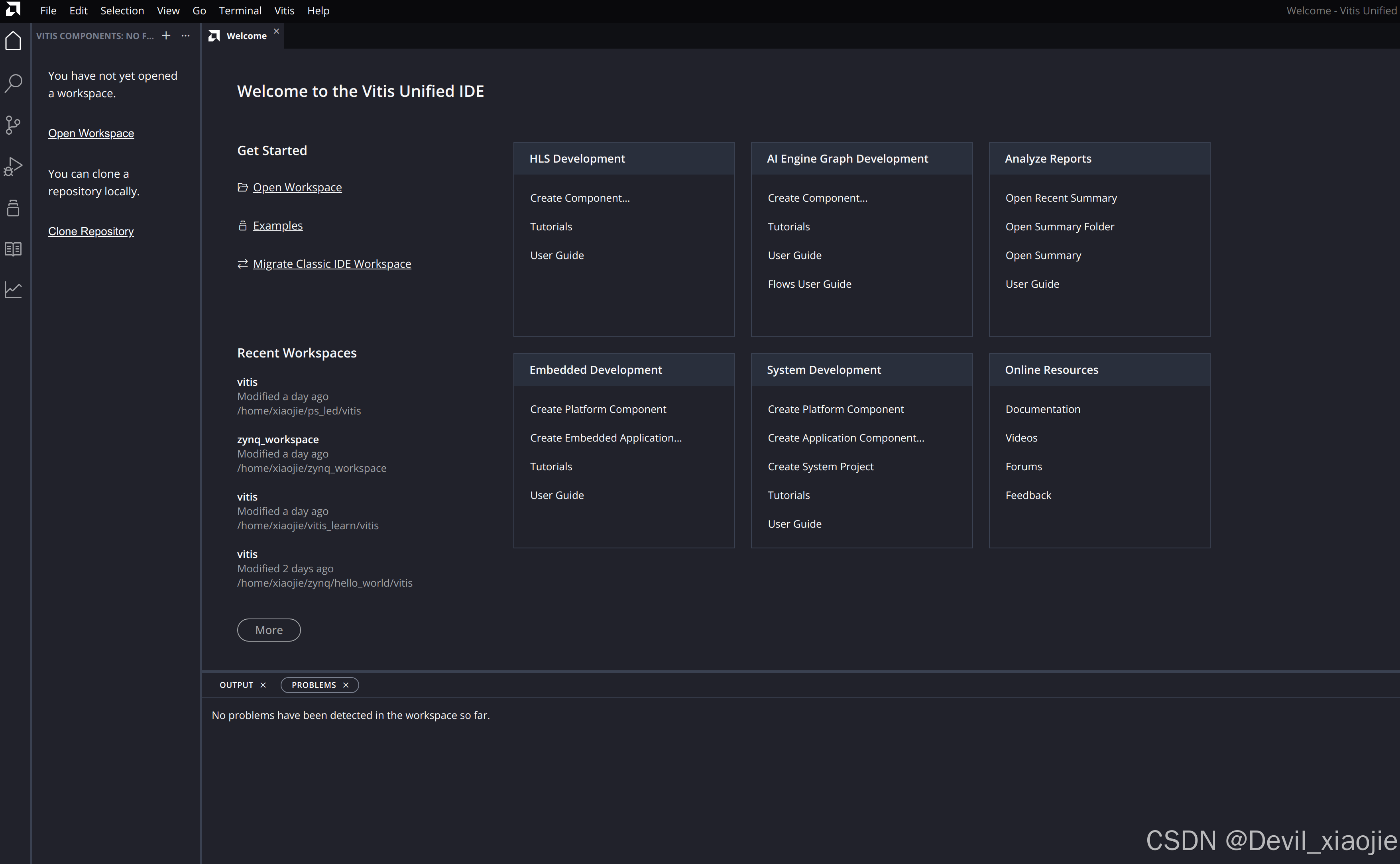

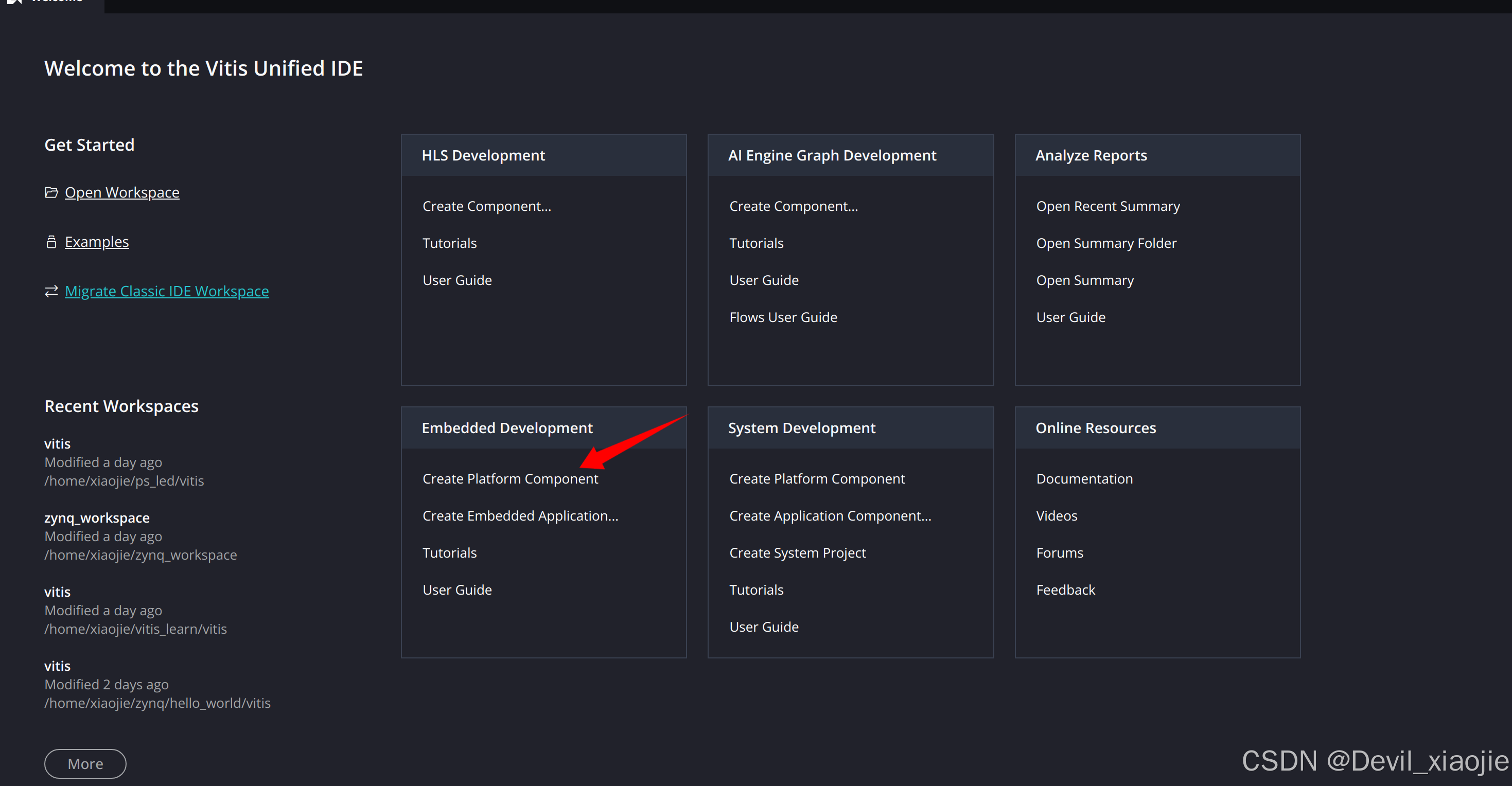

在vidado中启动vitis,在上面菜单栏找到tools下的launch vitis,打开vtis后,首先选择一个工作区,在使用xsa文件创建一个平台,然后在创建一个application(可以使用官方提供的一些历程进行快速验证设计)

点击open workspace选择一个文件夹作为工作区

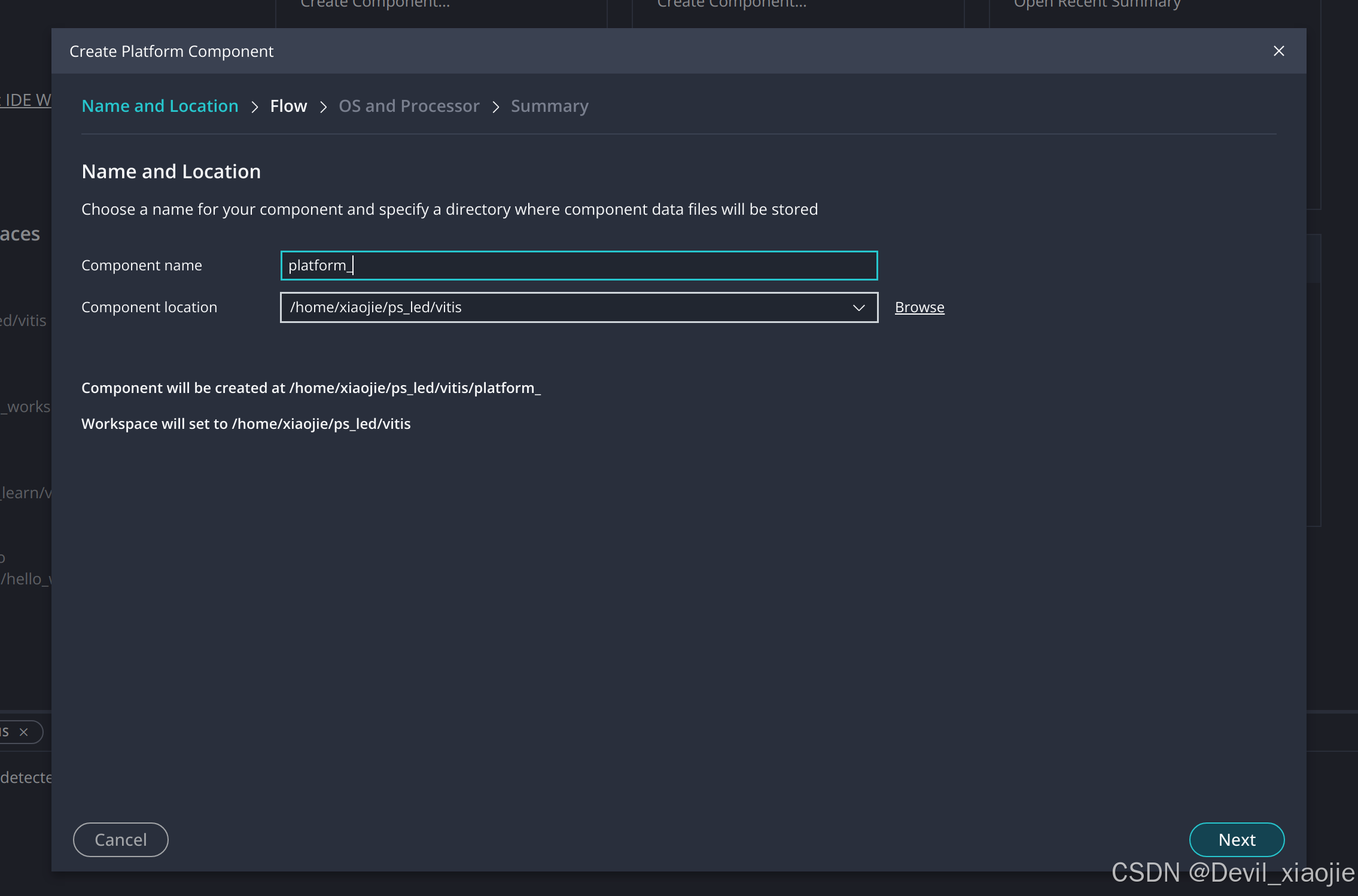

创建一个platform。

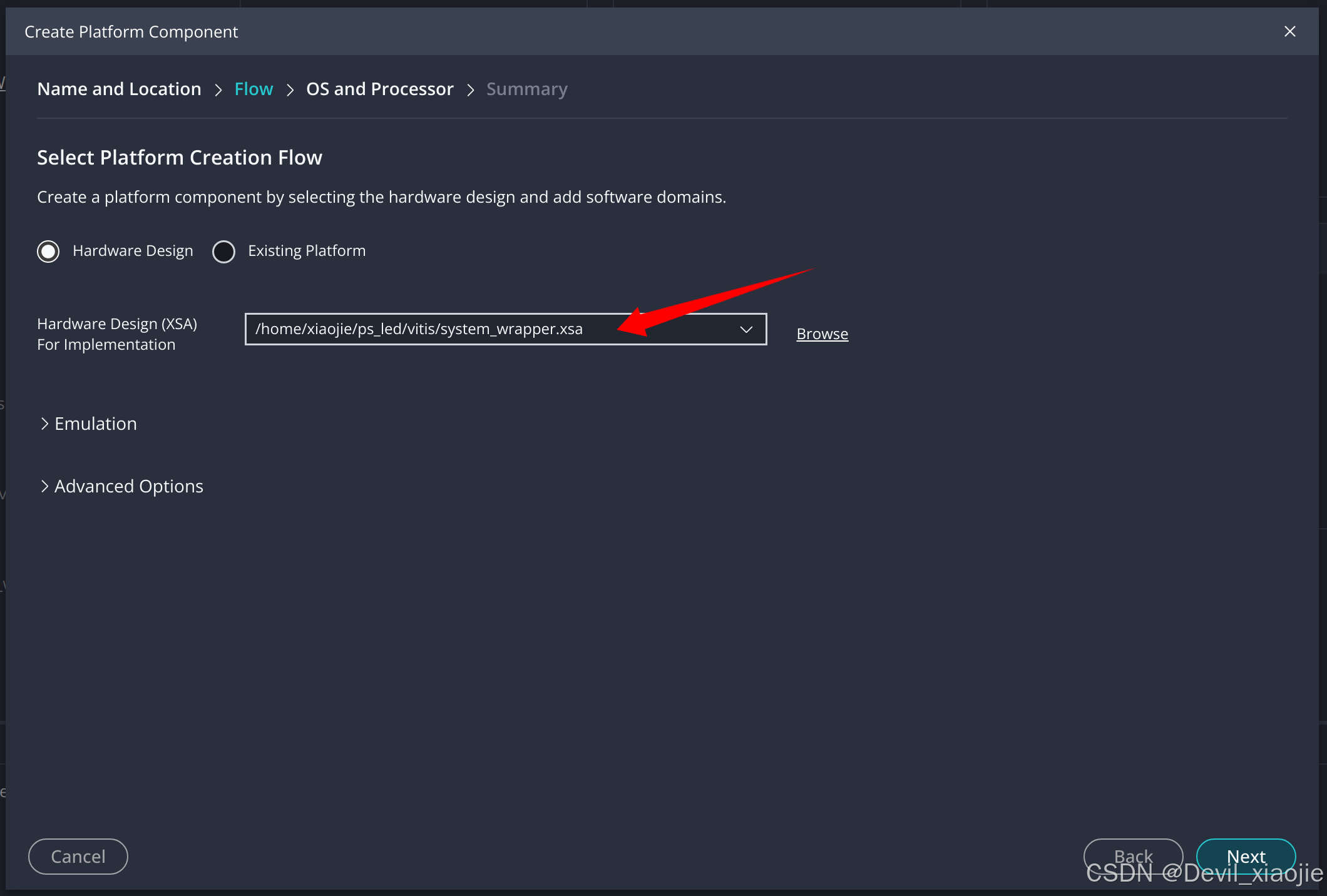

添加上我们之前导出的xsa硬件描述文件

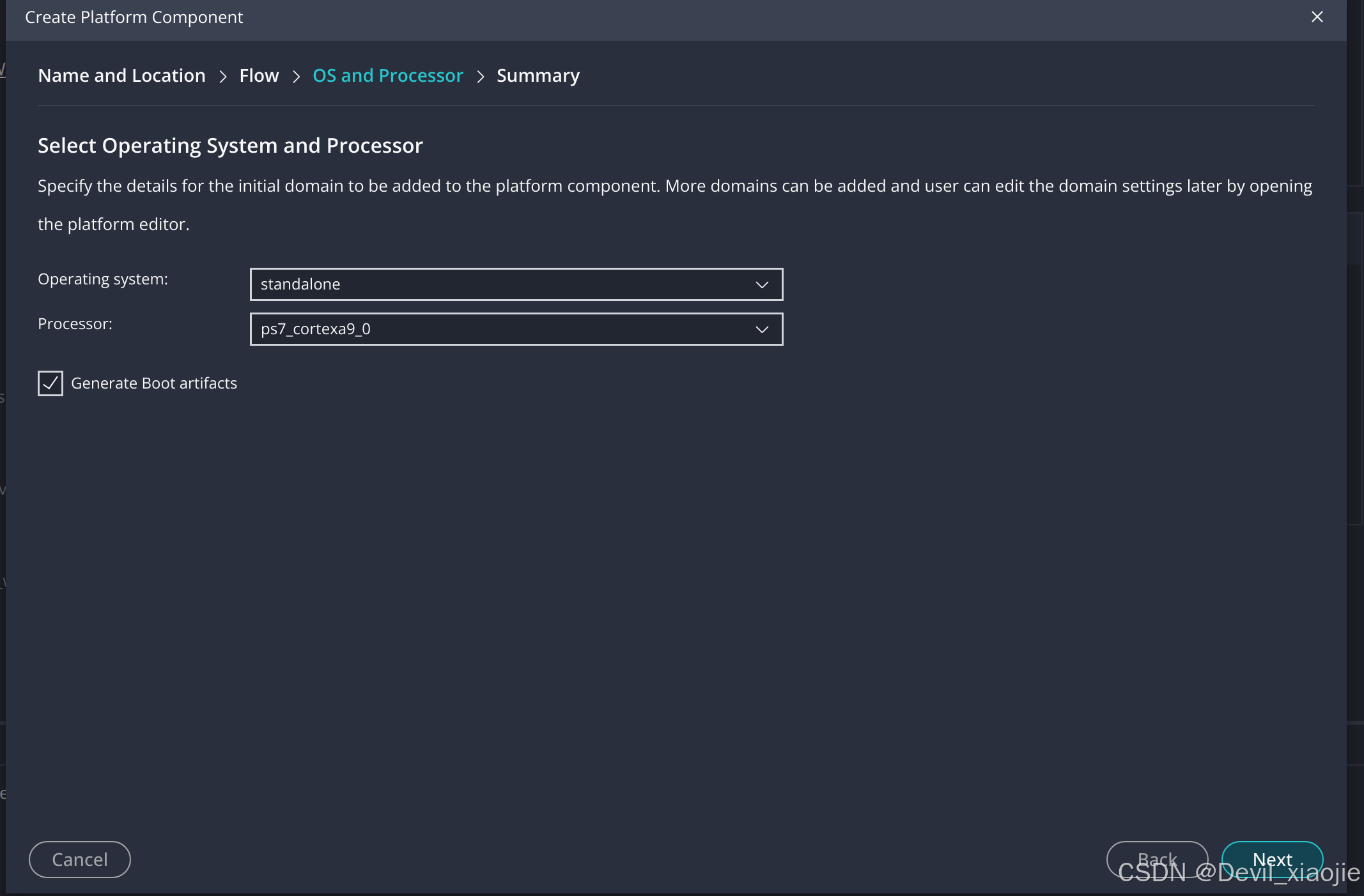

保持默认即可

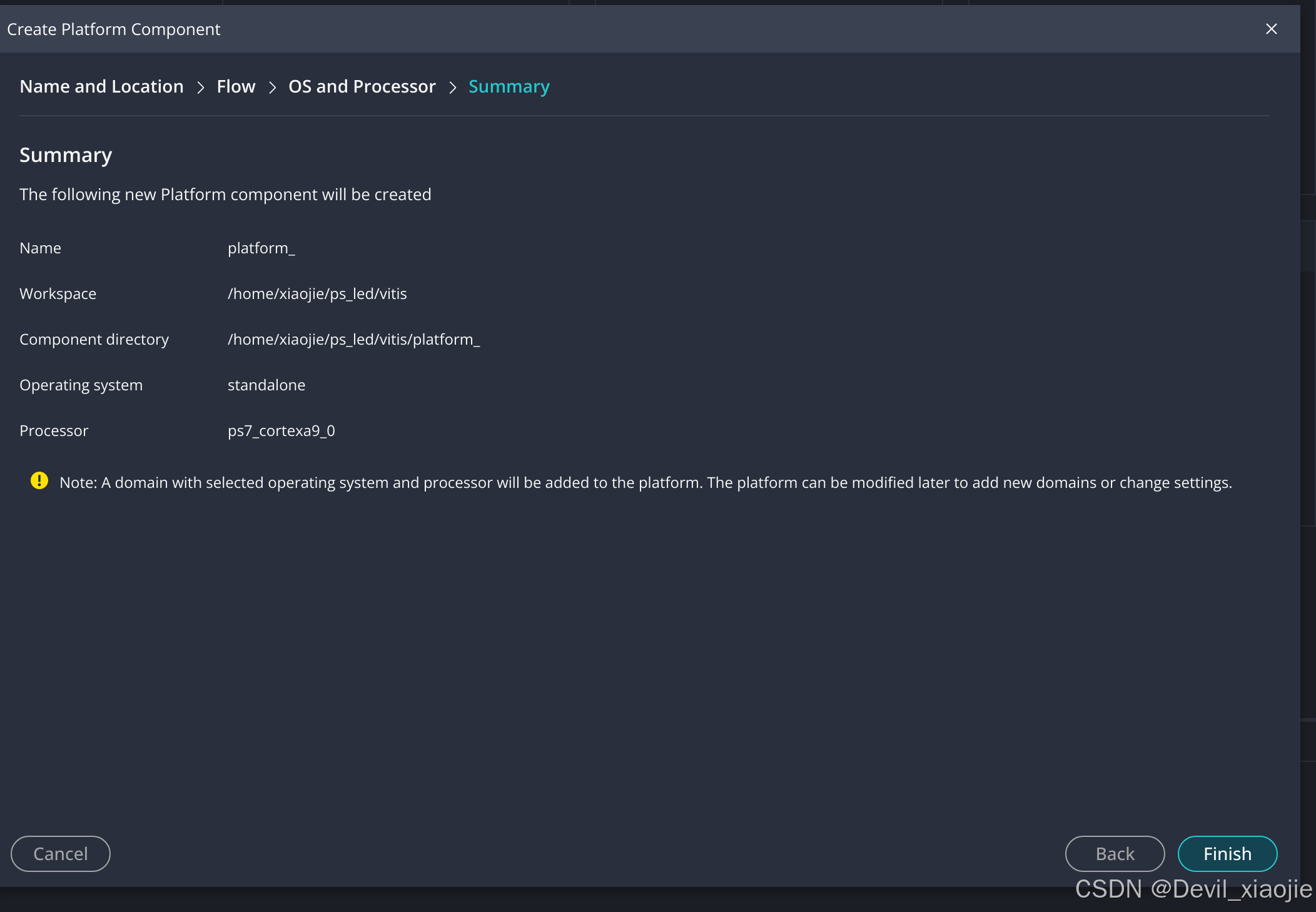

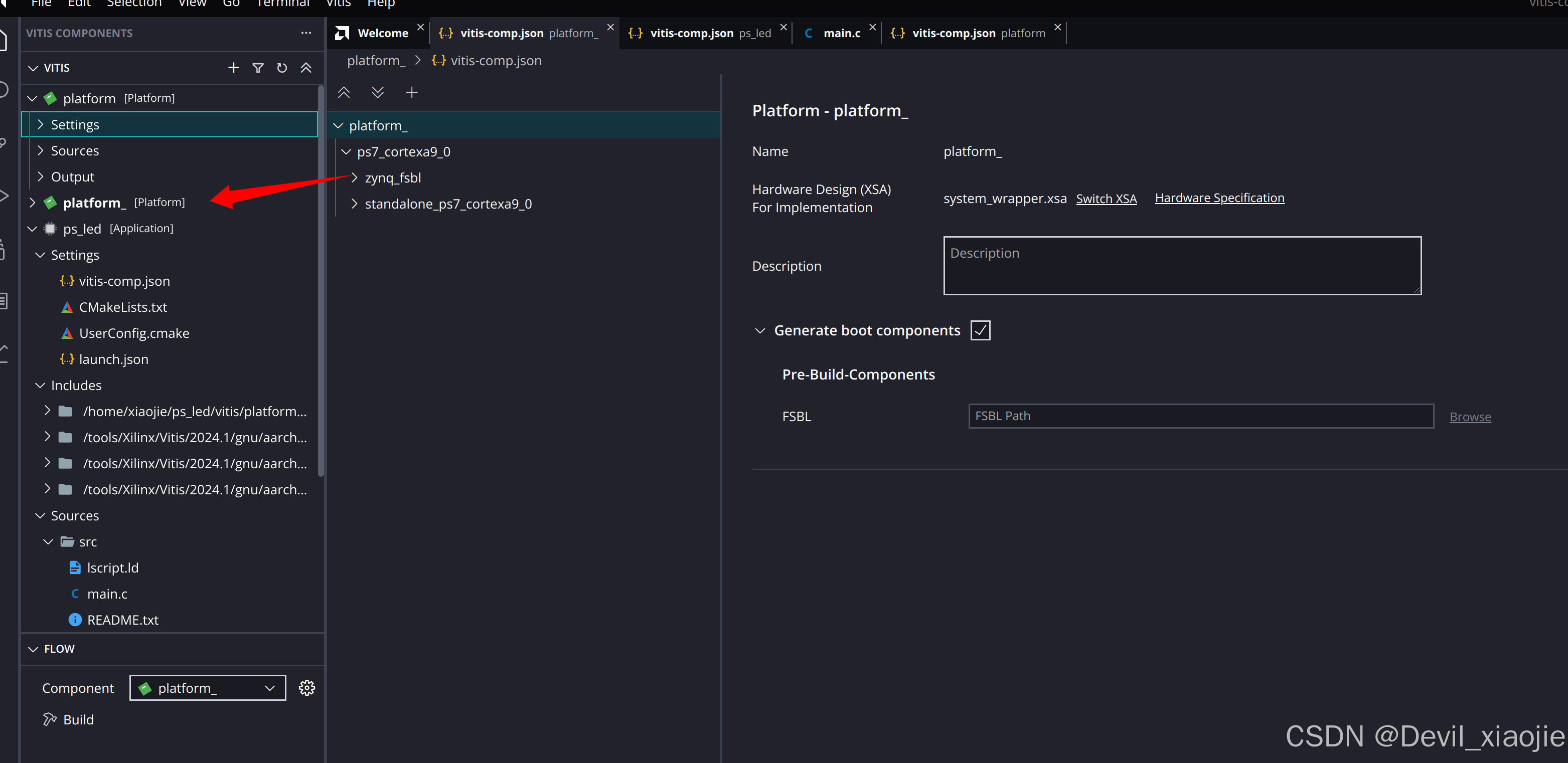

新建好的工程

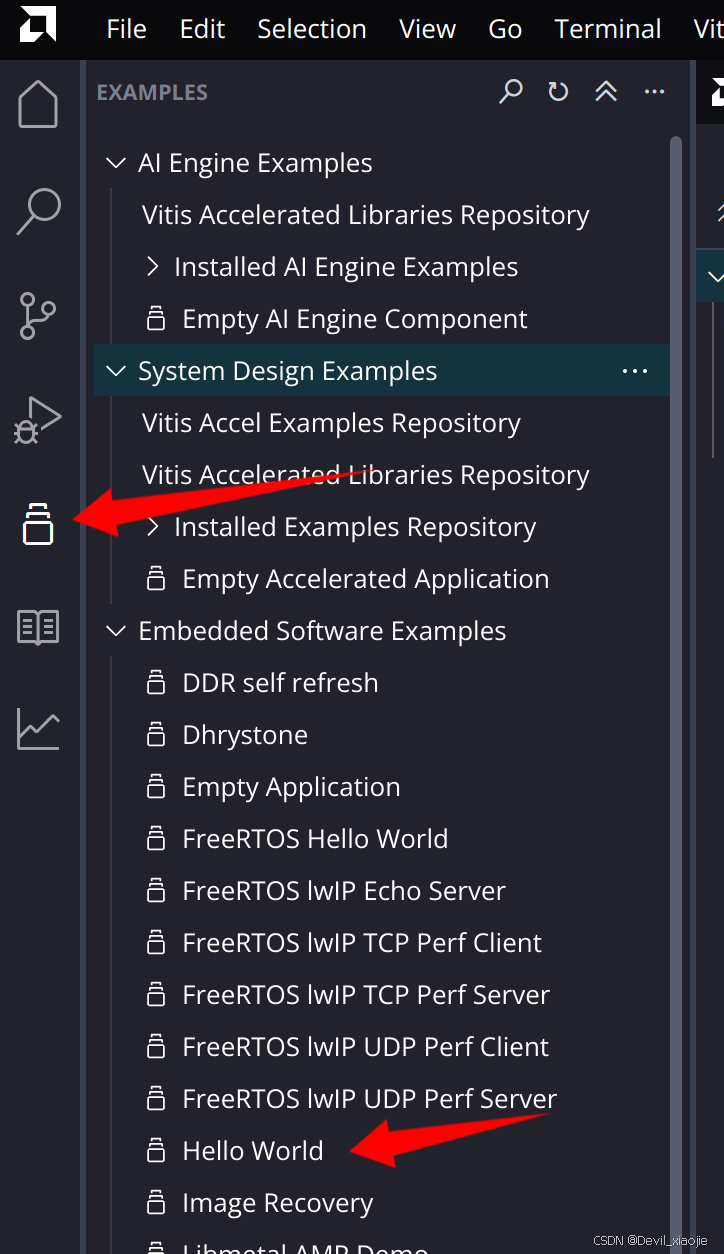

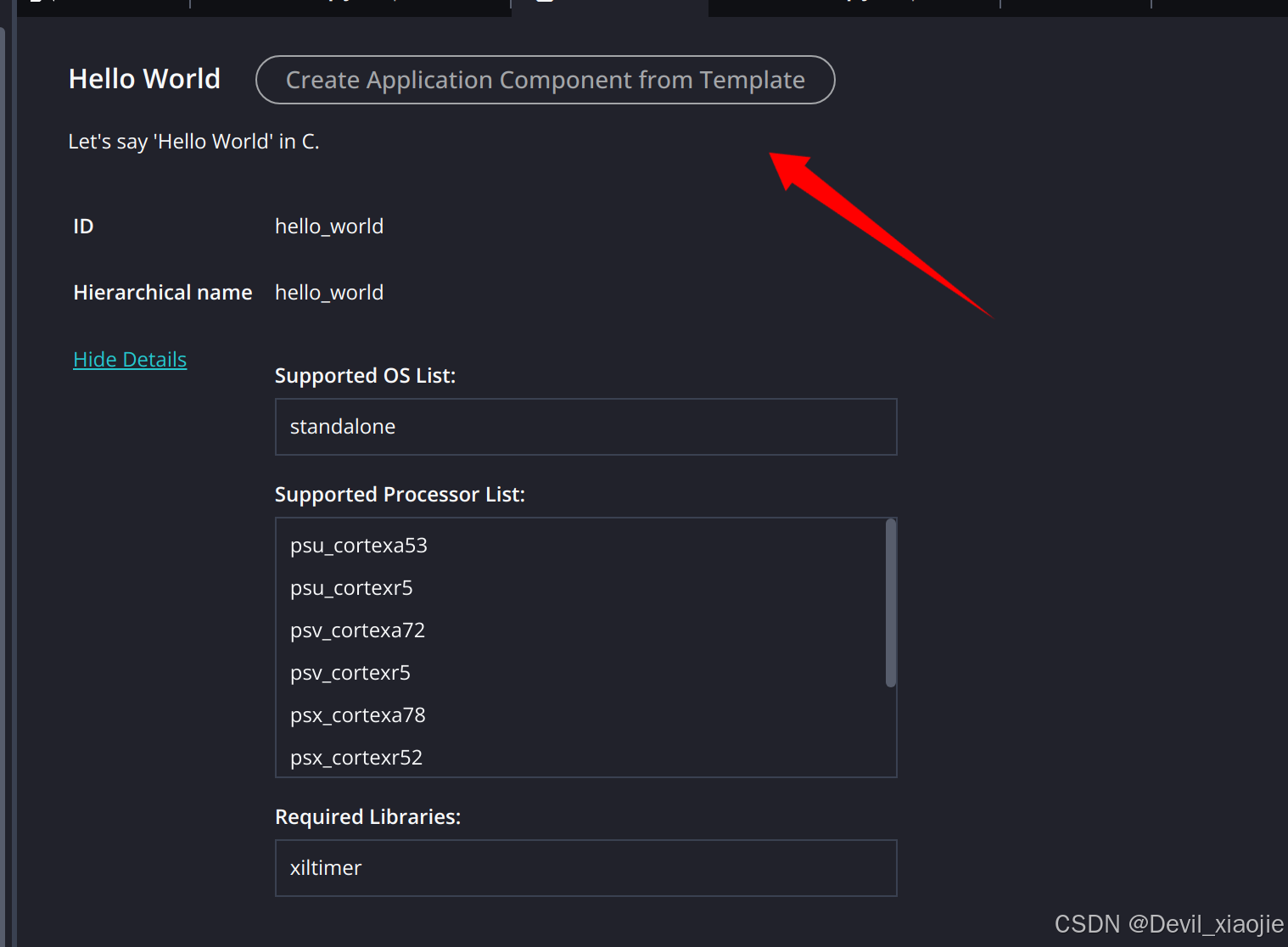

在左边可以找到官方例程创建的地方

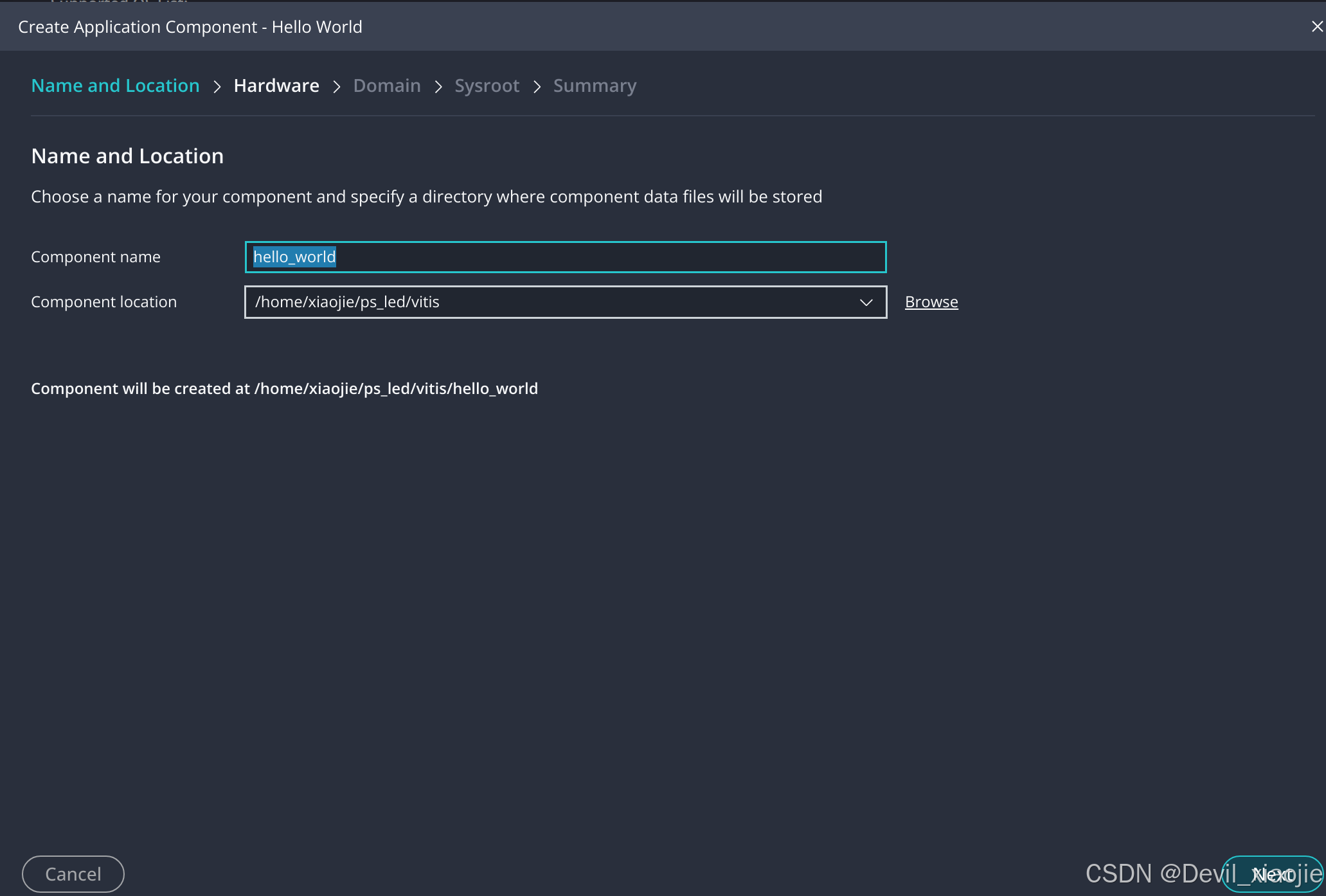

自定义即可

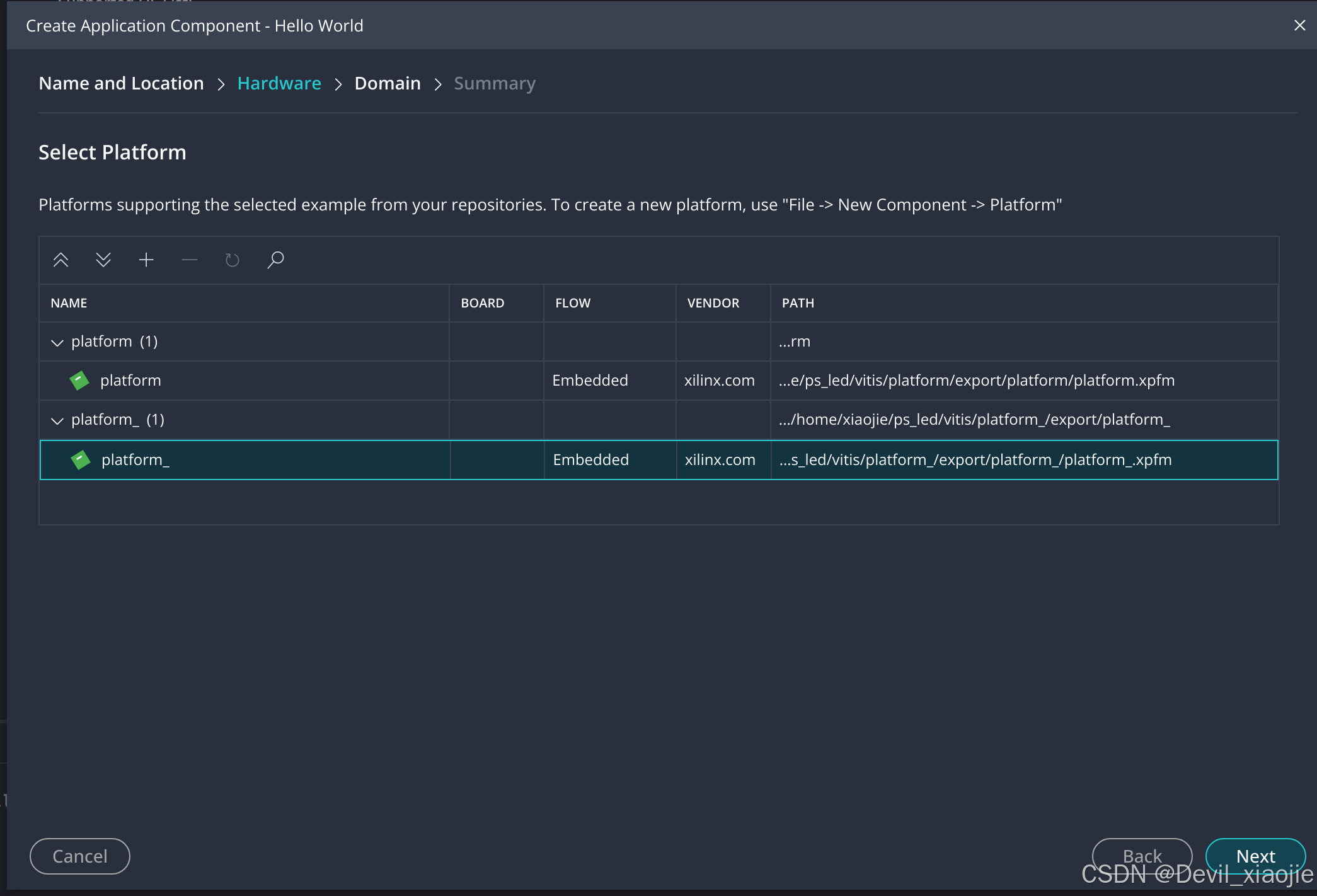

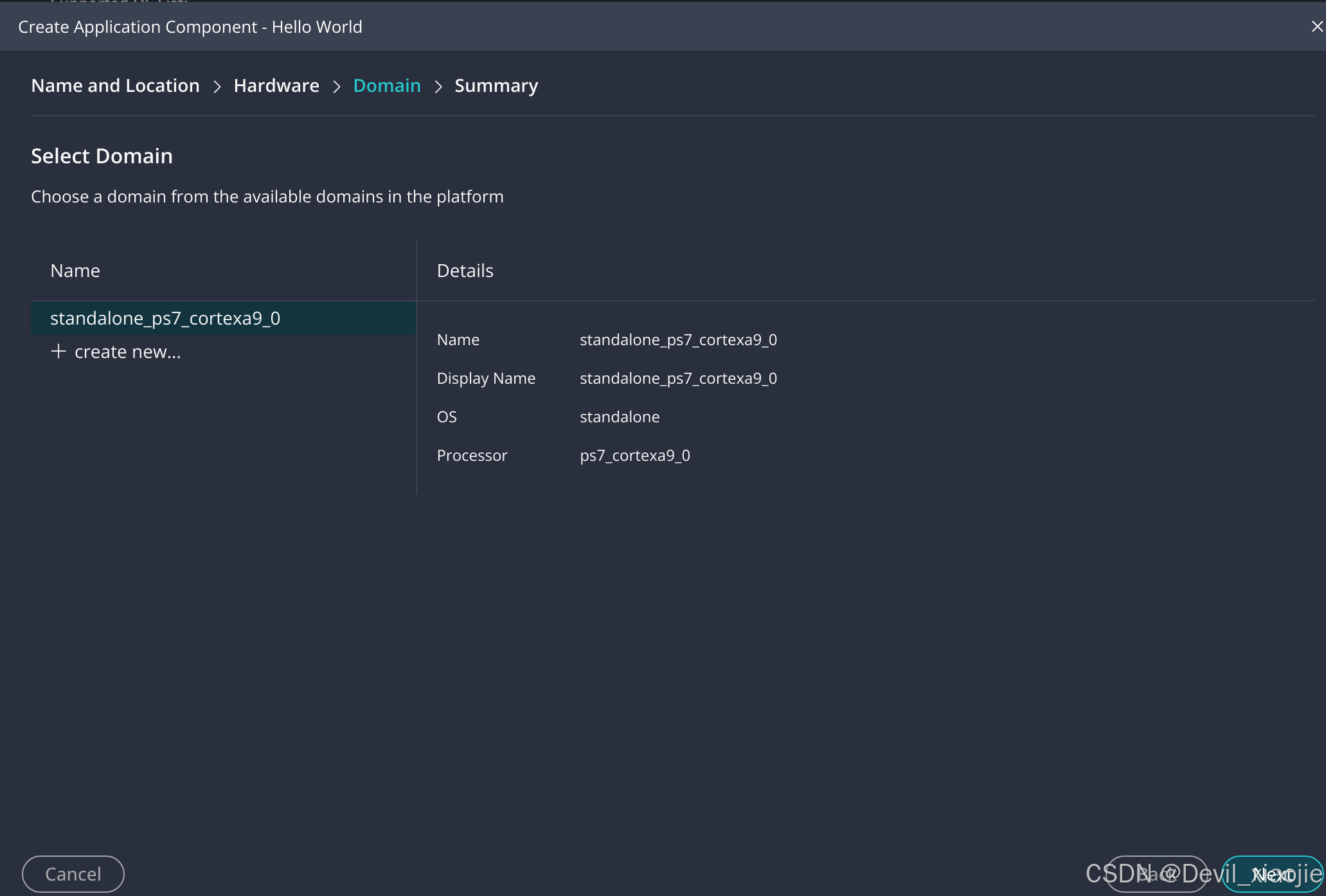

选择之前创建的平台

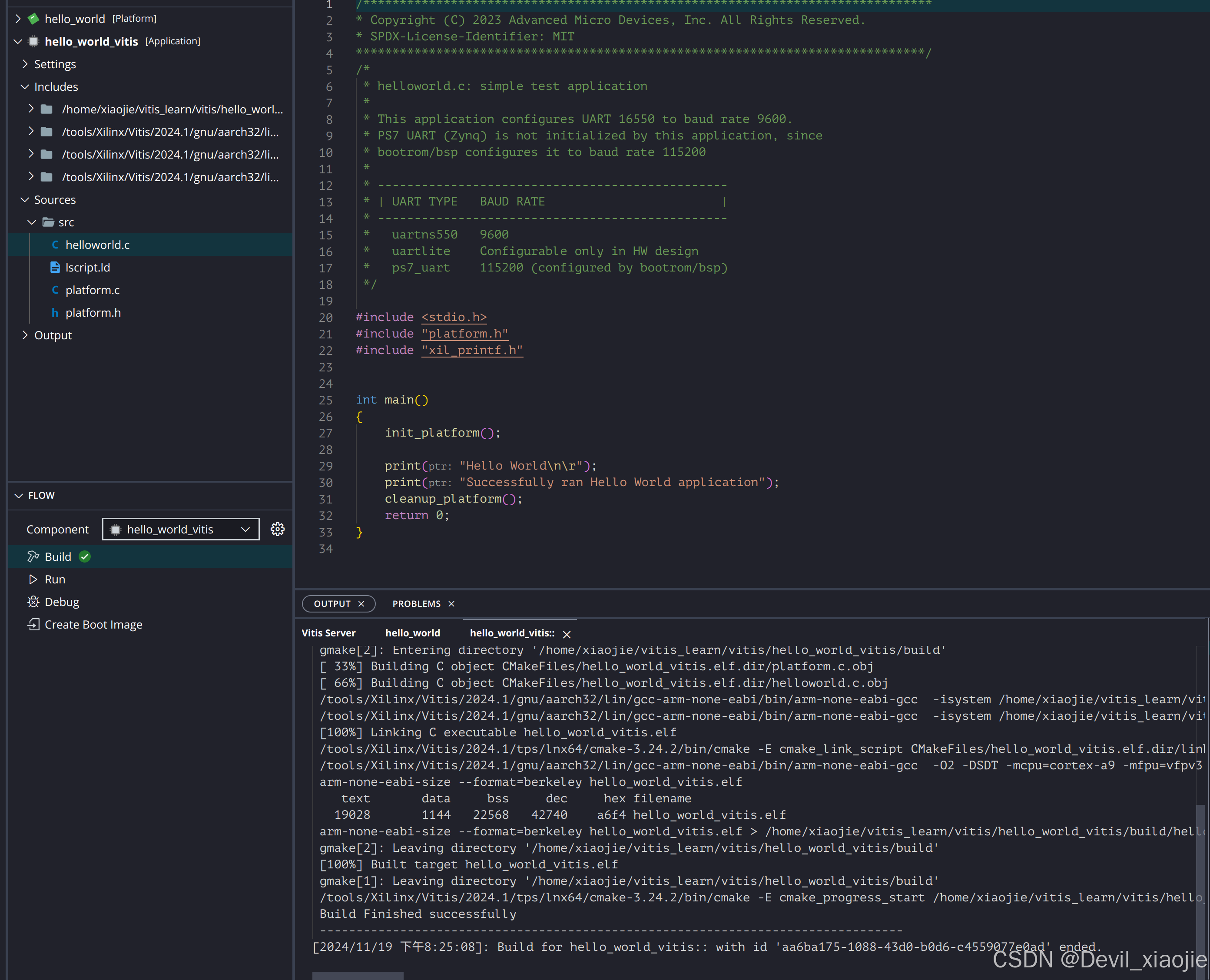

编译一下,无报错,可以点击run和debug进行验证使用的是JTAG。

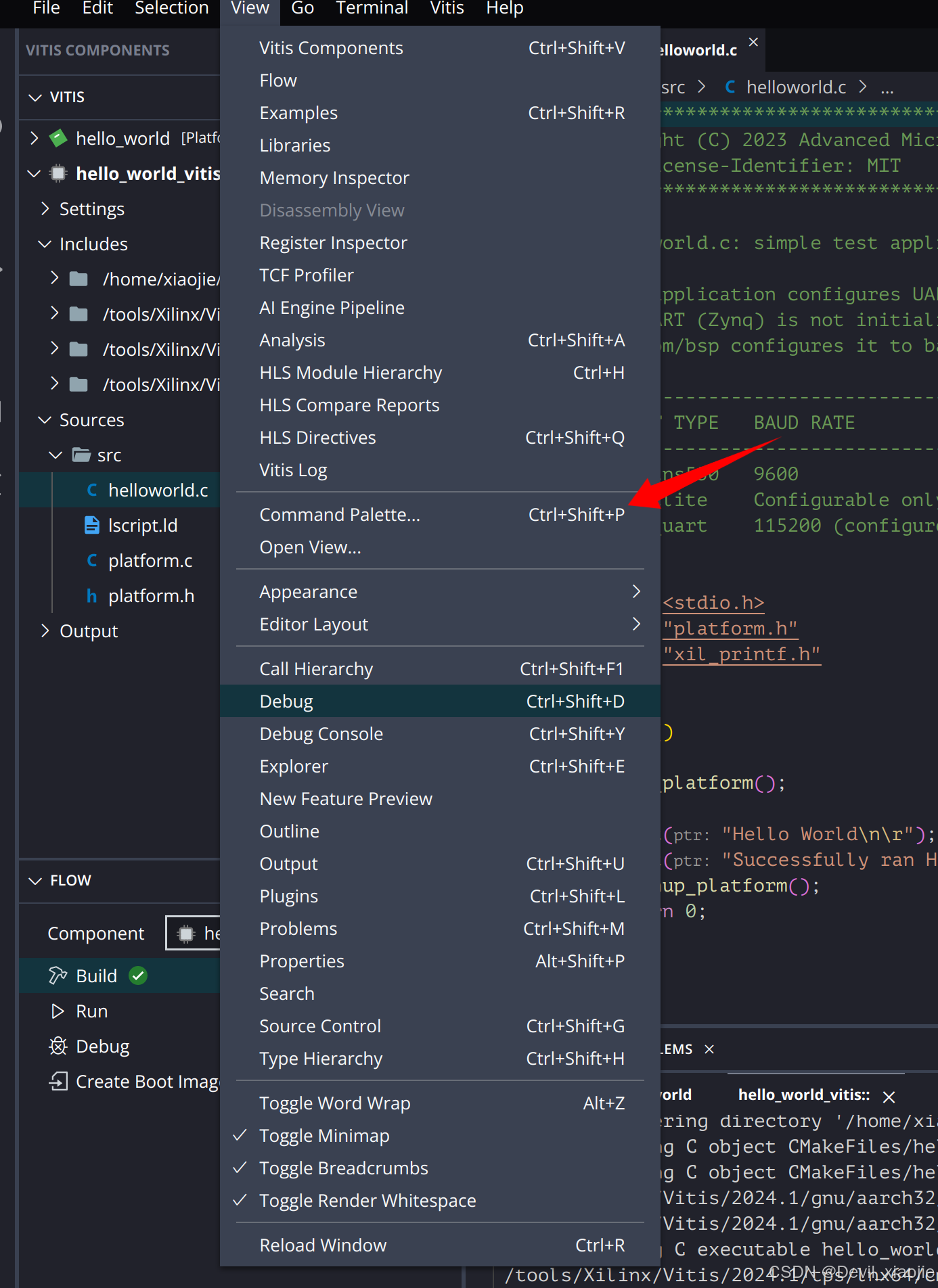

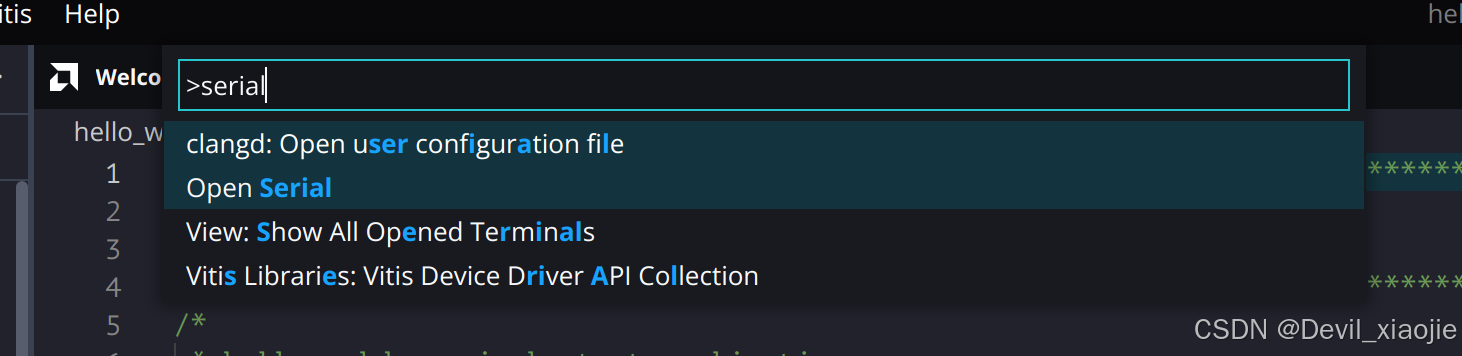

找到串口调试助手。

自己配置即可

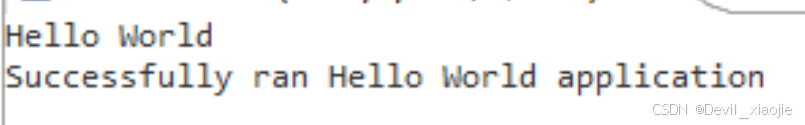

点击运行之后,会在serial终端里面看到输出的信息。

四. Vitis 应用开发

4.1 准备工作

- 硬件设计:

- 确保在 Vivado 完成硬件设计,生成 .xsa 文件。

- 安装检查:

- 确保 Vitis 安装完整。

4.2 创建硬件平台项目

- 导入 XSA 文件:

- 创建 Platform Project,选择 Vivado 导出的 .xsa 文件。

4.3 创建应用程序项目

- 应用模板选择:

- 根据需求选择模板,如 Hello World 或 Peripheral Tests。

4.4 工程编译与调试

- 编译与烧录:

- 完成编译后,通过 JTAG 接口将程序烧录到 FPGA。

五. MIO 和 EMIO 的实现

5.1 MIO(Multiplexed I/O)

- 功能描述:MIO是用于直接连接Zynq Processing System(PS)的固定I/O接口,支持外设如UART、SPI 和 I2C。它们不需要通过可编程逻辑(PL)的中介。

- 配置步骤:

- 在 Vivado 中,通过“Zynq Processing System”界面分配特定的输入/输出引脚到 MIO;

- 开启 MIO 外设功能,例如,把 UART1 映射到特定的 MIO 引脚。

- Vitis 中的使用:

- 调用适当的外设驱动,如 xuartps(UART 驱动)用于初始化并执行操作,例如发送和接收数据。

5.2 EMIO(Extended Multiplexed I/O)

- 功能描述:EMIO 允许 PS 和 PL 之间灵活的 I/O 指配,能够借助 FPGA 灵活实现自定义逻辑和外设控制。

- 配置步骤:

- 在 Vivado 的 Block Design 中,将 PL 与 PS 的接口切换至 EMIO;

- 利用 PL 来传输信号至外部硬件或在 FPGA 内部逻辑中处理。

- Vitis 中的使用:

- 集成对应外设驱动,通过 API 函数来进行 I/O 操作。

六. 中断实现

6.1 中断配置

- 在 Vivado 中:

- 激活 Zynq 中断控制器(General Interrupt Controller, GIC);

- 为需要中断支持的外设(如 GPIO、Timer)指定中断线。

- 在 Vitis 中:

- 创建中断向量表,自动生成的 Board Support Package(BSP)中通常包括,进行中断处理程序注册和初始化;

- 编写中断服务程序(ISR)并用 XScuGic_Enable() 函数激活特定中断。

6.2 中断服务程序和初始化

- 服务程序示例:

void MyInterruptHandler(void *CallbackRef) {

// 中断处理逻辑

}

- 初始化过程示例:

XScuGic InterruptController;

XScuGic_Config *ConfigPtr;

// 初始化中断控制器

ConfigPtr = XScuGic_LookupConfig(INTC_DEVICE_ID);

XScuGic_CfgInitialize(&InterruptController, ConfigPtr, ConfigPtr->CpuBaseAddress);

// 注册和启用中断

XScuGic_Connect(&InterruptController, INTR_ID, (Xil_ExceptionHandler)MyInterruptHandler, NULL);

XScuGic_Enable(&InterruptController, INTR_ID);

七. AXI 和 GPIO 的实现

7.1 AXI 总线概述

- 接口类型:

- AXI-Lite:简化版,用于低延迟控制信号。

- AXI-Full:全功能版,适合高吞吐量数据传输。

- AXI-Stream:面向高效数据流传输,无需地址,常用于实时应用。

7.2 添加和配置 AXI 外设

- 在 Vivado 中:

- 打开 IP Catalog,选择 AXI GPIO 等外设,配置 AXI 总线参数(地址范围、数据宽度);

- 将这些外设通过 Block Design 集成到 Zynq PS 的 AXI 总线上。

- 在 Vitis 中:

- 使用 xgpio 驱动 APIs 进行操作,初始化(XGpio_Initialize())、方向设置(XGpio_SetDataDirection())、数据读写(XGpio_DiscreteWrite() 和 XGpio_DiscreteRead())。

7.3 AXI GPIO 示例代码

#include "xgpio.h"

XGpio Gpio;

int main() {

// 初始化 GPIO

XGpio_Initialize(&Gpio, GPIO_DEVICE_ID);

// 设置方向,通道 1 设为输出

XGpio_SetDataDirection(&Gpio, 1, 0x00);

while (1) {

// 写入数据

XGpio_DiscreteWrite(&Gpio, 1, 0xFF);

}

return 0;

}

5144

5144

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?