在低频条件下,实际电容特性比较接近理想元件,但频率稍高时,就必须考虑他们的高频等效模型了。电容在电路中一个用途是滤波,必须将电容的寄生参数考虑进去,才能分析和设计出正确的滤波器。

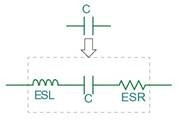

1电容的等效模型

如图1所示,实际电容可以看成是电容、电阻、电感三者的串联。其中等效串联电阻ESR(EquivalentSeries Resistance)和等效串联电感ESL(EquivalentSeries Inductance)分别从两个方面对电容的特性产生影响。

图1 实际电容等效模型

先来看ESR的影响。电容除了储能应用之外,大部分应用是滤波。大容量的滤波电容有钽电容和铝电解电容两种,其中钽电容性能更好更贵。其实钽电容也是有极性的电解电容,两种电容的性能主要差别就是ESR不同。

(1)理想电容C的两端电压绝不会产生“突变”,再大的充放电电流也只能产生“渐变”的电压,所以理论上并联电容的电路,其端电压是不会产生“毛刺”电压的。

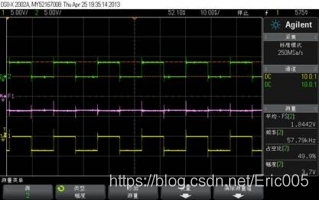

(2)实际滤波电容两端的电压会产生如图2所示的毛刺(中间波形,直流负压)。

图2 负压芯片TPS60400的输出

(3)电容端毛刺电压产生的原因就是电容的等效ESR。电容吞吐电流来保持自身端电压的稳定,但是吞吐电流会在ESR上产生压降,于是形成总的电压纹波乃至电压“毛刺”。

(4)相同容量的钽电解电容的ESR要远小于铝电解电容,所以同容量钽电容滤波的纹波电压要远小于铝电解电容。这就是为什么很多时候,我们把1μF的钽电容的滤波效果等效为10μF的铝电解电容。

(5)钽电容作为极性电容,特别需要提醒的是其外观标注,针插封装钽电容为正常的长引脚为阳极,但贴片钽电容的阳极却是划横线的那一端!

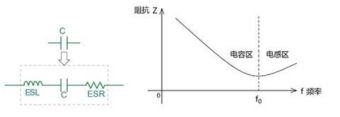

接下来看ESL的影响。由于ESL的存在,电容中容抗和感抗分量会随电信号频率变化。如图3所示:

图3 实际电容的阻抗

(1) 在低频段,所有电容毫无例外的均表现为电容特性(频率越高阻抗越低)。但是,当频率高于LC谐振频率f0时,电容转变成电感特性,即频率越高阻抗反而越高。而电感的特性不仅不会稳定电压,还会产生感应电压。

(2)不同材料和构造电容,其转折频率f0差别很大,一般说来,大容量的电容频率特性差(转折频率f0低),小容量的电容频率特性好(转折频率f0高)。

(3)值得庆幸的是,高频电容的容量虽小,但高频时真正起滤波作用的容抗却很小,“高频小容量”电容与“低频大容量”电容可以互为补充。

(4)实际电路中并联不同种类的电容,可以实现全频率范围内的滤波。多个电容并联滤原则上相差至少10倍,一般100倍为宜。

2电源线耦合干扰

“干扰”一词在初学者看来就是“无名肿痛”,能够想象到的就是“无所不在”又“无计可施”的电磁辐射之类的。其实电路中绝大部分的干扰都是来自电路自身的电源线(VCC和GND)。

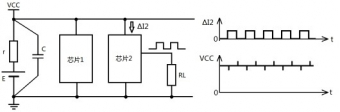

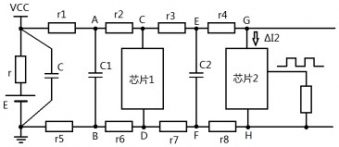

(1)如图4所示,电源给多个芯片供电。芯片2为数字芯片,输出方波信号给负载RL。

(2)由于负载电流为方波,所以芯片2向电源索取的电流将不是恒流,产生了ΔI2。理想电源是不存在的,所有电源均有内阻,ΔI2会在电源内阻r上产生压降,从而导致VCC的变化。

(3)由于滤波电容C的稳压作用,ΔVCC不至于是方波,但是会像图4右所示的波形,产生毛刺电压(突变电流在ESR上的压降)。毛刺的位置对应了芯片2输出电流的开关时刻(突变时刻)。

(4)城门失火、殃及池鱼,芯片1的供电VCC不再是恒定直流,而是图4右所示那样的受到芯片2干扰的电源电压,这就是电源线耦合干扰,即芯片2通过电源线将干扰传递给了芯片1。

图4 电源线耦合干扰原理

要减缓乃至消除电源线耦合干扰的影响,就需要用到去耦电容,其作用和水库非常类似,起到调节水流(电流)盈亏的作用。芯片配上去耦电容以后,既不干扰别人,也不被别人干扰。

(1) 当芯片自身用电量突然增加时,可以借去耦电容的电荷应急,而不会影响主回路供电。去耦电容损失的电荷,可以慢慢由主供电回路补充。

(2) 当芯片自身用电量突然减少时,多余的电荷可以往去耦电容里灌,而不影响主回路的用电。去耦电容多余的电荷,可以慢慢泄放到主供电回路。

(3) 当主供电电压发生突变(电压毛刺)时,芯片将受到去耦电容的“隔离”保护,减缓影响。

“去耦”电容的布置应尽量靠近本器件的VCC引脚和GND引脚。

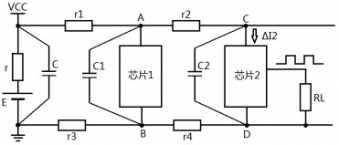

如图5所示,由于线路是有电阻的,电容C1和C2仅能稳定UAB和UEF两端电压,芯片处的供电电压UCD和UGH仍然是波动的。

图5 错误的去耦电容位置

如图6所示,由于采用了就近单点接法,芯片供电电压UAB和UCD就是电容C1和C2两端电压,供电电压自然就能达到稳定。

图6 正确的去耦电容位置

滤波电容和去耦电容本质都是一样的,用于稳定电压的作用。两者的区别只是观察的视角不同,滤波电容是对电源而言的,去耦电容是针对用电器(芯片)而言。所以,选择ESR尽量小的电容的原则也适用于去耦电容。

问题1:陶瓷电容、钽电容、铝电解电容哪一种ESR最低?哪一种最高?

参考答案:陶瓷电容最低,铝电解电容最高

问题2:滤波时为什么要把低频大电容和高频小电容同时使用?

参考答案:因为二者ESL的转折频率不同,组合使用才能实现全频率范围内的滤波

问题3:去耦电容为什么要尽量靠近芯片Vcc和GND?

参考答案:因为如果远离Vcc和GND,线路上的电阻会产生压降,导致芯片供电电压不稳定

本文详细介绍了电容的实际特性,包括等效串联电阻(ESR)和等效串联电感(ESL)对电容在高频条件下的影响。在滤波应用中,大容量电容如钽电容的ESR较低,能有效降低电压纹波。ESL则会导致电容在高频时由电容特性转变为电感特性。电源线耦合干扰是电路中的常见问题,去耦电容通过靠近芯片布置,能有效稳定供电电压,防止干扰传播。选择低ESR电容对于滤波和去耦都至关重要。

本文详细介绍了电容的实际特性,包括等效串联电阻(ESR)和等效串联电感(ESL)对电容在高频条件下的影响。在滤波应用中,大容量电容如钽电容的ESR较低,能有效降低电压纹波。ESL则会导致电容在高频时由电容特性转变为电感特性。电源线耦合干扰是电路中的常见问题,去耦电容通过靠近芯片布置,能有效稳定供电电压,防止干扰传播。选择低ESR电容对于滤波和去耦都至关重要。

9939

9939

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?