Xilinx DDR4 DDR3 多通道读写防冲突设计,可实现最高8个通道同时读写DDR且不冲突问题,通道数可根据使用来决定。

每个通道读写接口简单,操作独立,可同时实现最高8个通道的读写请求。

此工程经过2个月的实际上板疲劳测试,功能稳定,时序健壮,性能优异,有需要用到DDR4 DDR3的多通道 单通道的地方,此工程代码可直接移植。

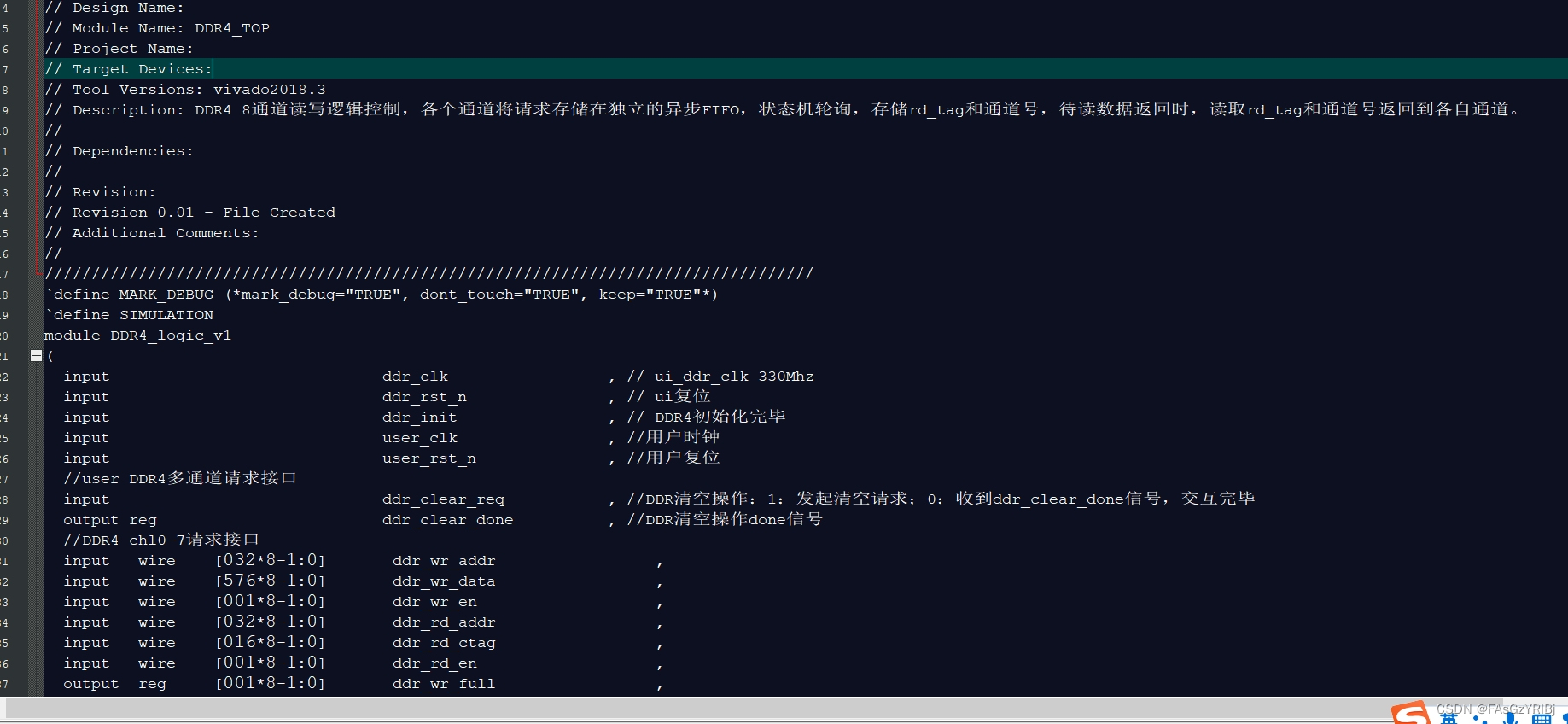

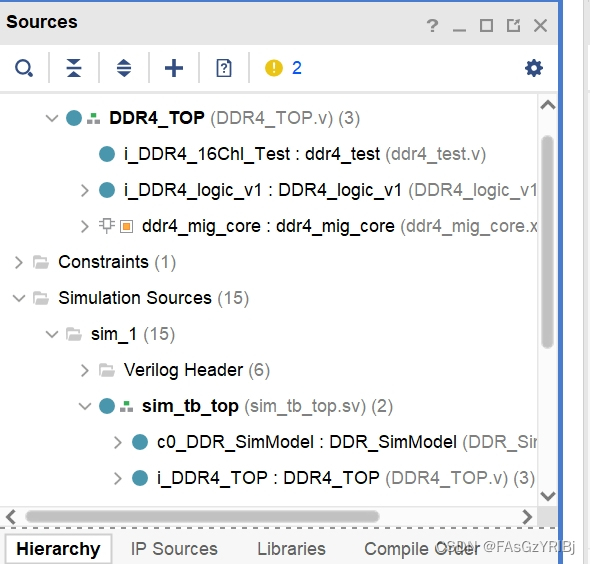

本工程通过Vivado实现,程序中包含详细注释,另一份详细设计说明文档,保证可以弄懂DDR的逻辑和设计架构,可直接应用于工程设计中。

Xilinx DDR4 DDR3 多通道读写防冲突设计

随着科技的发展,DDR(Double Data Rate)内存已成为计算机的标配,越来越多的设备开始采用DDR4 DDR3内存。然而,随着内存容量的增加和速度的提高,内存读写的速度也变得越来越重要,因此如何实现多通道读写防冲突设计成为了DDR4 DDR3内存设计的一个重要问题。

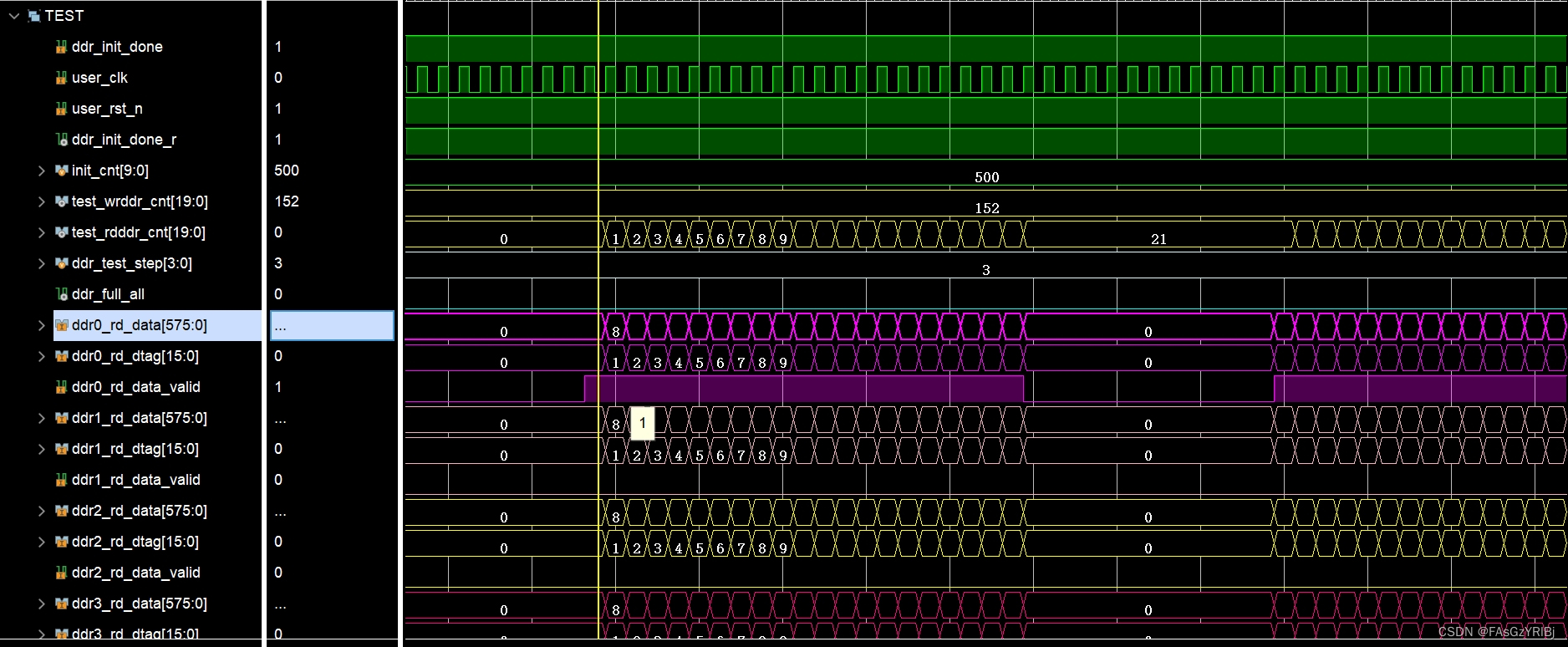

为了解决这个问题,Xilinx推出了一种多通道读写防冲突设计方案。该方案利用了FPGA芯片的灵活性和可重构性,可实现最高8个通道同时读写DDR且不冲突问题,通道数可根据使用来决定。每个通道读写接口简单,操作独立,可同时实现最高8个通道的读写请求。

这个方案经过了2个月的实际上板疲劳测试,功能稳定,时序健壮,性能优异,有需要用到DDR4 DDR3的多通道单通道的地方,此工程代码可直接移植。

本工程通过Vivado实现,程序中包含详细注释,另赠送一份详细设计说明文档,保证可以弄懂DDR的逻辑和设计架构,可直接应用于工程设计中。

方案技术细节

多通道读写防冲突是通过调整时序和逻辑实现的。首先,每个通道的读写接口都被设计为相互独立的,这样就可以避免不同通道之间的干扰。其次,通过合理的时序设计,确保每个通道按照规定的时间顺序进行读写操作,从而避免冲突。最后,为了提高性能,在设计时采用了流水线技术,将读写操作分为多个阶段,从而实现高效的并行处理。

具体实现中,设计人员需要在Vivado中进行时序和逻辑的调整,以适应不同场景下的读写需求。同时,需要特别关注时序的健壮性,避免由于时序不准确引起的读写出错问题。

方案应用

多通道读写防冲突设计方案广泛用于需要高速、高容量内存的计算机、服务器、工控设备等场景。在这些场景下,大量的数据需要进行读写操作,如果读写速度不够快,就会导致系统性能下降,影响用户体验。采用多通道读写防冲突设计方案可以有效提高内存读写速度,并避免不同通道之间的冲突问题,从而确保系统性能和稳定性。

总结

多通道读写防冲突设计方案是一种重要的DDR4 DDR3内存设计方案,它能够显著提高内存读写速度,并避免不同通道之间的冲突问题,从而确保系统性能和稳定性。在实际应用中,设计人员需要根据不同场景下的需求进行时序和逻辑的调整,同时需要特别关注时序的健壮性,以确保系统的稳定性和可靠性。

相关代码,程序地址:http://lanzouw.top/674731967969.html

744

744

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?