Xilinx DDR4/DDR3多通道读写防冲突设计,可实现最高8个通道同时读写DDR且不冲突问题,通道数可根据使用来决定。每个通道读写接口简单,操作独立,可同时实现最高8个通道的读写请求。此工程经过2个月的实际上板疲劳测试,功能稳定,时序健壮,性能优异,有需要用到DDR4/DDR3的多通道/单通道的地方,此工程代码可直接移植。

如有疑问,可加qq:1023350982

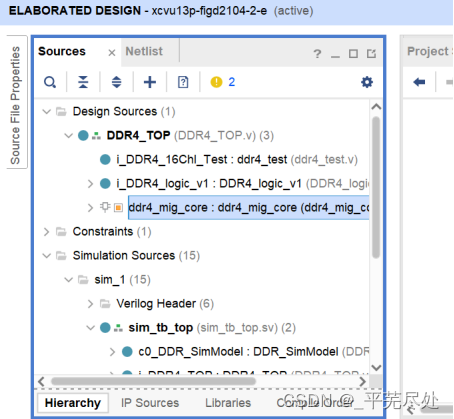

1、设计架构说明

工程一共分为三部分,DDR4_TOP为项目顶层,包含ddr4_test、DDR4_logic_v1、ddr4_mig_core三块,其中ddr4_test为测试逻辑,产生DDR测试读写请求;DDR4_logic_v1为整个工程的核心,包含读写命令解析存储、命令解析、读写时序生成、多通道仲裁逻辑、DDR4 IP核控制,读数据返回、跨时钟域处理等。代码详细说明在工程中已写注释。

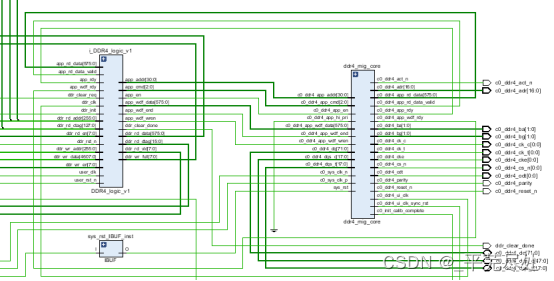

2、原理图

3、ddr4_test模块说明

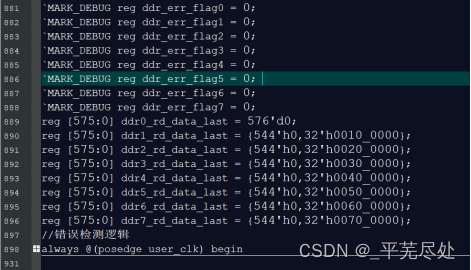

这个模块的功能是产生测试逻辑,其中包含错误检测功能,下面这些信号统计各个通道的写请求次数与数据有效返回次数,并统计8个通道的总次数。便于错误定位于查找。

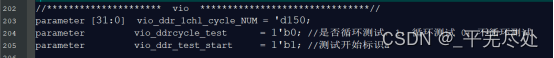

下面这些信号的值是可以改变的,从而控制测试模式:vio_ddr_1chl_cycle_NUM是每次读写DDR的地址次数,默认150次;vio_ddrcycle_test表示是否进行循环测试,循环测试为不间断连续进行读写测试;vio_ddr_test_start表示是否开始测试,1表示启动测试。

下面这些信号为错误检测信号,当程序出现错误时,对应通道的err_flag信号会拉高,表明当前通道的DDR出现的读写错误。

4、DDR4_logic_v1模块说明

DDR4 8通道读写逻辑控制,各个通道将请求存储在独立的异步FIFO,状态机轮询,存储rd_tag和通道号,待读数据返回时,读取rd_tag和通道号返回到各自通道。

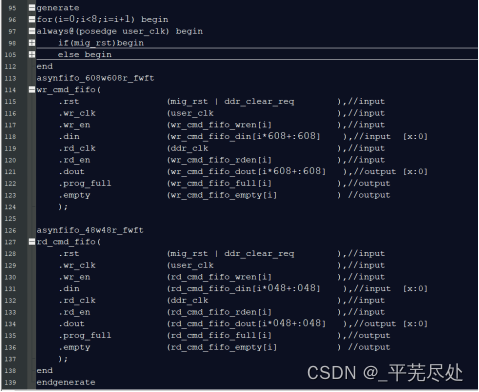

设计思路是首先会将读写请求进行解析分类,写请求存入wr_cmd_fifo中,读请求存入rd_cmd_fifo中,见下图。

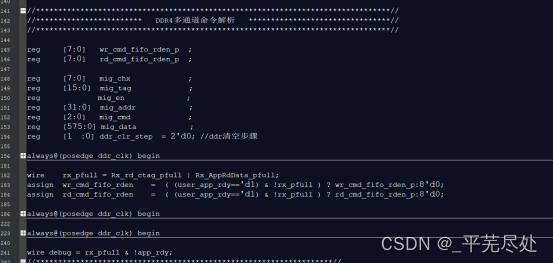

接下来需要进行读写命令解析,通过仲裁判断当前要处理哪个通道,产生当前通道号、命令、读写数据地址、写数据。

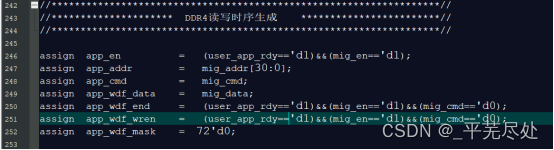

接下来生成DDR IP核读写时序。

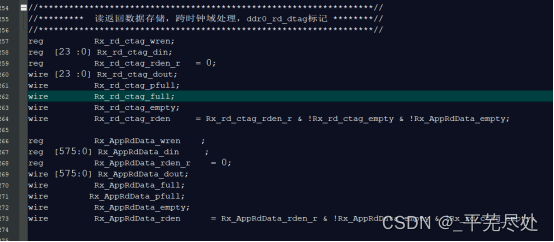

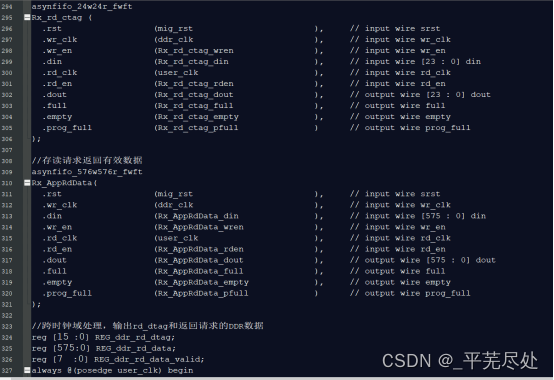

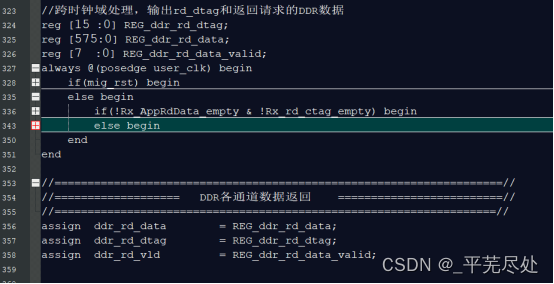

最后,需要进行读返回数据存储,进行跨时钟域处理,完成读写请求域与DDR 时钟域之间的数据传输。

同时记录读请求通道号和存储读返回有效数据

最后将返回的读数据分发到对应通道的读请求中,完成DDR的读访问。写操作的情况下不需要数据返回,因此直接写入DDR即可。

5、ddr4_mig_core模块说明

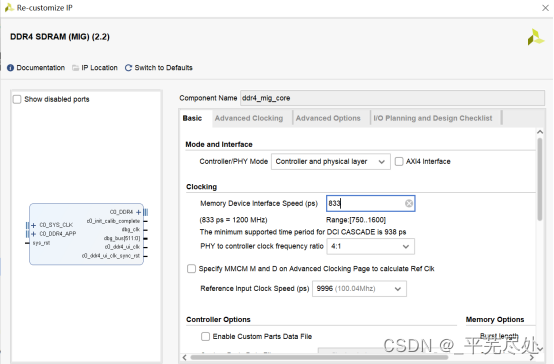

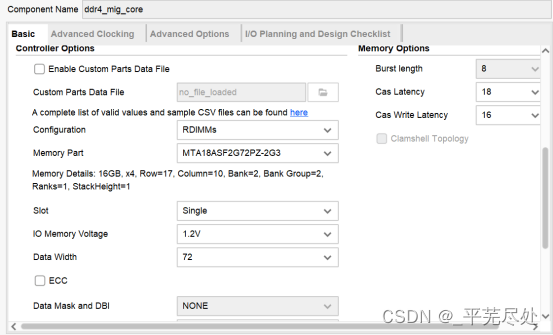

此部分主要是DDR IP核配置

配置DDR速率与时钟

配置DDR时序参数

其他信号默认即可。

487

487

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?