目录

一、设计要求

本次基于FPGA的示波器设计主要技术要求包含以下内容:

- 系统能够实现模数转换功能,即包含ADC驱动模块;

- 系统能够实现ADC采集数据的缓存功能;

- 系统包含辅助测试模块,DAC数模转换模块;

- 系统能够实现ADC数据和LCD液晶显示数据的转换功能;

- 系统具备LCD液晶显示功能;

- 附加项:系统具备波形的调频和调幅功能;

- 具备波形数据信息的显示功能,幅值、频率等;

二、系统架构设计

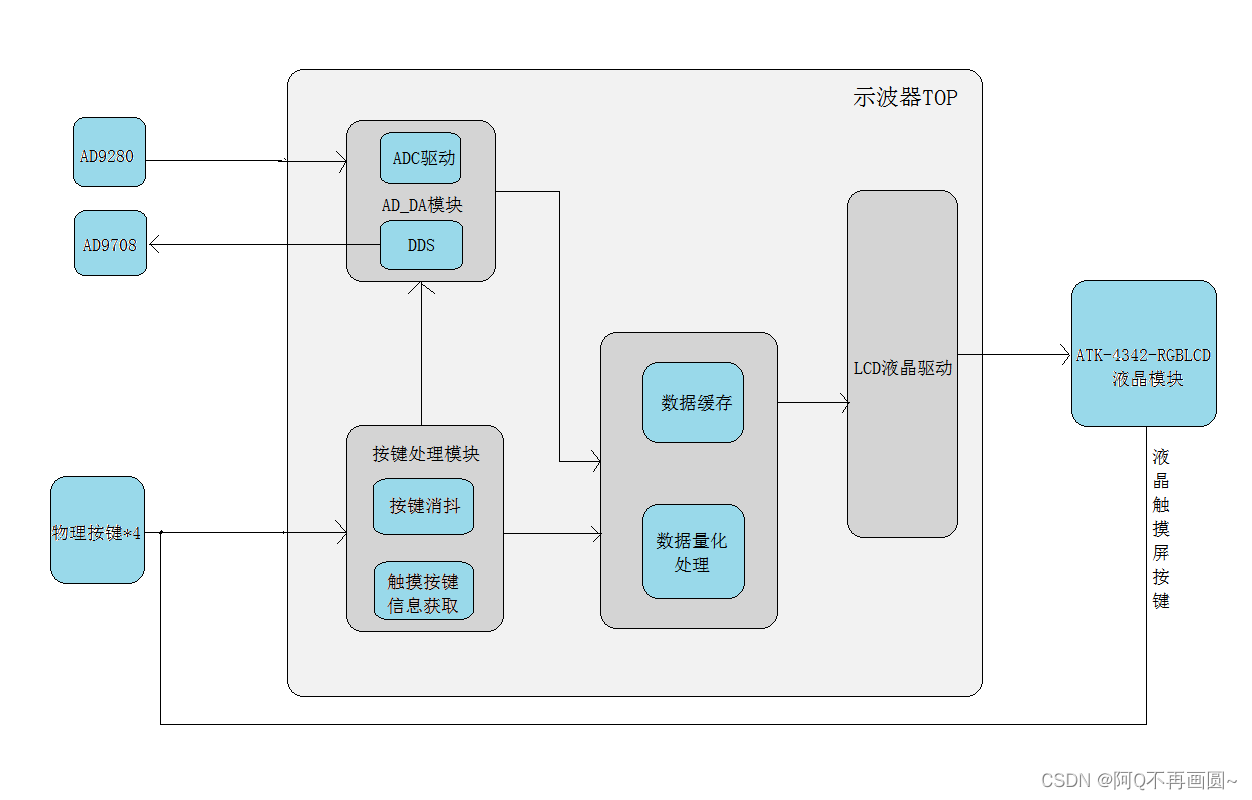

根据项目设计要求,将功能要求进行模块化,系统结构设计如图1所示。主要功能模块包括:

- AD_DA模块:主要功能驱动ADC9280模数转换模块,将模拟信号转换为数字信号,完成示波器的模拟信号的采集工作;驱动DAC9708数模转换模块,利用DDS技术实现简易信号发生器功能,此处添加该功能的目的主要是为了在没有模拟数据源的条件下进行示波器功能的辅助测试;

- 按键处理模块:该模块主要对物理按键进行边沿检测处理,完成按键消抖处理,正确获取按键信息;同时获取液晶触摸屏的触摸按键信息;

- 数据缓存&量化处理模块:该模块功能主要对AD采集的数据进行缓存,然后结合LCD液晶工作原理将AD数据进行转换,将ADC采集的模拟信号量在液晶屏上通过以波形的方式显示。

同时,模块包含频率计功能,将ADC采集信号的频率、幅值等信息进行计算,输出给LCD液晶驱动模块进行显示;除此之外,还可以根据液晶触摸按键信息将完成液晶波形显示的横纵坐标的缩放功能。 - LCD液晶驱动模块 :主要功能驱动液晶显示;

图1

三、模块设计

3.1 AD_DA模块设计

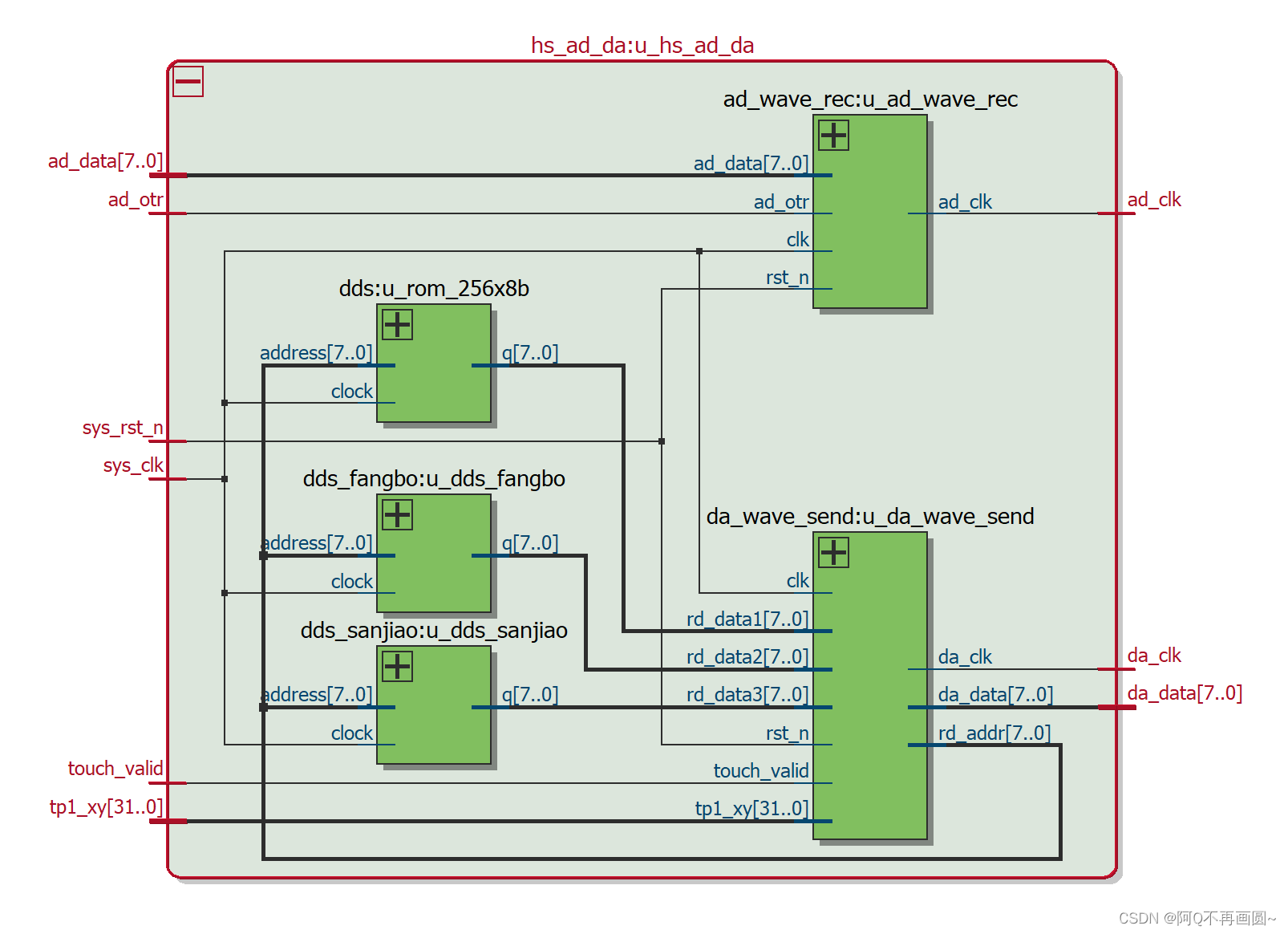

模块内部主要包含ADC9280驱动程序,以及DAC9708驱动程序,这两个模块较为常见,驱动程序简单。设计中ADC部分主要正确产生ad_clk,然后通过ad_clk对ad_data进行采样即可。有关DA驱动程序,设计中加入例如DDS内容,在ROM内部存储了正弦、三角、方波三种波形,波形可通过按键进行切换,频率、幅值均可调节。RTL级视图如图2所示。

图2

3.2 按键处理模块

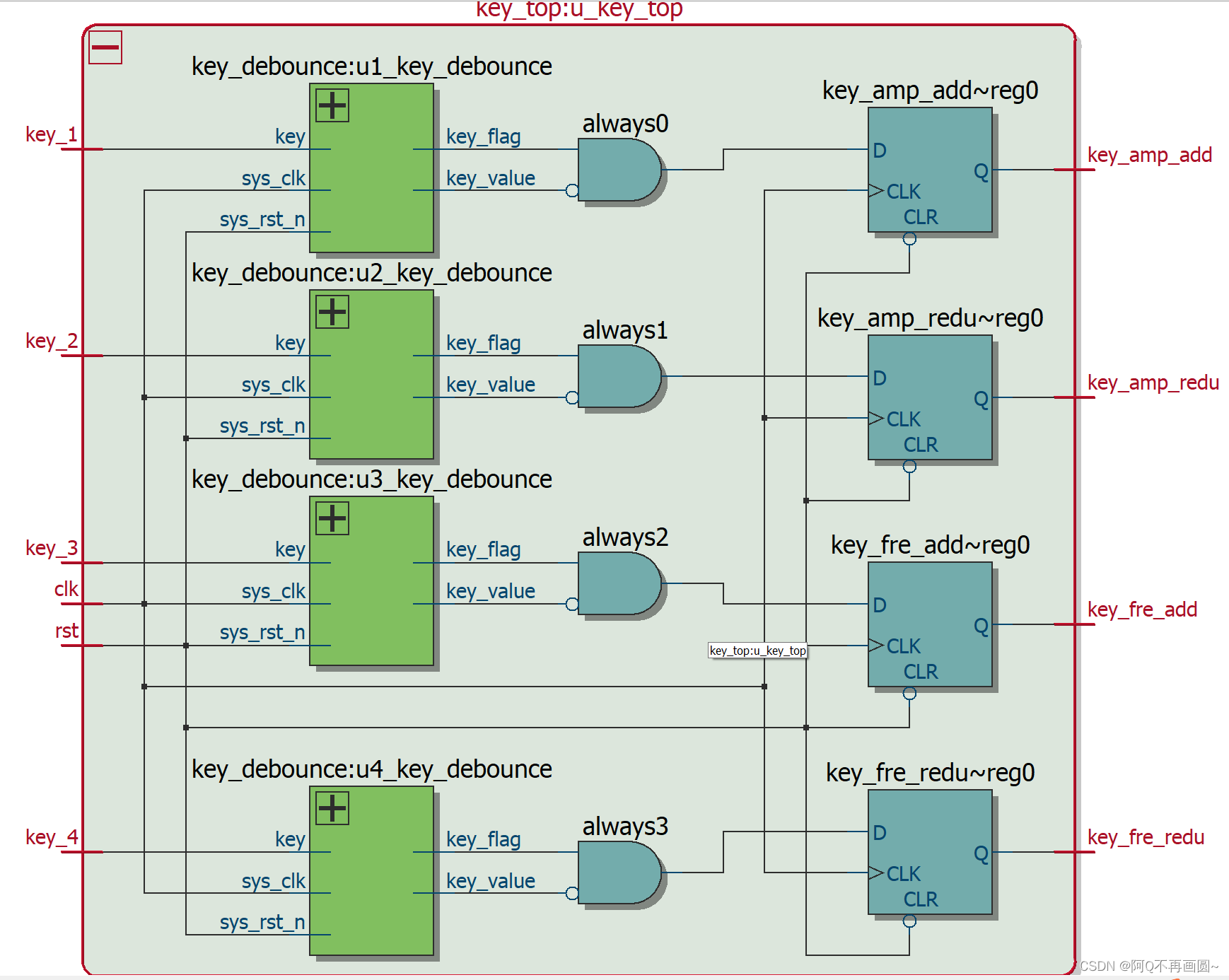

模块主要功能:主要分为两部分,第一部分将物理按键利用边沿检测技术,完成对按键信息的处理,准确的获取按键的上升沿或者下降沿脉冲。RTL级视图如图3所示。

图3

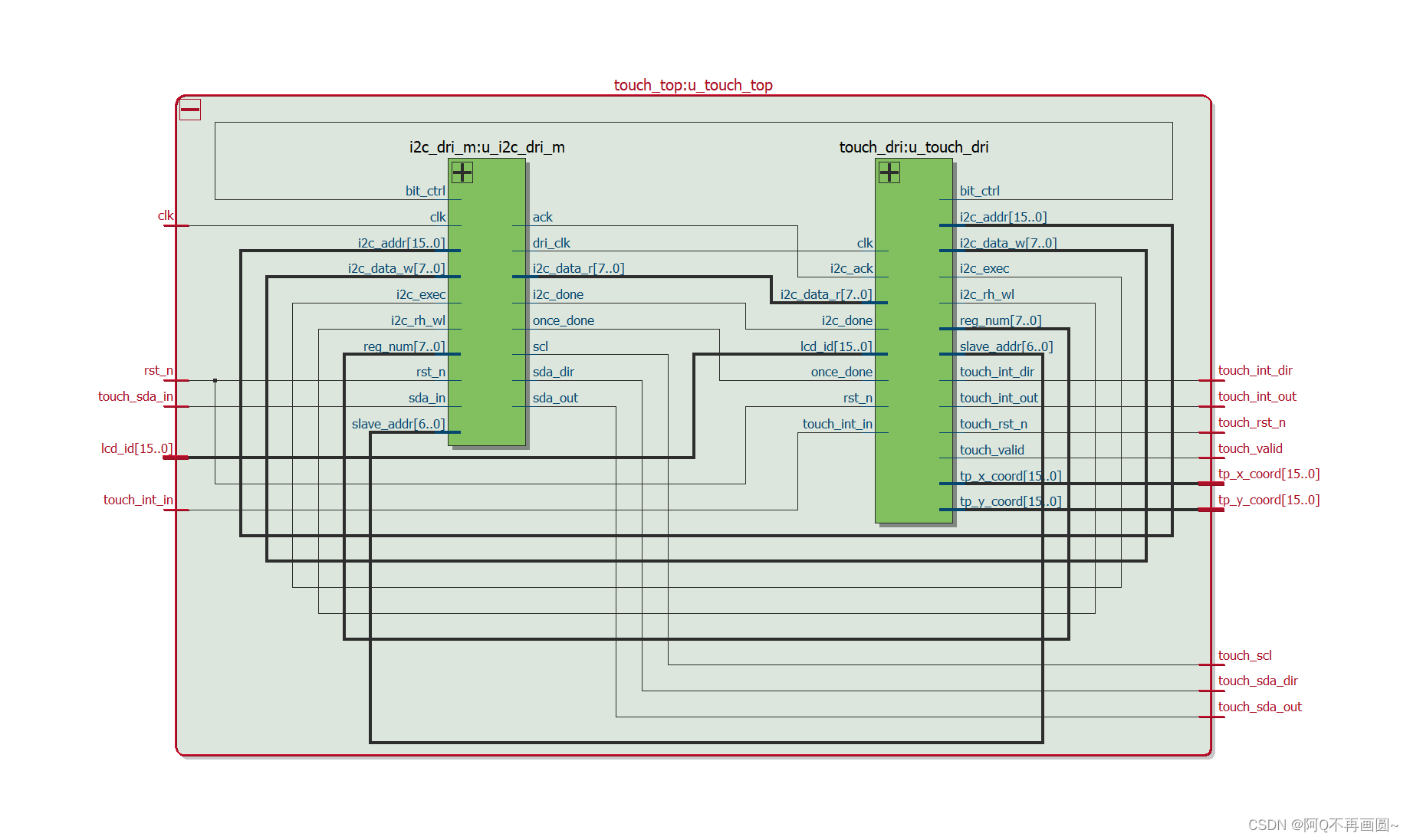

第二部分主要对液晶触摸按键信息进行正确的采集,如图4所示。

图4

3.3 数据缓存&数据量化模块

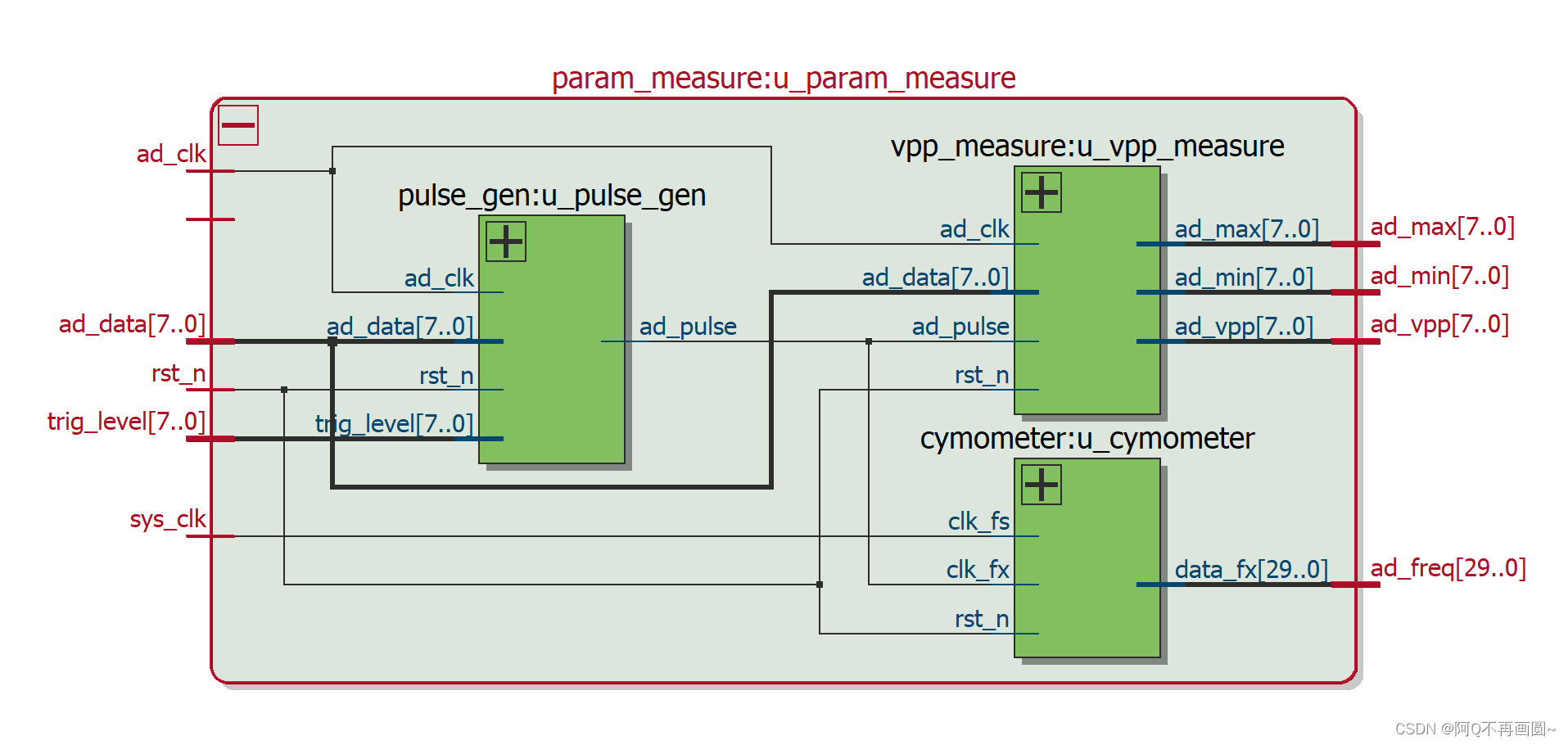

模块主要将ADC采集的信号进行缓存处理,然后结合LCD液晶显示的工作原理,完成量化处理,模块内部添加频率计,将采集信号的频率信息进行提取。同时还有采集信号的峰峰值、幅度等信息进行提取,输出给LCD液晶驱动模块。

图5

图5

3.4 LCD液晶驱动模块

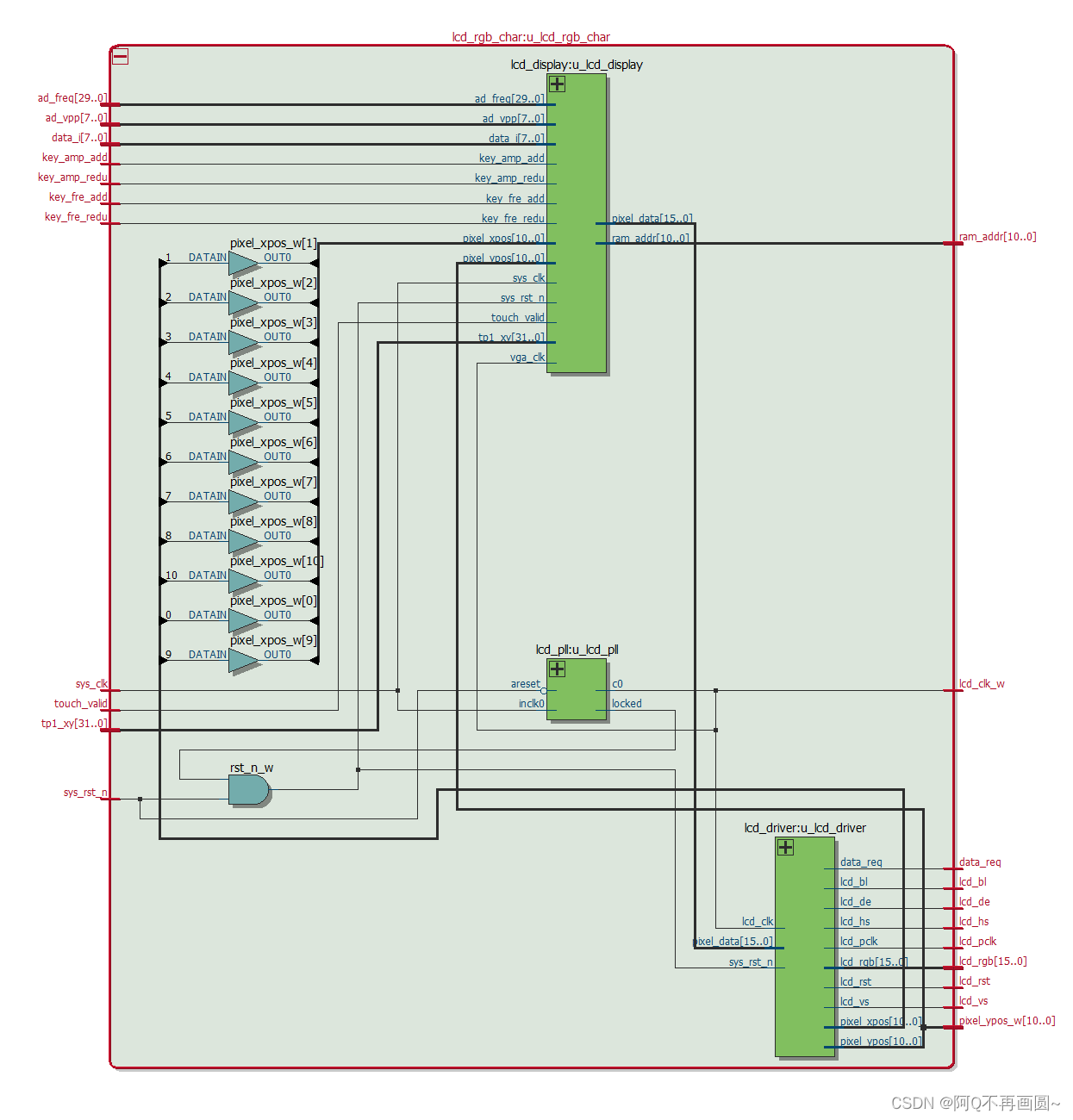

该液晶模块为RGB565格式的显示模块,驱动程序RTL级视图如图6所示。模块主要将ADC采集的数据完成画波形操作,将采集的数据映射到LCD液晶上完成显示,例如采集正弦波信号,在液晶显示屏上要能够直观的看见正弦波波形。

同时,结合液晶触摸按键,完成频率、幅值的刻度的增、减工作,实现波形的X\Y轴的调节工作。

图6

图6

四、方案验证

本次设计使用黑金的开发板AX515,如图7,以及黑金配套的ADC/DAC模块AN108模块如图8,还有LCD液晶模块(液晶要求:RGB888/RGB565,4.3寸,分辨率:480*272,含触摸屏按键功能)。此处开发板和液晶模块不做硬性要求,只要开发板外设能够链接ADC模块和液晶模块即可。

图7

图8

4.1 DA功能调试验证

功能测试过程中ADC采集的信号源是由板卡自身的DDS信号发生器提供,即DAC输出信号源直接介入ADC信号输入接口,DAC在线示波器SignalTap波形显示如图9所示,可以看见例化的三种波形工作均正常,输出选择可通过按键来进行选择。

图9

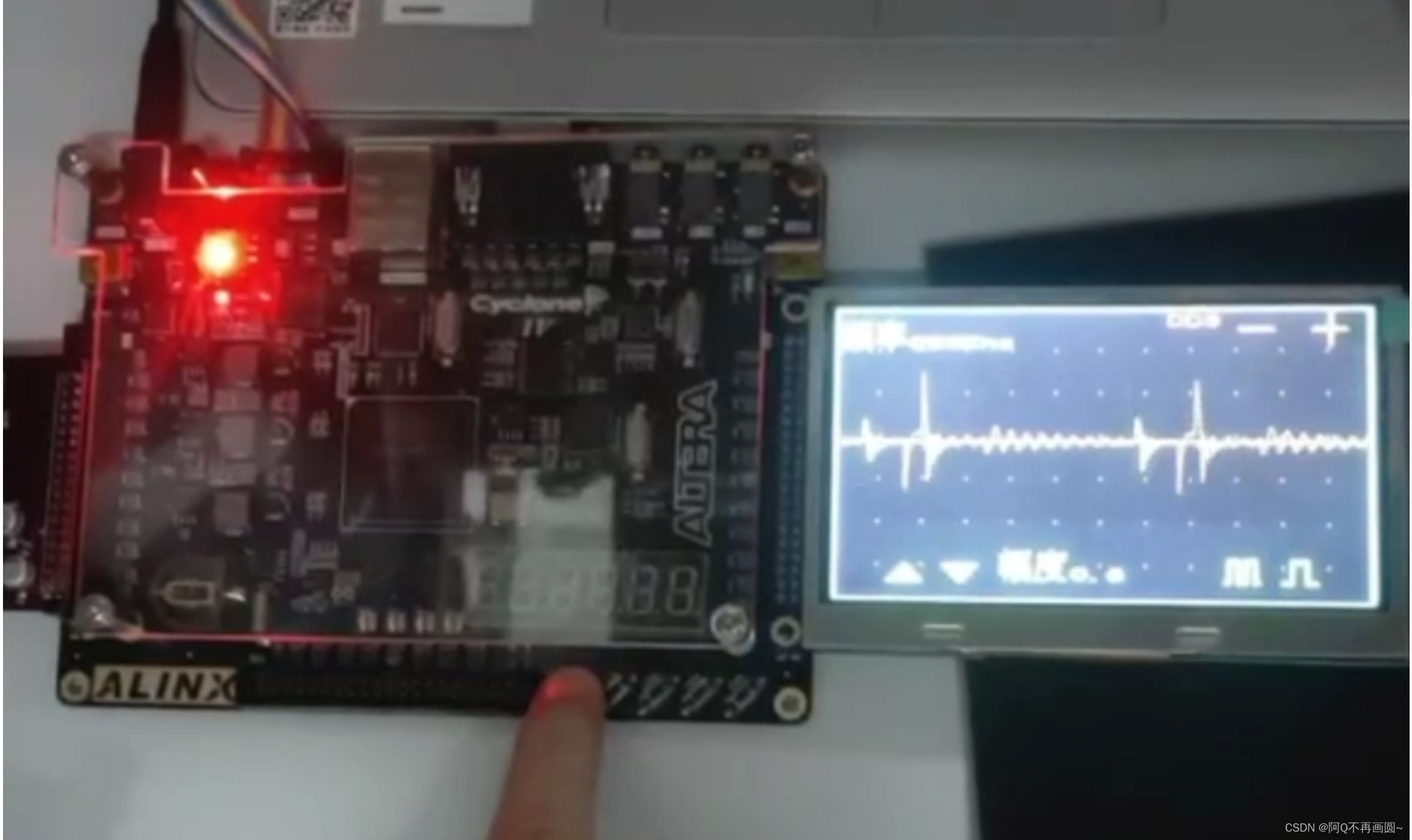

如下图10,为ADC不接任何信号时的噪声采集展示图,

图10

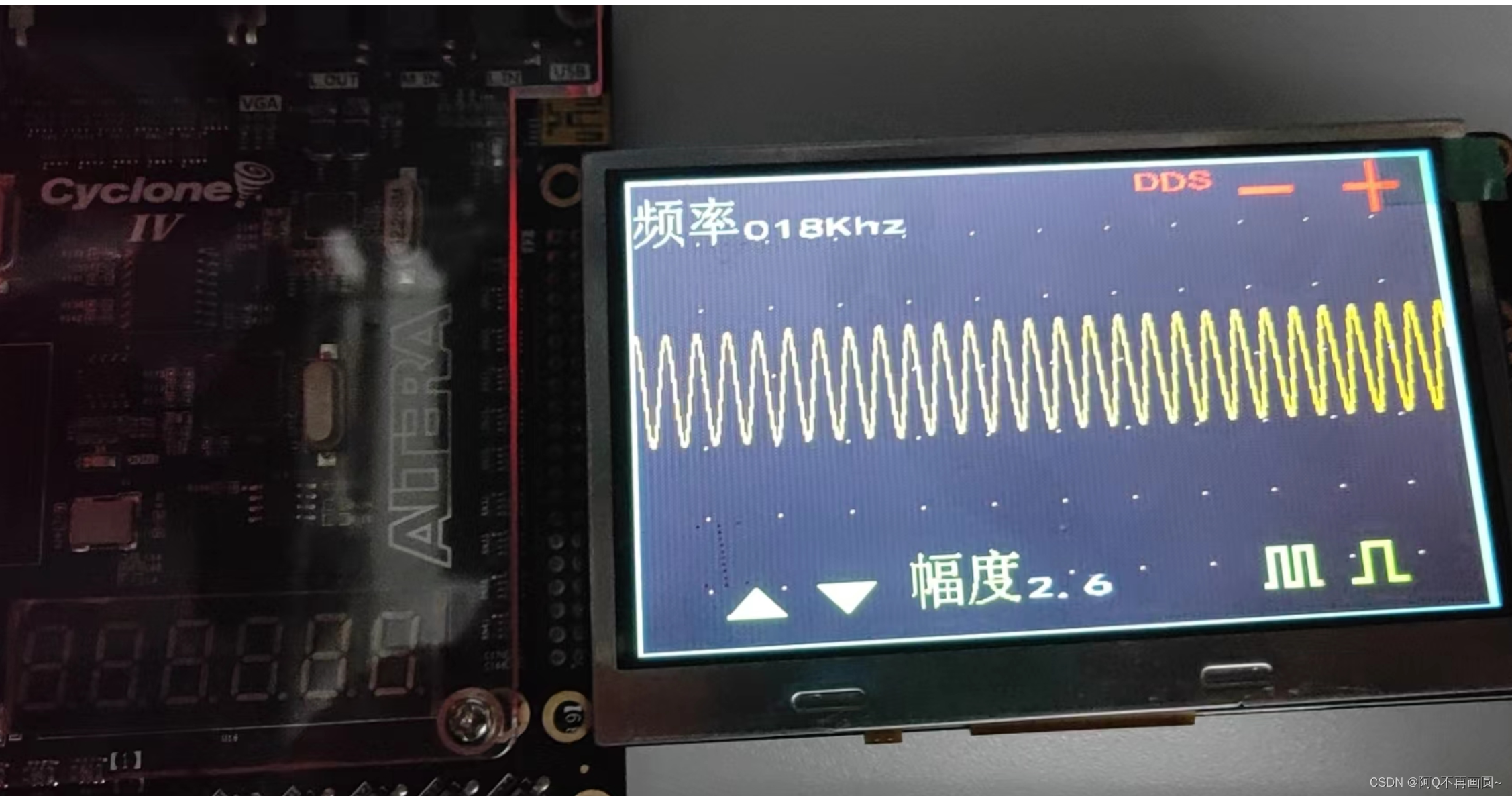

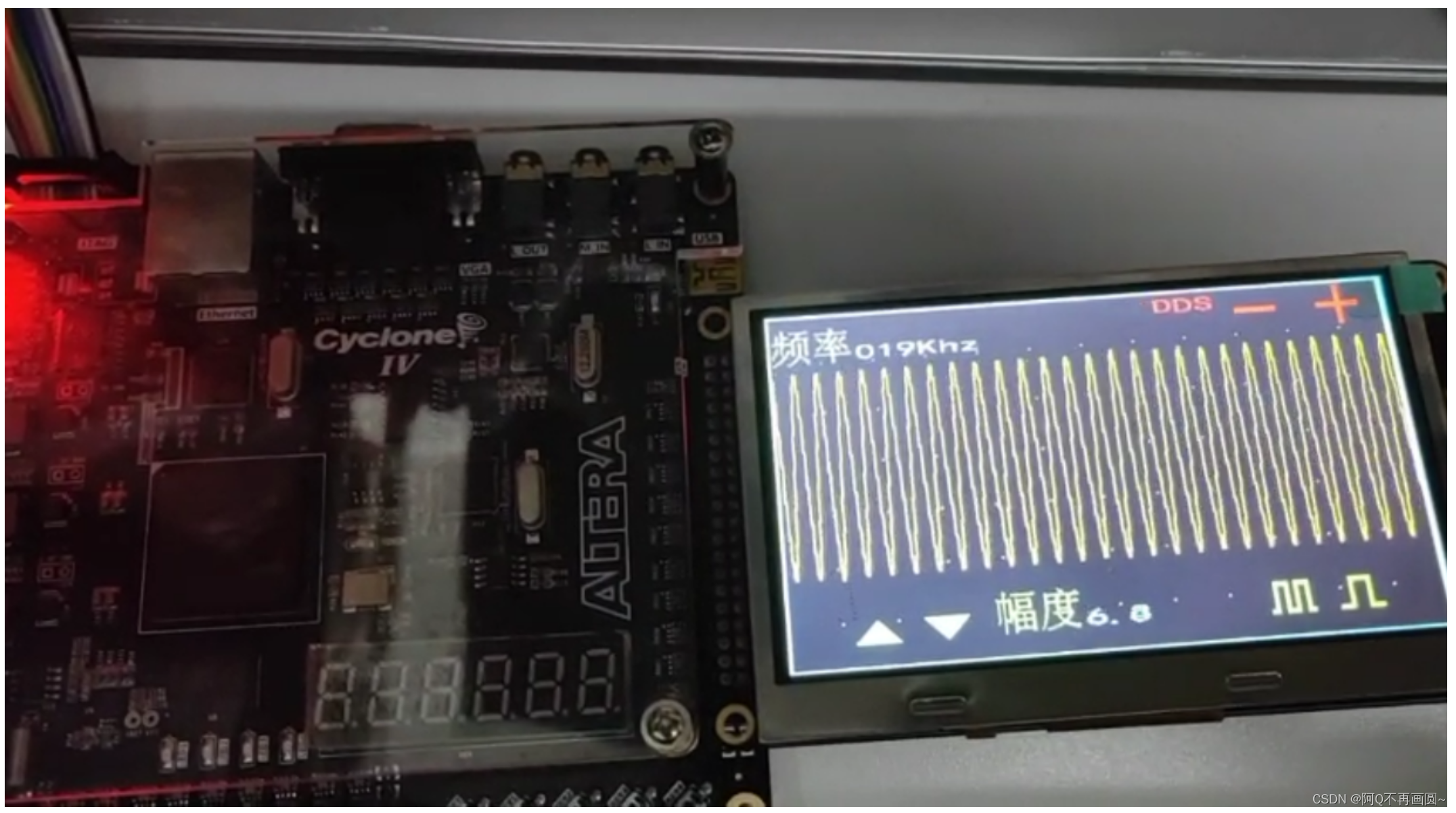

图11为ADC 接入DAC正弦波信号时的系统功能展示图,图中各种信息显示均正常。

图11

通过按键调节DAC输出波形幅值,ADC采集数据均有对应变化,系统功能初步验证完成,如图12所示。

图12

本文章只对设计架构和功能做简单的说明,程序具体实现内容较多,可自行下载对应程序进行深入学习理解,另外7寸液晶、VGA接口的配套例程均已调试通过,可私信进行具体问题具体交流。

2904

2904

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?