本次设计使用CMOD-S7和ICG-20330搭建一个基于FPGA的陀螺仪驱动系统,最终的设计要求有如下几点:

- 理解陀螺仪芯片工作原理;

- 正确使用FPGA驱动ICG-20330陀螺仪芯片,能够正常获取陀螺仪芯片的数据;

- FPGA正常采集陀螺仪芯片数据,完成陀螺仪芯片的数据整合工作;

- 通过串口将数据发送至上位机;

- 根据陀螺仪芯片的工作原理,将上位机数据正确转换成对应的X,Y,Z轴的角度等信息。

3.1 设计平台介绍

3.1.1 FPGA介绍

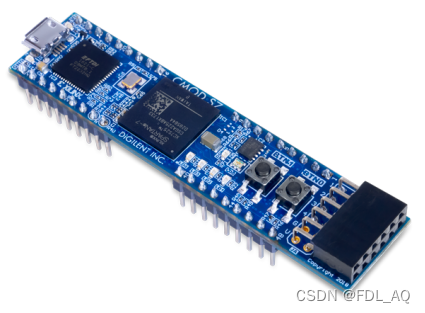

本次设计使用CMOD-S7功能开发板,FPGA主芯片为Spartan-7。Cmod S7是一款小巧的48引脚DIP板,采用36引脚,围绕Xilinx Spartan-7 FPGA构建。它有32个FPGA数字I / O信号,2个FPGA模拟输入信号,一个外部电源输入和接地线路连接到100毫英寸间距内,使Cmod S7非常适合与面包板一起使用。它只有0.7英寸×3.05英寸,可以方便的开发嵌入式系统。该板还包括编程ROM,时钟源,USB编程和数据传输电路,电源,LED和按钮,如图所1所示,位开发板实物图。

图1

3.1.2 陀螺仪介绍

本次设计陀螺仪芯片型号为ICG-20330,ICG-20330是一个3轴运动跟踪设备,包括一个3轴陀螺仪在一个小型的3x3x0.75毫米(16针LGA)包。

- 高性能规格

陀螺仪灵敏度误差:±1%o

陀螺仪噪声:5毫秒/Ö赫兹

- 包括512字节光纤来减少流量串行总线接口,并降低功耗通过允许系统处理器突发读取传感器数据,然后进入低功率模式

- EISFSYNC支持

- ICG-20330包括片上16位adc、可编程数字滤波器、嵌入式温度传感器和可编程中断。

- 该设备的工作电压范围低至1.71V。

- 通信端口包括I2C和7MHz的高速SPI。

该芯片常用于电话相机模块中的OIS(光学图像稳定),DSLR和DSC中

DSCEIS(电子图像稳定),以及电话相机模块等。

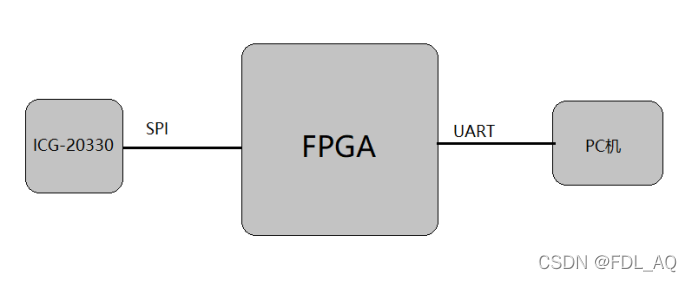

设计方案

本次设计使用CMOD-S7开发板结合ICG-20330陀螺仪芯片,设计架构如下图2所示:

图2

FPGA在设计中的主要功能:

- FPGA通过SPI总线驱动ICG-20330,使其正常工作;

- 获取ICG-20330数据,完成数据整理工作;

- 提供UART接口与PC机互联,完成数据上传;

ICG-20330陀螺仪设计中主要功能:

- 正常工作,内部将角度等信息准确进行采集存储;

- 对接SPI接口,和FPGA完成数据交互;

PC机在设计中的主要功能:

- 通过UART接口和FPGA对接,完成数据交互;

- 正确显示FPGA发送的数据,供设计这分析;

设计整体方案较为简单,难点集中在ICG-20330的驱动部分,这一部分需要结合数据手册,理解其工作原理,正确配置寄存器,最终获取所需求的数据。

4.1 FPGA架构设计

4.1.1 FPGA硬件架构设计

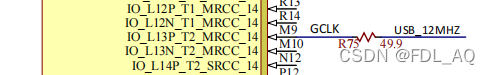

FPGA主时钟12MHz,用于给FPGA提供系统时钟,电路图3如下:

图3

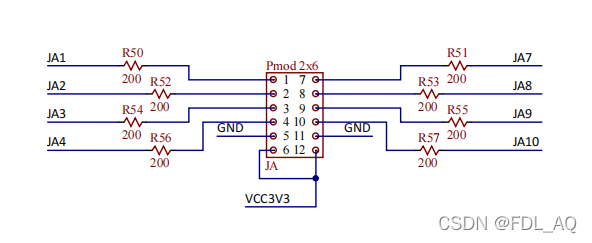

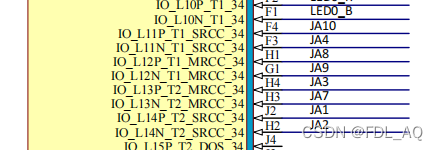

图4图5位Pmod2*6接插件,连接FPGA的IO管脚,可以通过该接插件连接ICG-20330,作为SPI接口使用。

图4

图5

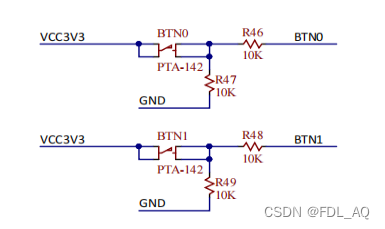

图6为按键电路,用于提供系统复位;

图6

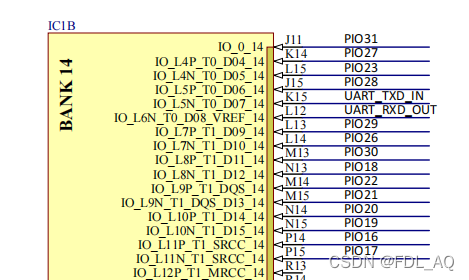

图7为串口电路设计,这部分设计在是共用USB-JTAG接口,使用micro-USB直接能够实现UART接口功能,且不影响其他功能。

图7

4.1.2 FPGA架构设计

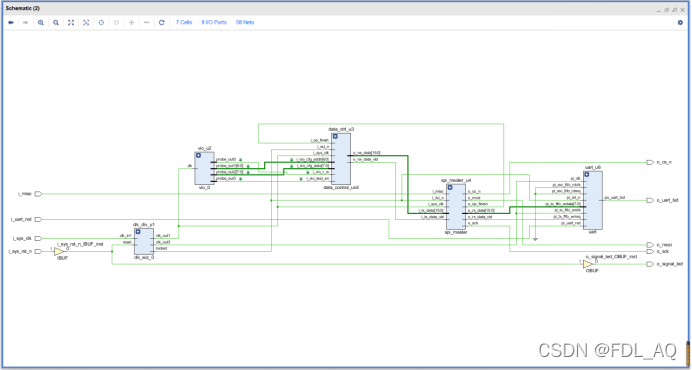

图8

如图8所示,为FPGA设计的RTL级视图,它能够后直观的看见顶层设计和内部结构设计。

首先,从图中我们可以看见顶层的管脚有:

- i_sys_clk : 系统时钟12MHz,用于给系统提供工作时钟;

- i_sys_rst_n:系统复位,低电平有效;

- i_miso:SPI总线信号,miso,对于FPGA来说属于输入信号;

- o_cs_n:SPI总线信号,片选信号;

- o_mosi:SPI总线信号,mosi,对于FPGA来说属于输出信号;;

- o_sck:SPI总线信号,SCK时钟;

- o_uart_txd:UART接口发送信号线;

- i_uart_rxd:UART接口接收信号线;

- o_signal_led:状态指示等;

其次,内部的各个模块的功能如下:

- clk_div:时钟分频模块,系统时钟输入12MHz,在内部架构中,每个单独的模块,都需要单独的主时钟,这样以来PLL锁相环就能够通过倍频和分频,完成这一项工作,由12MHz产生不同频率的时钟,共给各个模块使用;

- Vio模块:该模块是调用FPGA内部的IP核,其作用是用于调试,辅助观察内部各信号的实时状态;

- data_ctrl:该模块主要用于产生ICG-20330所有需要配置的寄存器地址和数据,控制寄存器的读写,结合SPI总线,控制对ICG-20330的读写操作;

- SPI_master:SPI接口的时序模块,用于模拟SPI协议的时序,最终控制mosi、miso、cs、sck四条信号的时序;

- Uart模块:UART接口时序控制模块,用于模拟UART协议的时序,进而完成和PC机的数据交互工作;

4.1.3 FPGA内部模快功能

关于FPGA内部的整体功能可以划分为两部分,数据采集,整理和发送;数据采集主要至对ICG-20330的状态数据采集;发送主要指通过UART和上位机进行通信。

- 数据采集

关于数据采集,研究的重点在与对ICG-20330的数据手册的研读理解,了解其工作原理和特性。

寄存器配置

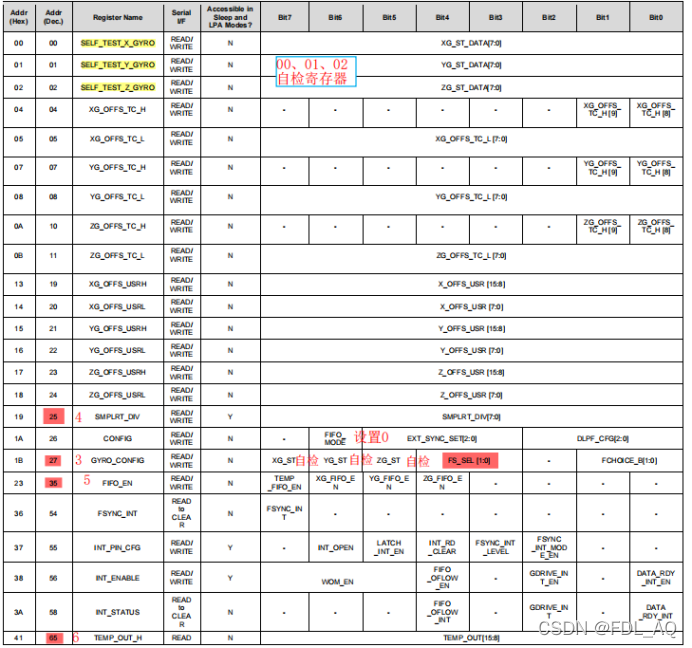

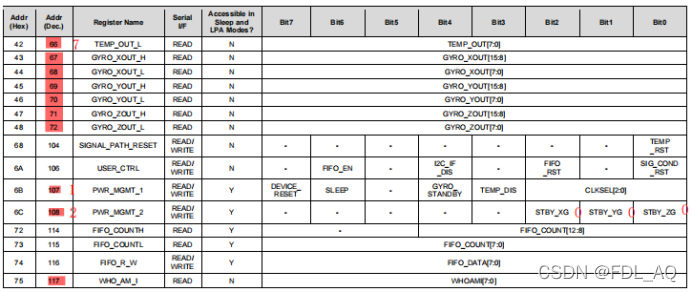

通过数据手册可以知道,ICG-20330工作在上电后需要进行寄存器初始化,具体操作为按照一定的顺序配置其内部的寄存器。如图所示,为寄存器列表,列表中的寄存器分为可读可写寄存器,和只读寄存器;可读可写的寄存器可以配置芯片工作的模式,完成一些主要状态的参数补偿,比如软复位寄存器(PWR_MGMT_1

),该寄存器是芯片内部的软复位寄存器,我们可以往里面写入数据,也可以从该寄存器内读取写入的数据,以此来验证寄存器配置是否正常;只读寄存器,比如ID号寄存器(WHO ARM I),该寄存器为只读寄存器,它主要的功能就是提供芯片的ID信息,本次使用的ICG-20330的ID号为68或69,这个在数手册中有明确的体现;如表1,表2。

表1

表2

根据设计要求,途中标红的寄存器都是我们需要配置操作的寄存器,在设计中需要按照一定的顺序完成配置操作;下图中代码中就是本次设计寄存器配置顺序,除了上电复位有硬性要求,其他的寄存器顺序没有具体要求;这一部分设计是在data_ctrl这个模块中实现的。

图9

如上图9代码中所示,设计中操作配置的寄存器有:

- PWR_MGMT1<-->(READ/WRITE)--复位:由于系统上电之后,需要进行内部复位,才能正常工作,该寄存器的配置需要先配置复位,然后再还原,处于非睡眠模式,使其能够正常工作;

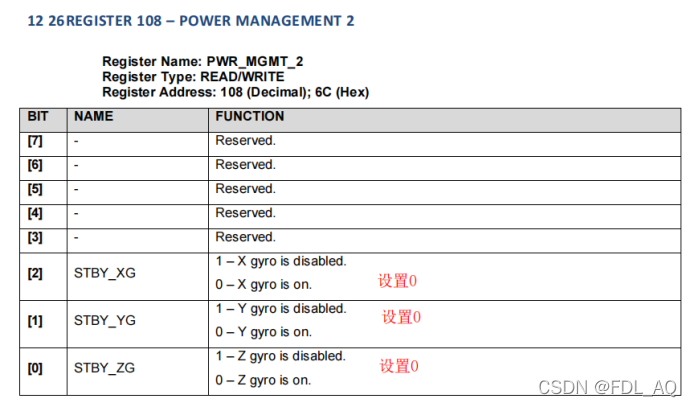

- PWR_MGMT_2<-->(READ/WRITE):该寄存器需要使三轴陀螺仪正常工作,[2:0]=3’b000;

图10

- SMPLRT_DIV<-->(READ/WRITE):采样率配置寄存器,该寄存器控制芯片工作时的采样率;

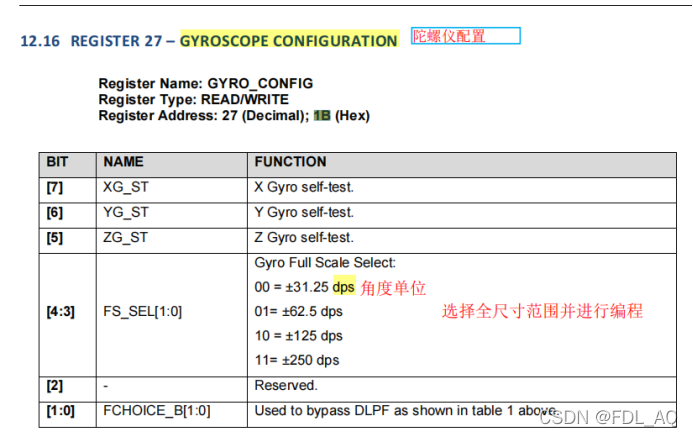

- GYRO_CONFIG<-->(READ/WRITE):陀螺仪配置寄存器,配置角度范围。

图11

- FIFO_EN<-->(READ/WRITE):FIFO使能寄存器,使能FIFO,允许新数据代替FIFO中的旧数据;确保数据的实时性;

- TEMP_OUT_H<-->(READ):ICG-20330温度数值高8bit;

- TEMP_OUT_L<-->(READ):ICG-20330温度数值低8bit;

- GYRO_XOUT_H<-->(READ):ICG-20330的X轴角度数值高8bit;

- GYRO_XOUT_L<-->(READ):ICG-20330的X轴角度数值低8bit;

- GYRO_YOUT_H<-->(READ):ICG-20330的Y轴角度数值高8bit;

- GYRO_YOUT_L<-->(READ):ICG-20330的Y轴角度数值低8bit;

- GYRO_ZOUT_H<-->(READ):ICG-20330的Z轴角度数值高8bit;

- GYRO_ZOUT_L<-->(READ):ICG-20330的Z轴角度数值低8bit;

- WHO_ARM_I<-->(READ):芯片ID号;

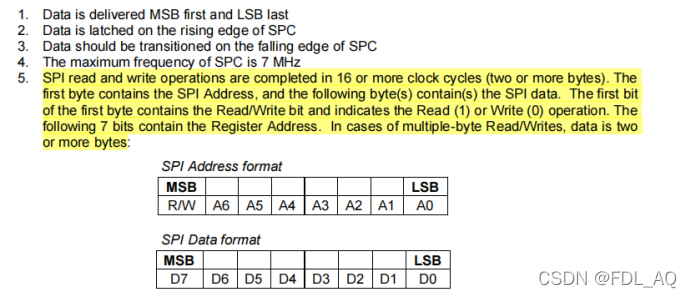

根据SPI总线设计要求,SPI读写操作通过16个或更多时钟周期(两个或更多字节)完成。第一个字节包含SPI地址,之后的字节包含SPI数据。第一个字节的第一位包含读/写位,并表示读(1)或Write(0)操作。以下7位包含注册器地址。在多字节读取/写入的情况下,数据是两个或多个字节。

因此,我们在data_ctrl模块中的data_reg位宽设计为16bit,其构成{1bit读写标志,7bitaddress,8bit数据};

图12

SPI总线设计

要完成ICG-20330的控制,我们需要使用SPI接口,当然也可是使用IIC接口,两者均可以,本次设计我们使用SPI,优点为速度较快,在完成一主多从的设计时比较方便控制。

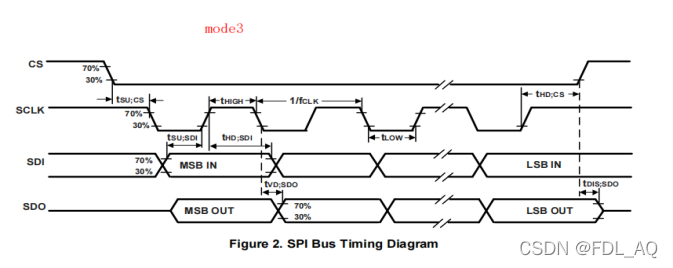

首先,我们需要确定SPI的模式。我们知道SPI根据极性和相位的不同可以分为四种模式,mode0-mode3;

CPOL(极性) CPHA(相位)

MODE0 0 0

MODE1 0 1

MODE2 1 0

MODE3 1 1

CPOL: SPI空闲时的时钟信号电平(1:高电平, 0:低电平);

CPHA: SPI在时钟第几个边沿采样(1:第二个边沿开始, 0:第一个边沿开始);

根据ICG-20330数据时序图可以知道,本次设计SPI模式我们使用mode3。

图13

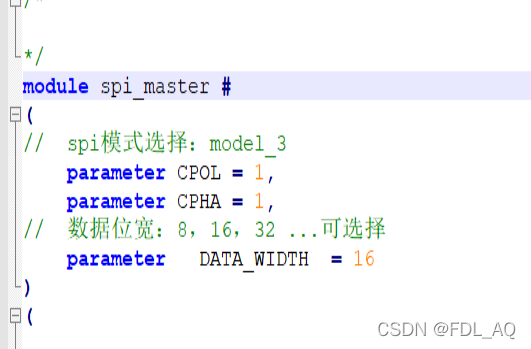

因此在代码中我们将模式按照数据手册要求进行设计,如下图,该SPI模块已经完成了封装,通过更改参数即可完成模式的修改;

图14

其次,我们要确定SPI协议的处理数据位宽为16位,这个一定要和我们的data_char模块对应,否则会出现数据传输异常的情况。

- 数据整理

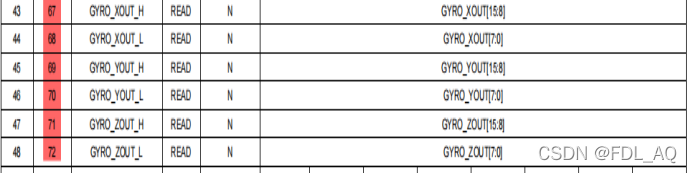

根据设计需求,我们需要获取ICG-20330的三轴的角度信息,在完成ICG-20330初始化之后,我们需要从寄存器ox67~0X72这六个寄存器中读取X、Y、Z三个轴的角度信息,这六个寄存器分辨代表X、Y、Z轴的数据高8位和滴8位,其中最高位为符号位。

图15

获取数据完毕后进行数据整理,由于SPI获取到16bit数据时,包含地址和数据,这边设计为了区分X、Y、Z三轴的数据,特意在传输数据过程中,做了数据标记。传输数据时按照X-Y-Z这个顺序进行传输,并且在三轴数据之前做了区分。

具体方法为传输时添加关键标志,在发送数据时先发送F1(X轴数据标志)-X轴高八位数据-X轴低八位数据-F2(Y轴数据标志)-Y轴高八位数据-Y轴低八位数据-F3(Z轴数据标志)-Z轴高八位数据-Z轴低八位数据。

这样一来,就能够很清晰的完成数据的区分,数据传输到上位机之后很容易就能够区分开来。

图16

- 数据发送

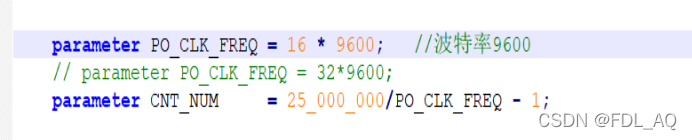

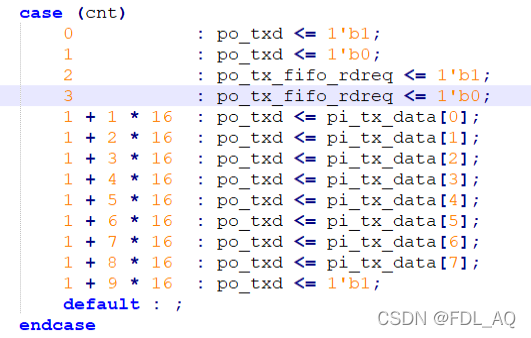

这部分主要指FPGA通过UART往上位机发送数据,设计需要注意UART协议的波特率设置,本次我们使用的波特率为9600,8为数据,无校验。

图17

图18

整理好的数据存放在FIFO中,TDX拉低之后使fifo的读使能信号拉高一个时钟周期,从fifo读取数据,然后通过串口发送出去,如上图18所示,按照8bit,无校验完成uart的txd信号发送。

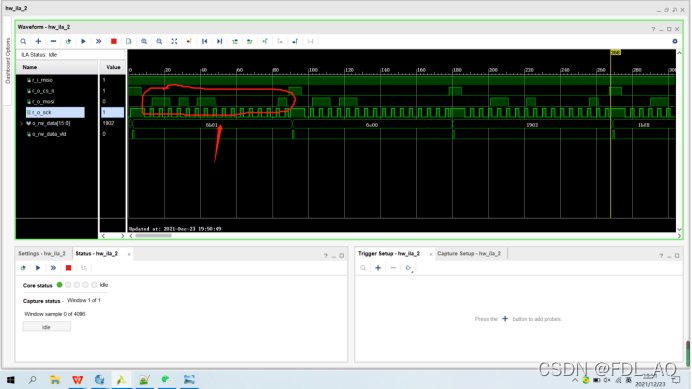

5.1 ICG-20330调试

通过添加在线逻辑分析仪,抓取相关信号,观察信号状态,如下图,为SPI总线的时序观测界面,其中配置数据为0X6b01,转化为2进制0110101100010000

观察mosi波形,和配置数据完全匹配;观察相位和极性,确定SPI模式为MODE3。

因此,该SPI时序设计正确。

图19

5.3 本章总结

本章通过对采集和发送两个最主要的部分进行调试。调试过程中借助VIVADO内部调试工具,可以很清晰直观的看到SPI时序和内部主要信号的状态是否正确。

目前我们能够直观看见SPI时序和寄存器配置部分已经完成,接下来就是FPGA从陀螺仪芯片中读取数。

程序代码及相关文档链接。

:基于FPGA的ICG-20330陀螺仪芯片的驱动程序及相关文档-嵌入式文档类资源-CSDN下载

1078

1078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?