SDRAM介绍

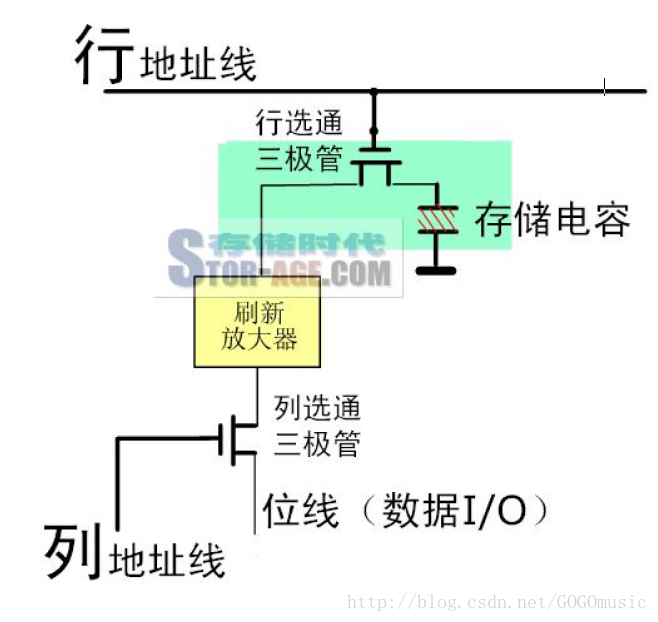

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证存储的数据不丢失,因为SDRAM中存储数据是通过电容来工作的,大家知道电容在自然放置状态是会有放电的,如果电放完了,也就意味着SDRAM中的数据丢失了,所以SDRAM需要在电容的电量放完之前进行刷新;随机是指数据不是线性依次存储,而是自由指定地址进行数据的读写

SDRAM结构

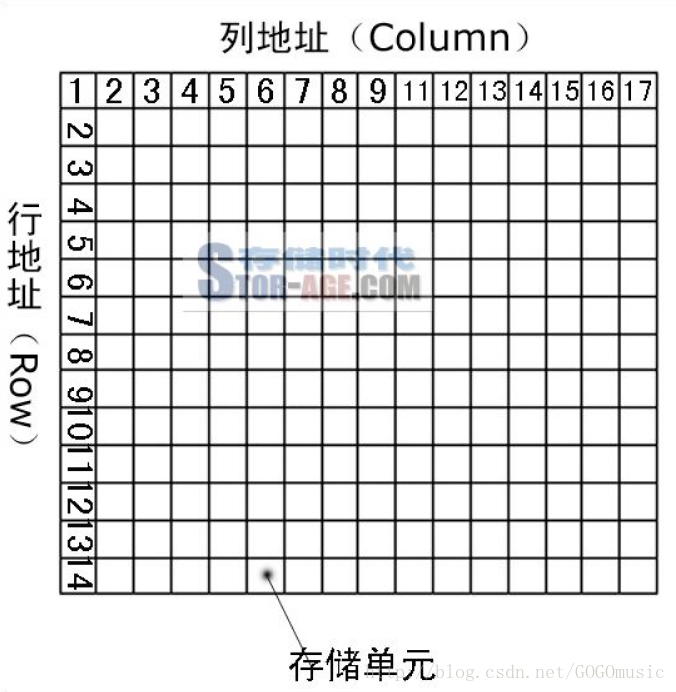

SDRAM容量=数据位宽x存储单元数量(BANK数x行地址x列地址)

(数据位宽等于存储单元中存储数据的宽度)

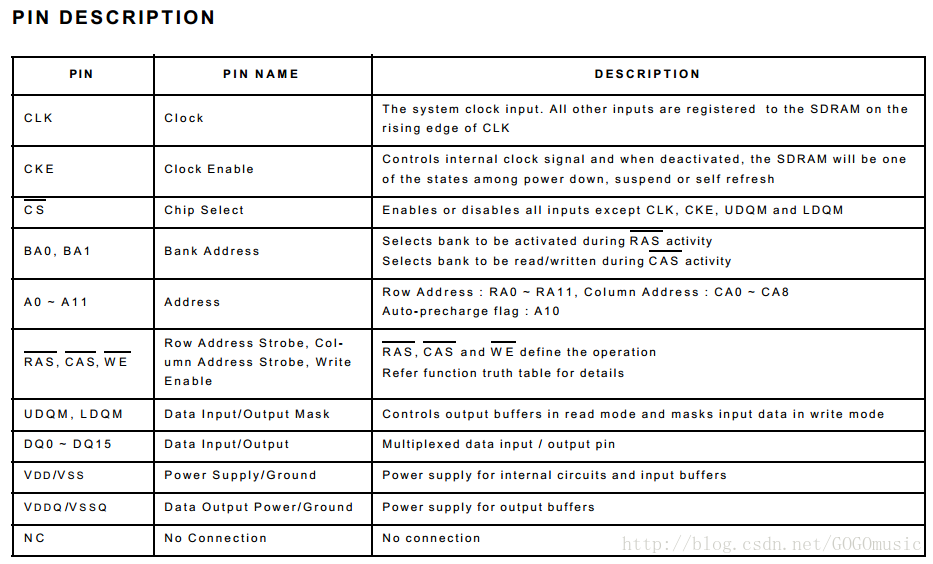

SDRAM芯片引脚介绍

1、首先,我们知道内存控制器要先确定一个P-Bank 的芯片集合,然后才对这集合中的芯片进行寻址操作。因此要有一个片选的信号,它一次选择一个P-Bank 的芯片集(根据位宽的不同,数量也不同)。被选中的芯片将同时接收或读取数据,所以要有一个片选信号。

2、接下来是对所有被选中的芯片进行统一的L-Bank 的寻址,目前SDRAM 中L-Bank 的数量最高为4 个,所以需要两个L-Bank 地址信号(=4)。

3、最后就是对被选中的芯片进行统一的行/列(存储单元)寻址。地址线数量要根据芯片的组织结构分别设计了。但在相同容量下,行数不变,只有列数会根据位宽的而变化,位宽越大,列数越少,因为所需的存储单元减少了。

4、找到了存储单元后,被选中的芯片就要进行统一的数据传输,那么肯定要有与位宽相同数量的数据I/O通道才行,所以肯定要有相应数量的数据线引脚。

CLK:SDRAM工作的时钟,并且所有的输入信号都是在CLK的上升沿进行检测的,也就是说我们给SDRAM给的任何命令,一定要在CLK的上升沿保持稳定,以免SDRAM获取我们给出的命令时出现错误。

CKE:时钟使能信号,是用来控制SDRAM内部时钟是否工作的一个信号(在SDRAM内部也是有时钟的哦)

CS:片选信号,这里需要注意的是,如果要对SDRAM进行操作,必须要将片选信号拉低

BA0,BA1:Bank地址线,用来给bank的地址,可以控制SDRAM的4个bank

A0~A11:地址线,当我们选择SDRAM某个Bank的Row地址的时候,需要到12根地址线(A0~A11);当选择Col地址的时候,只用A0~A8这9根线;A10这个信号可以用来控制Auto-precharge。

RAS、CAS、WE:这三根线就是用来给SDRAM发命令的,包括初始化、读、写、自动充电等命令。

UDQM、LDQM:数据输入/输出掩码。

DQ0~DQ15:SDRAM的数据线,为双向的,向SDRAM写数据或者从SDRAM中读出来的数据都是在DQ上进行传输的

地址线

• A0~A11:地址线,当我们选择SDRAM某个Bank的Row地址的时候,需要到12根地址线(A0~A11);当选择Col地址的时候,只用A0~A8这9根线;A10这个信号可以用来控制Auto-precharge

• SDRAM的厂商一般为了节约成本,采用同一总线来对SDRAM进行寻址是无可厚非的,对于Row地址用到了12根线,也就是总共有2^12=4096个Row地址,而col地址使用9根线,也就是有2^9=512个col地址

掩码

• 就拿咱们使用的这块SDRAM芯片来讲,数据线有16根,也就是说明我们数据的位数可以达到16位,但是呢,请注意,也许在我们使用SDRAM的时候,也许我们在向SDRAM写数据的时候,我们生成的数据只有8位,但FPGA是与SDRAM的16根数据线连在一起的,这个时候,存到SDRAM中的数据还是16位的,所以为了避免这个问题,我们就可以使用掩码来屏蔽掉高8位了。当然掩码在读数据的时候起到的作用也是类似的。

预充电

L-Bank 关闭现有工作行,准备打开新行的操作就是预充电(Precharge)

实际上,预充电是一种对工作行中所有存储体进行数据重写,并对行地址进行复位,同时释放S-AMP(重新加入比较电压,一般是电容电压的1/2,以帮助判断读取数据的逻辑电平,因为S-AMP 是通过一个参考电压与存储体位线电压的比较来判断逻辑值的),以准备新行的工作。

电容的电量(或者说其产生的电压)将是判断逻辑状态的依据(读取时也需要),为此要设定一个临界值,一般为电容电量的1/2,超过它的为逻辑1,进行重写,否则为逻辑0,不进行重写(等于放电)。为此,现在基本都将电容的另一端接入一个指定的电压(即1/2 电容电压),而不是接地,以帮助重写时的比较与判断

刷新

• 为什么有预充电操作还要进行刷新呢?

• 因为预充电是对一个或所有L-Bank 中的工作行操作,并且是不定期的,而刷新则是有固定的周期,依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。

那么要隔多长时间重复一次刷新呢?目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000 秒),也就是说每一行刷新的循环周期是64ms。这样刷新速度就是:行数量/64ms。我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms 或8192 Refresh Cycles/64ms 的标识,这里的4096 与8192 就代表这个芯片中每个L-Bank 的行数。刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096 行时为15.625µs(微秒,1/1000 毫秒),8192 行时就为7.8125µs。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?