我在Quartus II 13.1写了一个加法器,程序如下

`timescale 1ns/1ns

module Counter_Design

(

//global clock

input clk, //50MHz

input rst_n,

//user interface

output reg [3:0] cnt

);

//----------------------------

//Counter for 4 bit data

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 0;

else

cnt <= cnt + 1'b1;

end

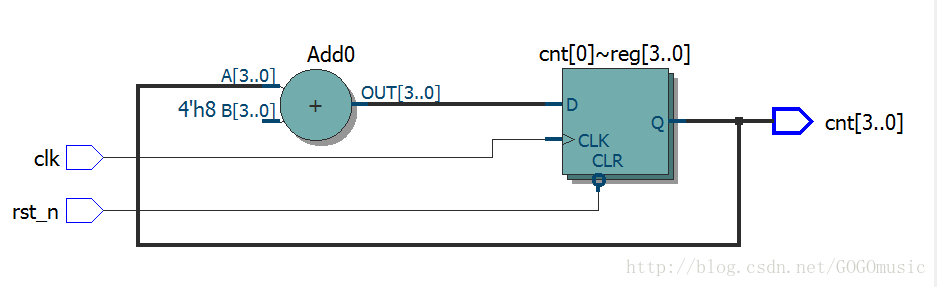

endmodule所生成的RTL视图如下:

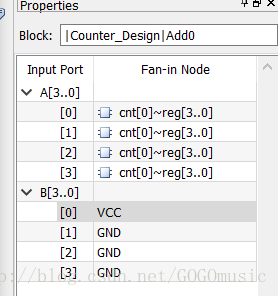

在加法器中cnt的值应每次加一,而在RTL视图中出现了B[3:0]为4’h8的情况,本以为这里应为4’h1。后来经过细致观察发现,点开RTl视图左边的B[3:0]属性发现 B[0]位为高,其他位为低,因此推断B在这里应为一个选择信号,并不是cnt要加的数,B[3..0]的4’h8只是选择cnt的第0位加1。

339

339

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?