上面的设计提示仅以"MK-米客方德"的SD NAND为准

注:不同的SD NAND 工作电流不一样,请注意电源供电能力和稳定性。

电源和GND之间的电容是为了上电和断电时,芯片能正常工作,电容过大或者过小都会影响芯片的功能

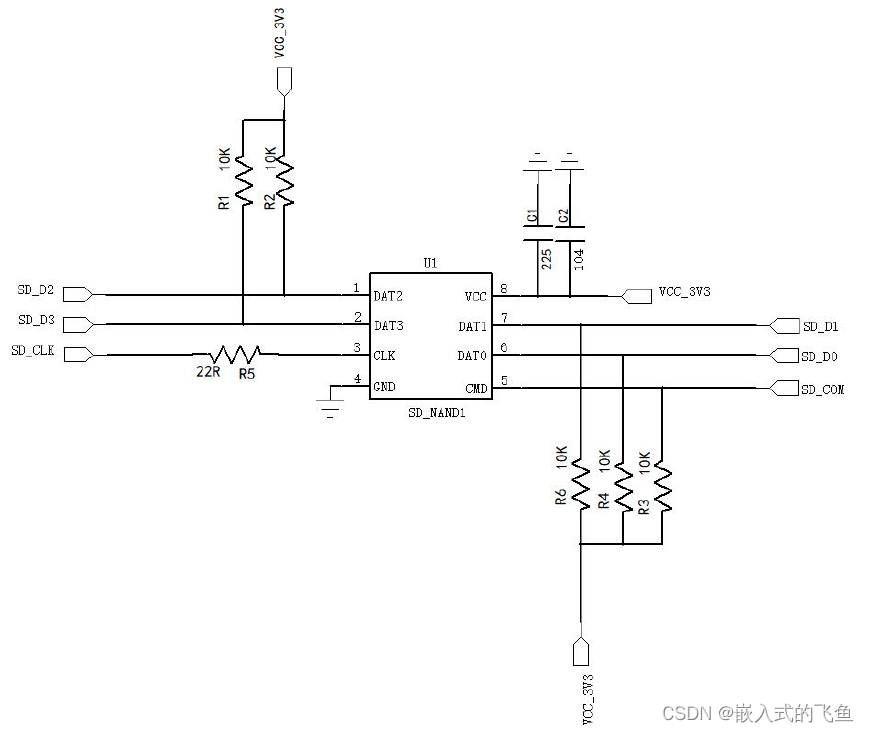

SD NAND 的DAT3引脚上拉为SPI模式,不接上拉默认为SDIO模式,所以上面的参考电路图是SD NAND的SPI参考电路

其他引脚的上拉电阻是为了保证信号的稳定性,主控芯片内部有上拉的引脚可以不额外上拉,

Layout 设计说明

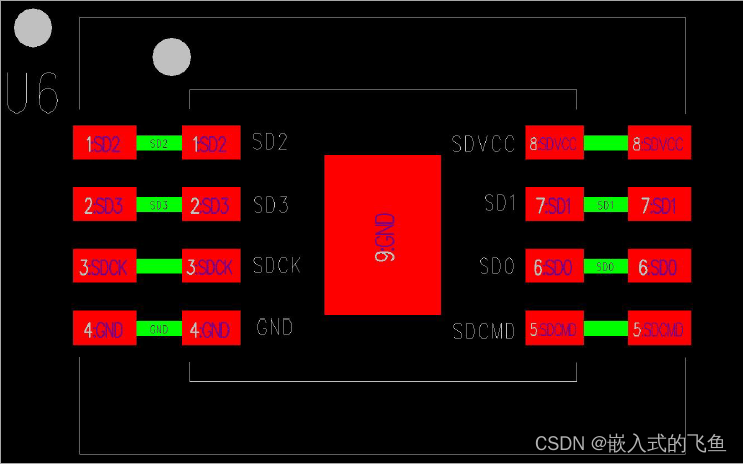

① MK-米客方德的SD NAND有两种封装,9* 12mm和6*8mm,下面是两种封装的兼容性设计

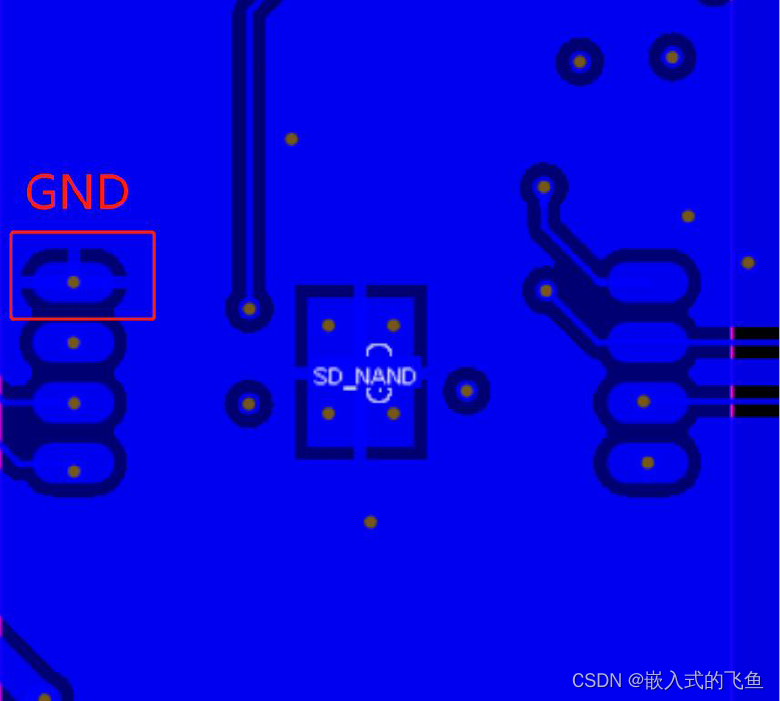

② layout 时 GND 脚 建议采用类似的“十字”或“梅花”型的连接 有利于过炉焊接。防止GND 脚整体铺铜散热很快导致虚焊假焊现象存在 (如下图)

1795

1795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?