数字系统的设计流程

1、数字系统的需求分析

2、功能部件设计(分模块设计)

3、构建数据通路

4、构建控制单元

5、系统集成联调

实验终极目标

实验任务分解

组合逻辑

一、组合逻辑部件设计

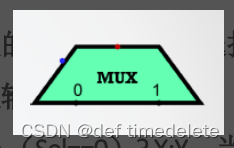

(一):2路选择器(16位)设计*

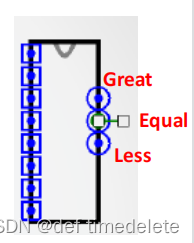

外观

1. 构建2路选择器(1位)

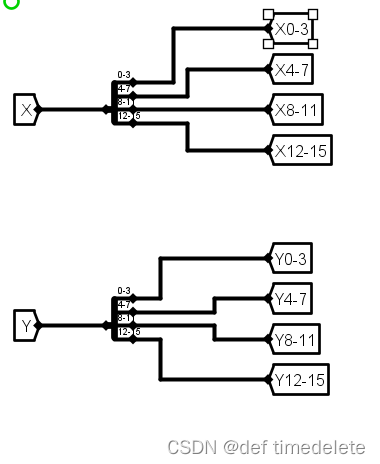

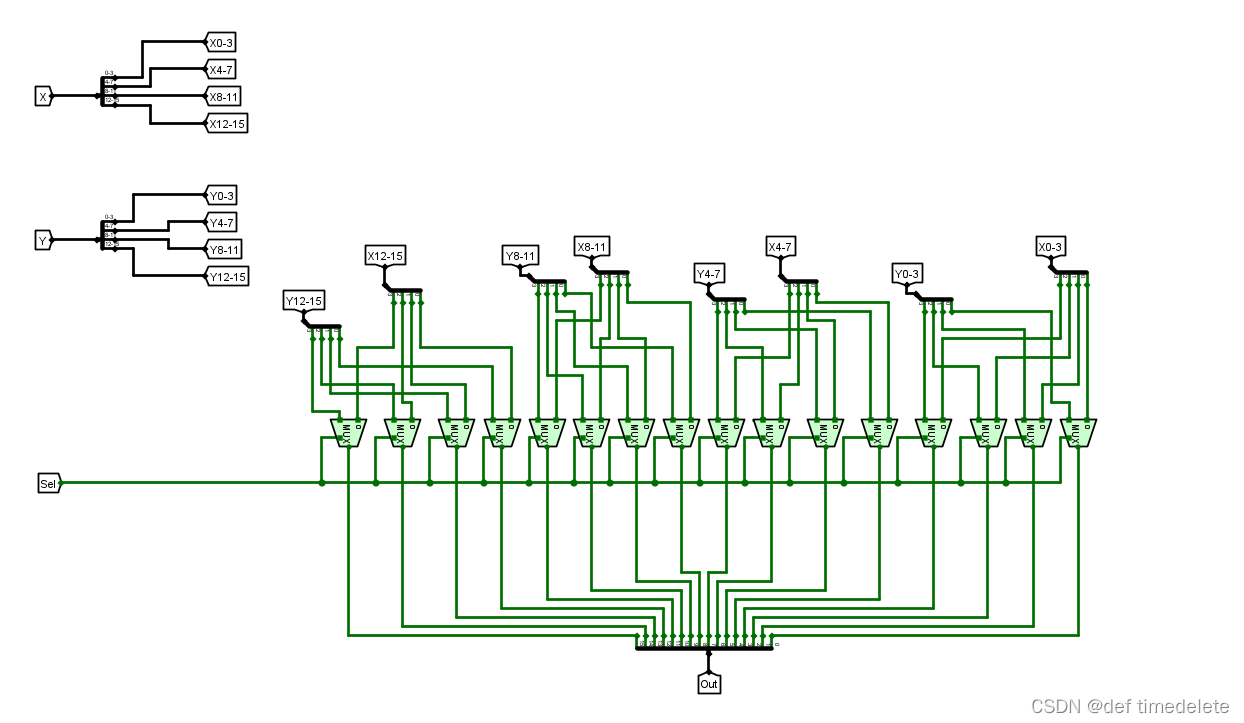

2、复制产生16个2路选择器(1位),连接形成1个2路选择器(16位)*

电路连接(只能手动连接)

要先用分线器将X和Y分成四位

测试结果(PASS)

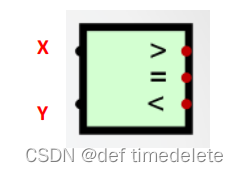

(二):16位无符号比较器

1. 构造4位无符号比较器

外观

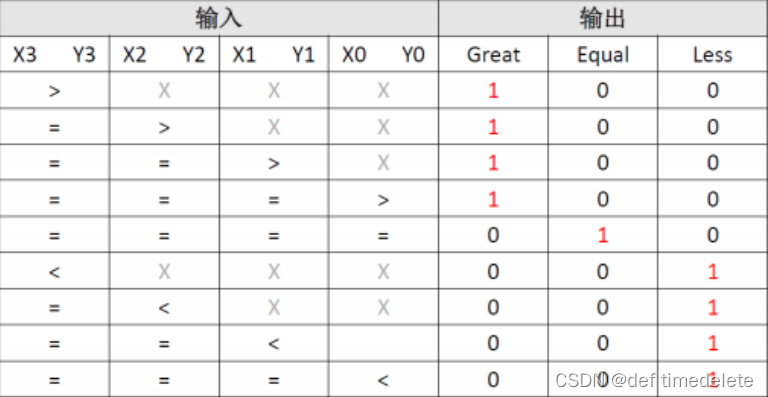

简易真值表

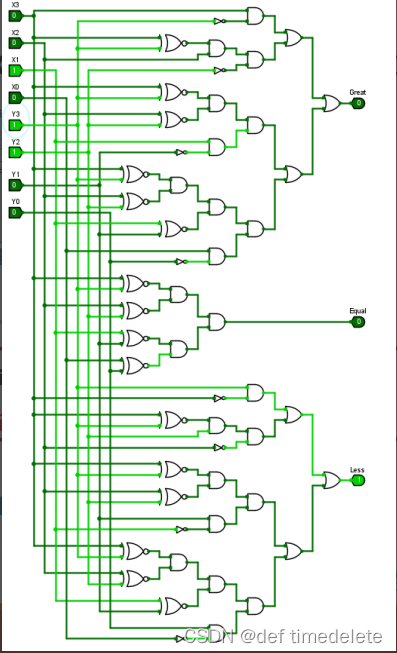

连接电路

手动绘制

利用真值表或逻辑表达 式自动生成电路

Great=X0 ~Y3 ~Y2 ~Y1 ~Y0 + X1 ~Y3 ~Y2 ~Y1 + X1 X0 ~Y3 ~Y2 ~Y0 + X2 ~Y3 ~Y2 + X2 X0 ~Y3 ~Y1 ~Y0 + X2 X1 ~Y3 ~Y1 + X2 X1 X0 ~Y3 ~Y0 + X3 ~Y3 + X3 X0 ~Y2 ~Y1 ~Y0 + X3 X1 ~Y2 ~Y1 + X3 X1 X0 ~Y2 ~Y0 + X3 X2 ~Y2 + X3 X2 X0 ~Y1 ~Y0 + X3 X2 X1 ~Y1 + X3 X2 X1 X0 ~Y0

Equal=~X3 ~X2 ~X1 ~X0 ~Y3 ~Y2 ~Y1 ~Y0 + ~X3 ~X2 ~X1 X0 ~Y3 ~Y2 ~Y1 Y0 + ~X3 ~X2 X1 ~X0 ~Y3 ~Y2 Y1 ~Y0 + ~X3 ~X2 X1 X0 ~Y3 ~Y2 Y1 Y0 + ~X3 X2 ~X1 ~X0 ~Y3 Y2 ~Y1 ~Y0 + ~X3 X2 ~X1 X0 ~Y3 Y2 ~Y1 Y0 + ~X3 X2 X1 ~X0 ~Y3 Y2 Y1 ~Y0 + ~X3 X2 X1 X0 ~Y3 Y2 Y1 Y0 + X3 ~X2 ~X1 ~X0 Y3 ~Y2 ~Y1 ~Y0 + X3 ~X2 ~X1 X0 Y3 ~Y2 ~Y1 Y0 + X3 ~X2 X1 ~X0 Y3 ~Y2 Y1 ~Y0 + X3 ~X2 X1 X0 Y3 ~Y2 Y1 Y0 + X3 X2 ~X1 ~X0 Y3 Y2 ~Y1 ~Y0 + X3 X2 ~X1 X0 Y3 Y2 ~Y1 Y0 + X3 X2 X1 ~X0 Y3 Y2 Y1 ~Y0 + X3 X2 X1 X0 Y3 Y2 Y1 Y0

Less=~X3 ~X2 ~X1 ~X0 Y0 + ~X3 ~X2 ~X1 Y1 + ~X3 ~X2 ~X0 Y1 Y0 + ~X3 ~X2 Y2 + ~X3 ~X1 ~X0 Y2 Y0 + ~X3 ~X1 Y2 Y1 + ~X3 ~X0 Y2 Y1 Y0 + ~X3 Y3 + ~X2 ~X1 ~X0 Y3 Y0 + ~X2 ~X1 Y3 Y1 + ~X2 ~X0 Y3 Y1 Y0 + ~X2 Y3 Y2 + ~X1 ~X0 Y3 Y2 Y0 + ~X1 Y3 Y2 Y1 + ~X0 Y3 Y2 Y1 Y0

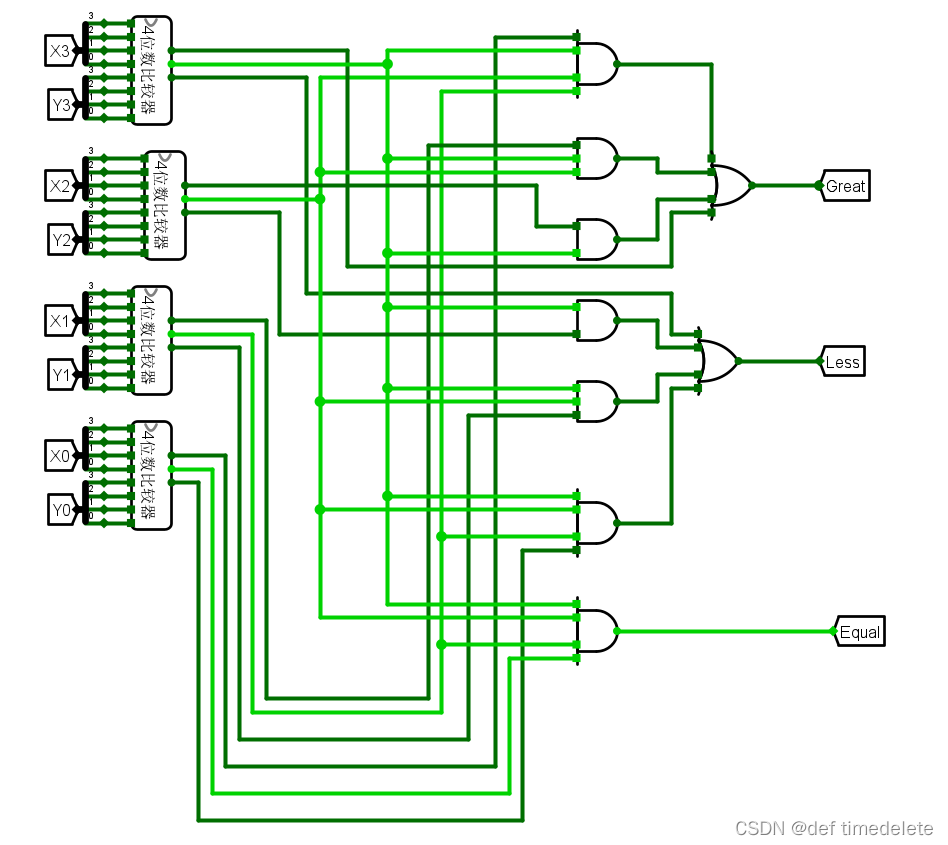

2、复制产生4个4位的比较器,再级连接形成1个16位的比较器

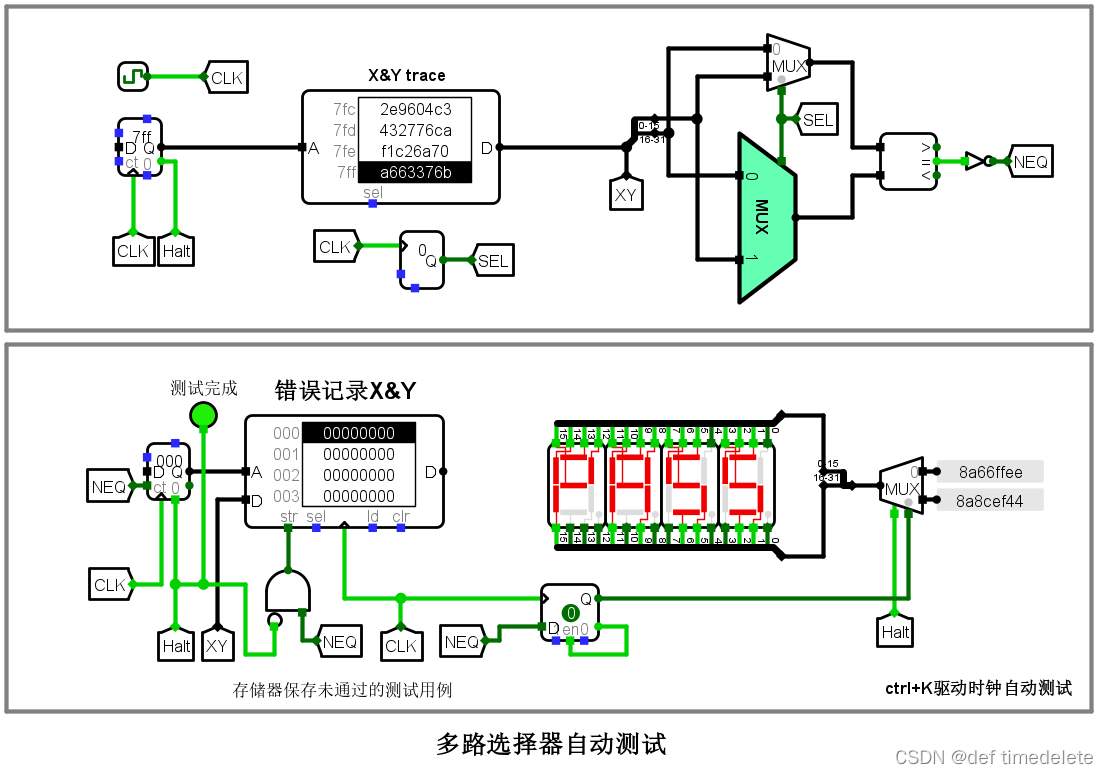

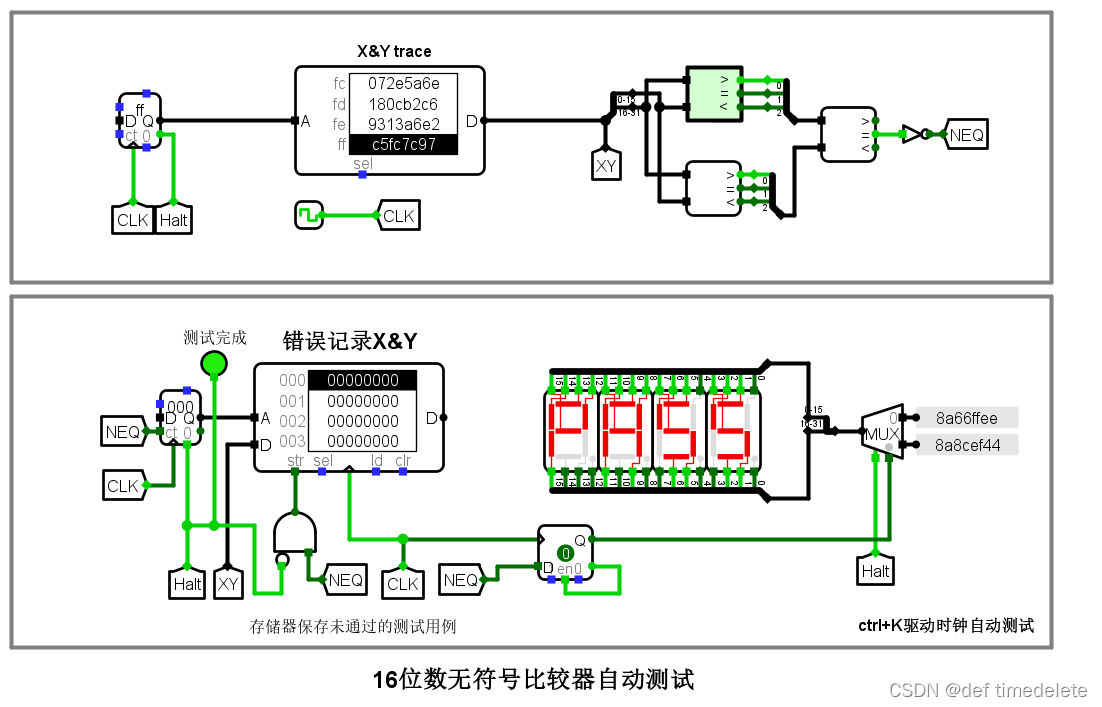

自动测试结果

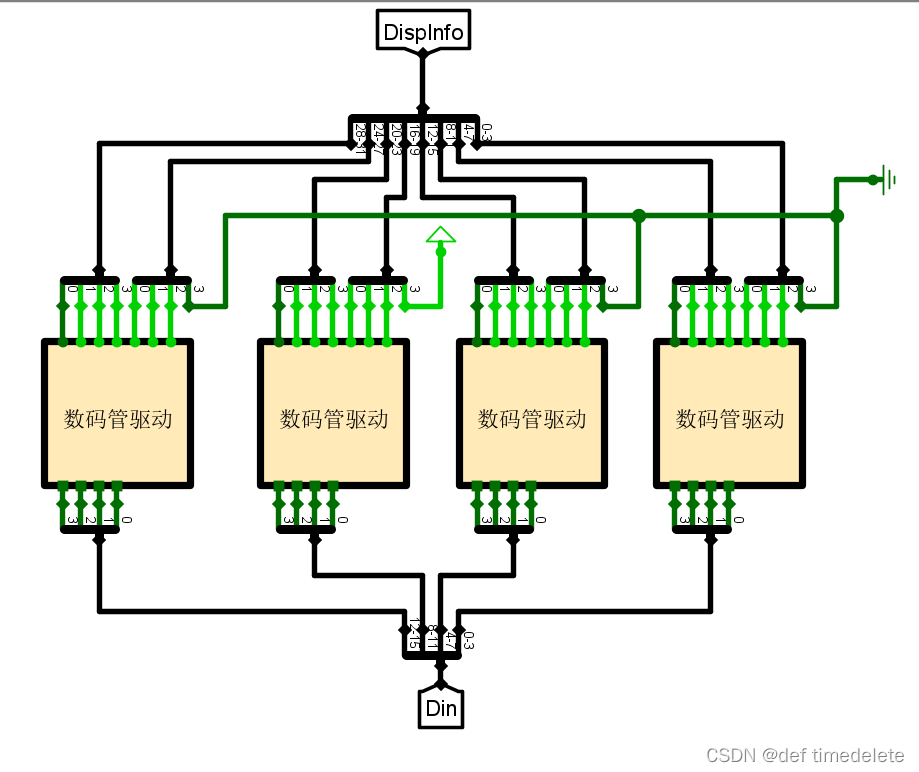

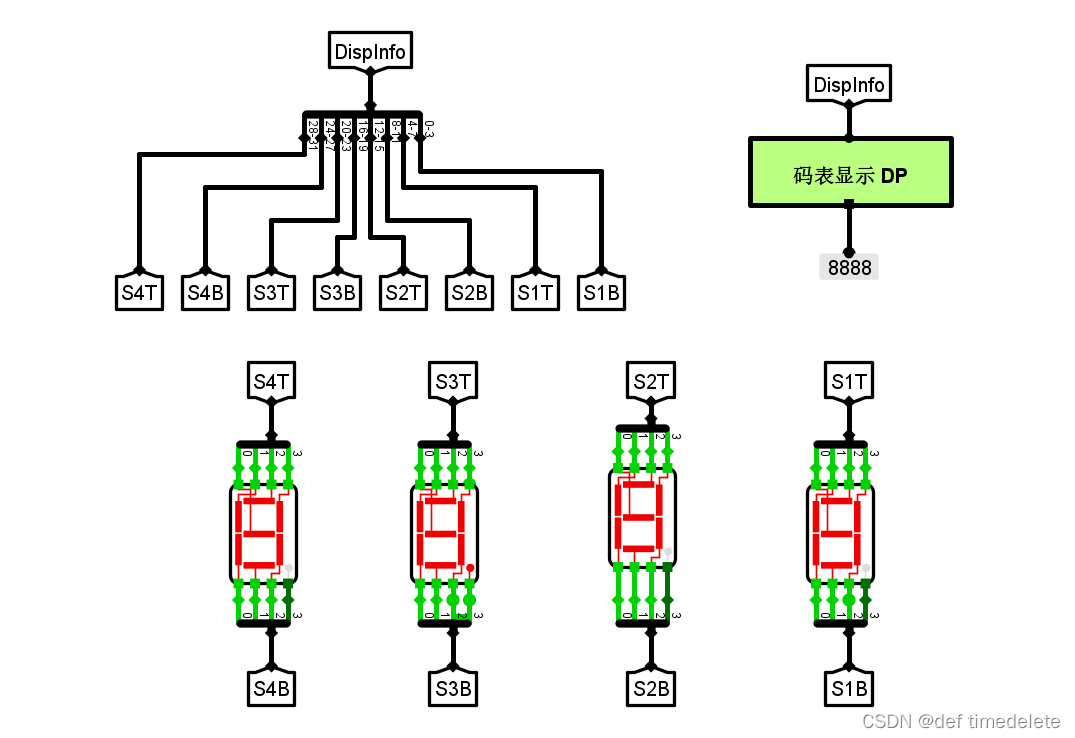

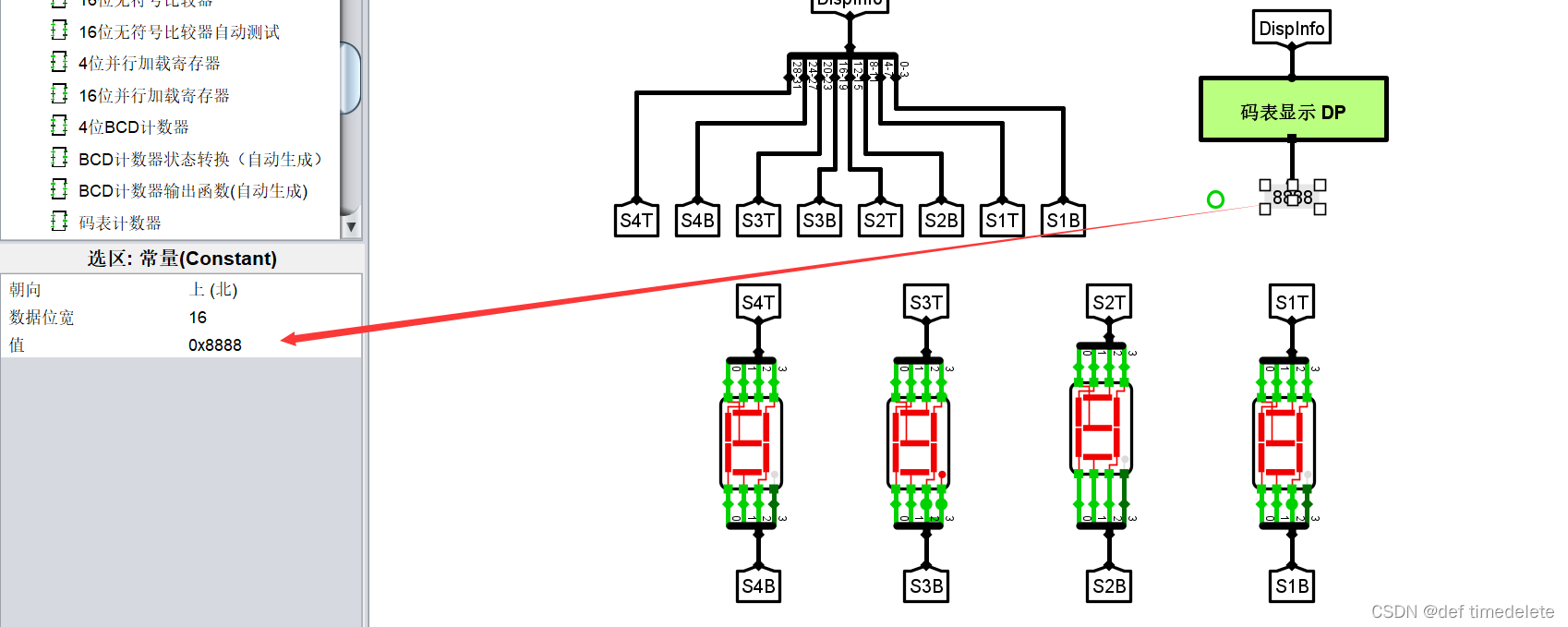

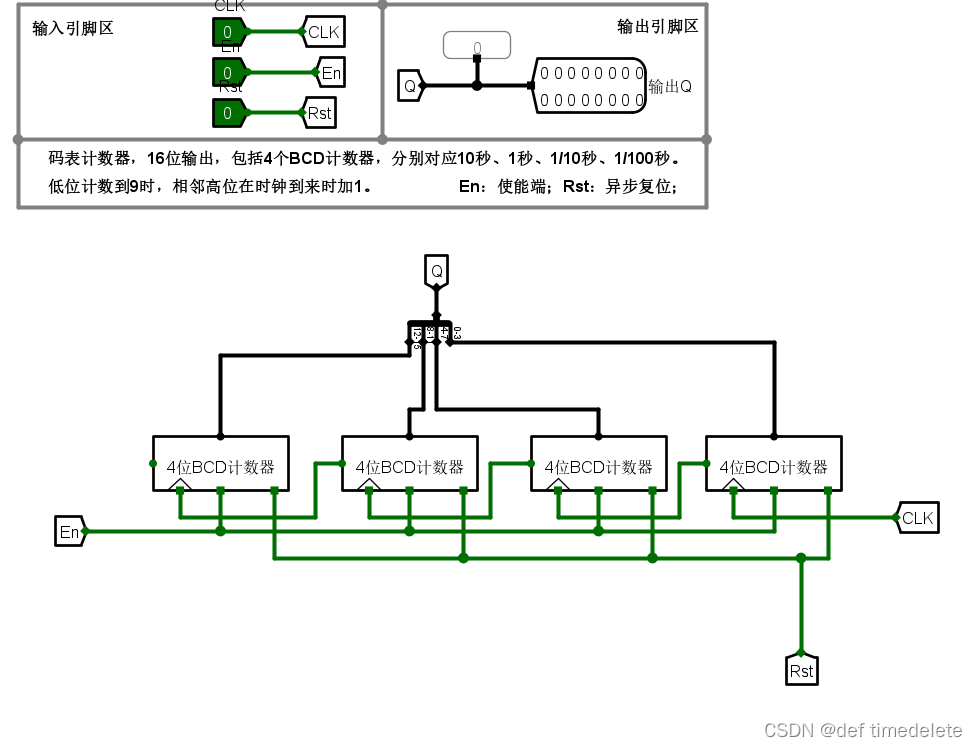

(三):码表数码管的驱动

![]()

要调节显示的数字时,如下图所示点击常量符号,在左下角对常量的属性进行修改

二、同步时序逻辑电路概述

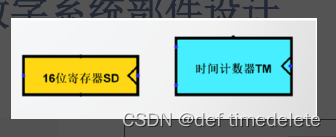

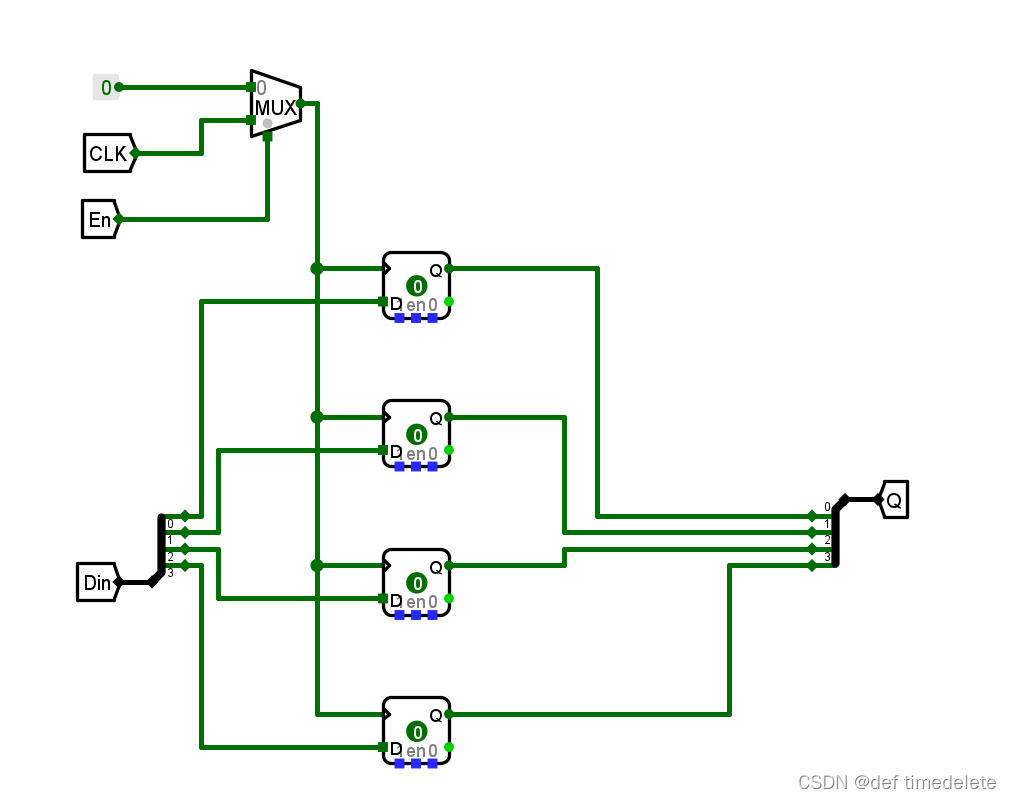

(一):16位并行加载寄存器

1. 构建 4位并行加载寄存器*

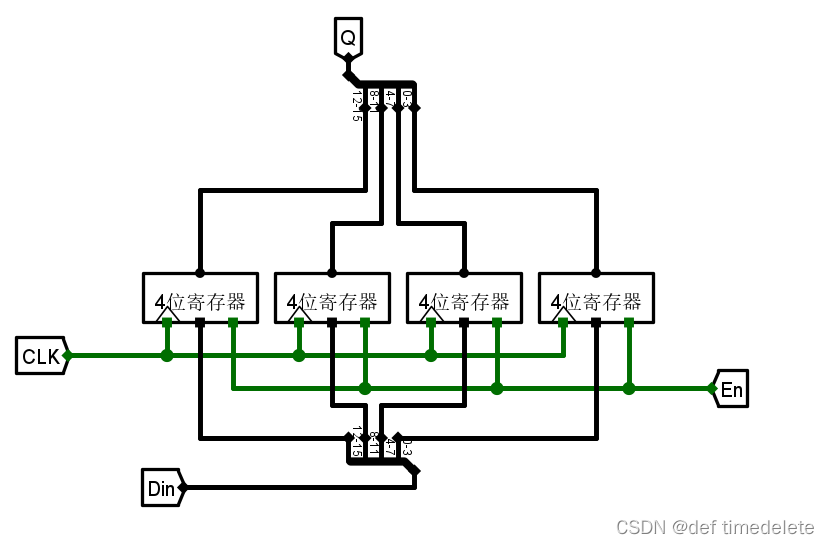

2、复制产生4个4位寄存器,再并联接形成1个16位并行加载寄存器

电路连接

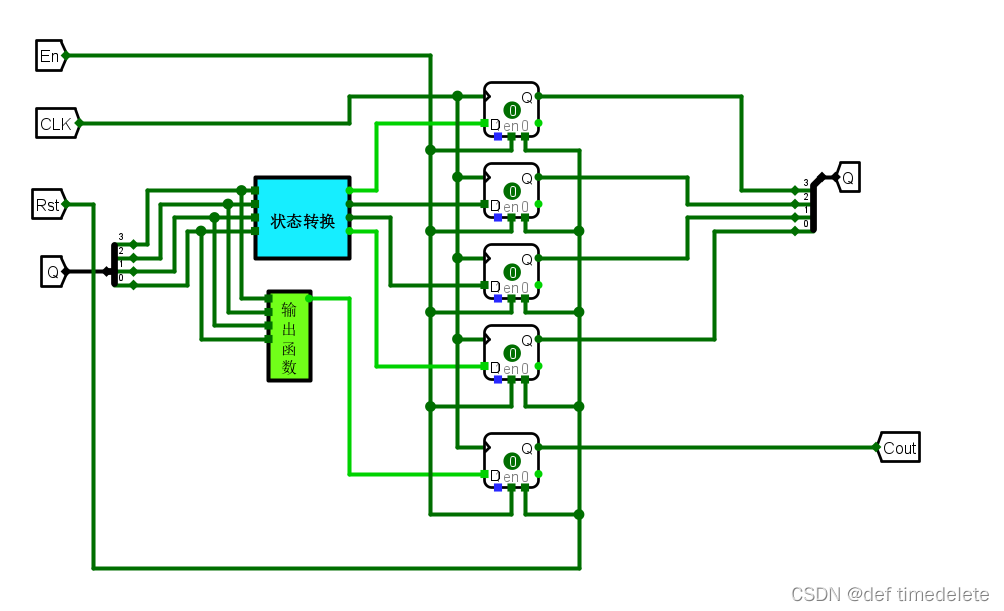

(二):4位BCD反向计数器

4位BCD反向计数器的外部特性

利用真值表或逻辑表达 式自动生成电路

BCD计数器状态转换

N3=~S3 ~S2 ~S1 ~S0 + S3 S0 + S3 S1 + S3 S2

N2=S2 S0 + S2 S1 + S3 ~S2 ~S1 ~S0

N1=S1 S0 + S2 ~S1 ~S0 + S3 ~S1 ~S0

N0=~S0

BCD计数器输出函数

Cout=~S3 ~S2 ~S1 ~S0

4位BCD计数器(手动绘制)

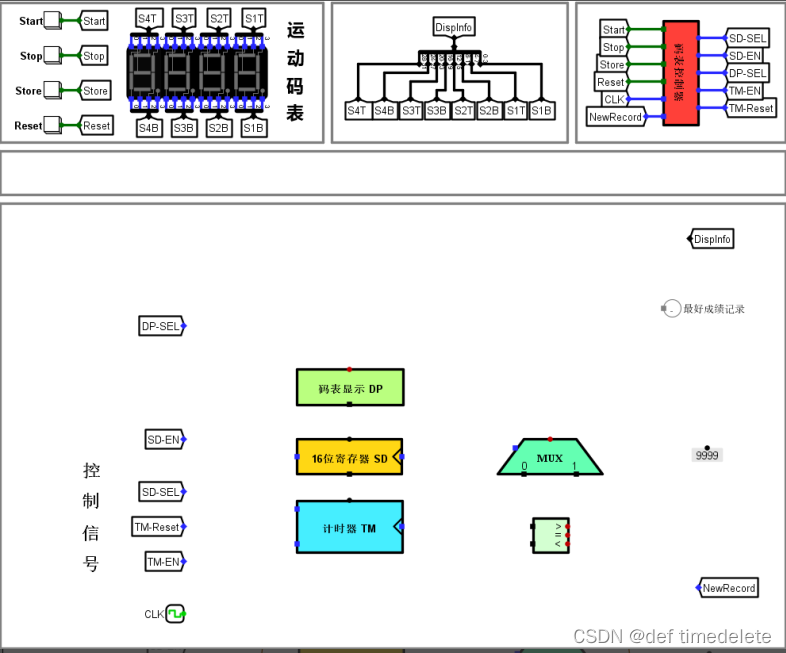

三、运动码表控制单元构建(重点!!)

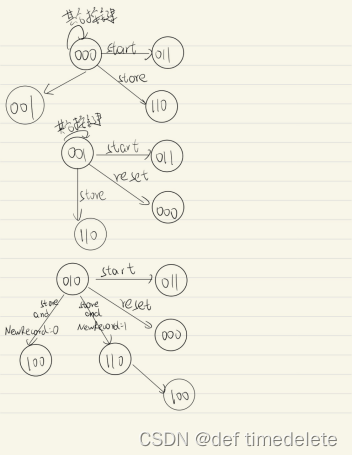

“码表控制状态转换”的设计

运动码表状态定义

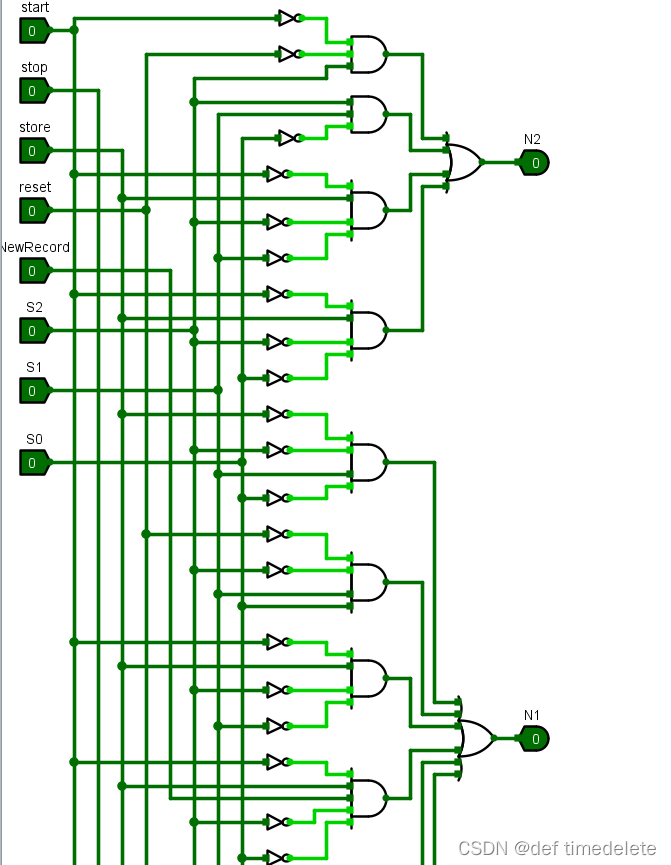

电路连接

表达式

N2=~start ~reset S2 + S2 S1 ~S0 + ~start store ~S2 ~S1 + ~start store ~S2 ~S0

N1=~store ~S2 S1 ~S0 + ~reset ~S2 S1 S0 + ~start store ~S2 ~S1 + ~start store NewRecord ~S2 ~S0 + start ~store ~S2 ~S1 + start ~reset S2

N0= ~store ~reset ~S2 ~S1 + ~store ~S2 ~S1 ~S0 + ~stop ~reset ~S2 S1 S0 + start ~store ~S2 ~S1 + start ~store ~S2 ~S0 + start ~reset S2

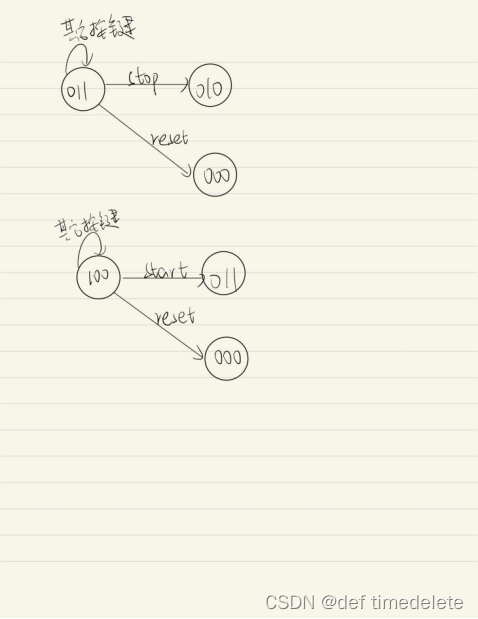

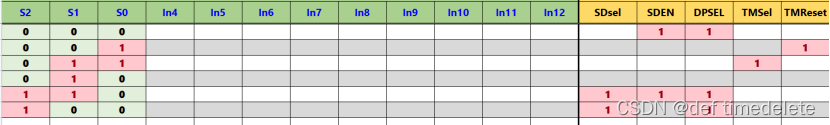

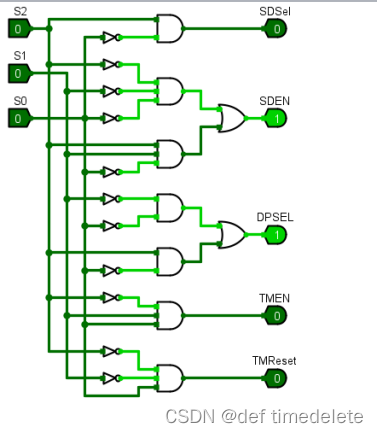

“码表控制输出函数”的设计

SDSel为0时,选择的是常量9999,为1时,选择的是当前计时器的值

DPSel为0时,选择的是当前计时器的值,为1时,选择的是16位寄存器里存的值

SDEN为1时,更新寄存器的值

TMSel(TMED)为1时,打开计时器开始倒计时

TMReset为1时,清空计时器的值

真值表

电路连接

表达式

SDSel=S2 ~S0

SDEN=~S2 ~S1 ~S0 + S2 S1 ~S0

DPSEL=~S1 ~S0 + S2 ~S0

TMEN=~S2 S1 S0

TMReset=~S2 ~S1 S0

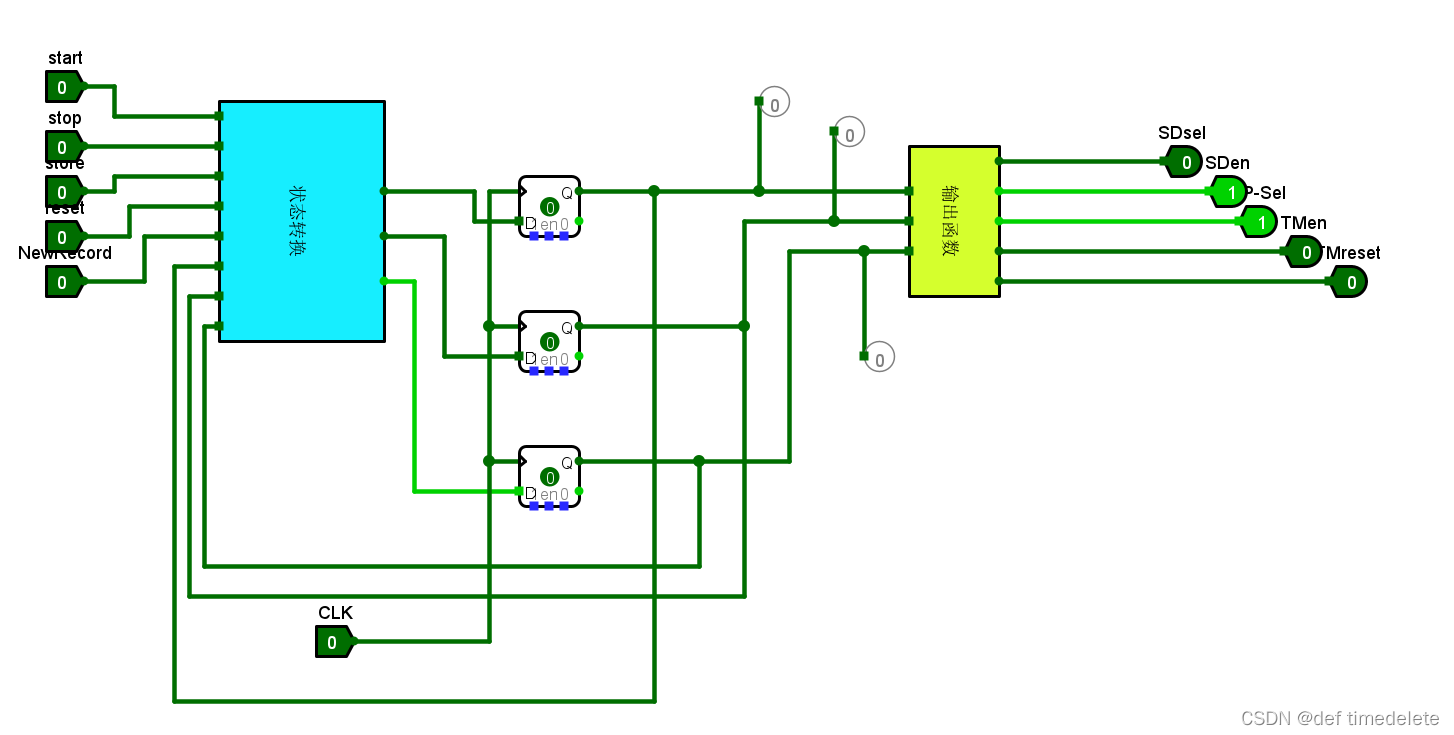

码表控制器

电路连接

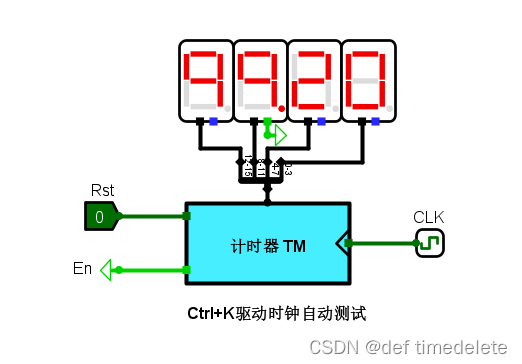

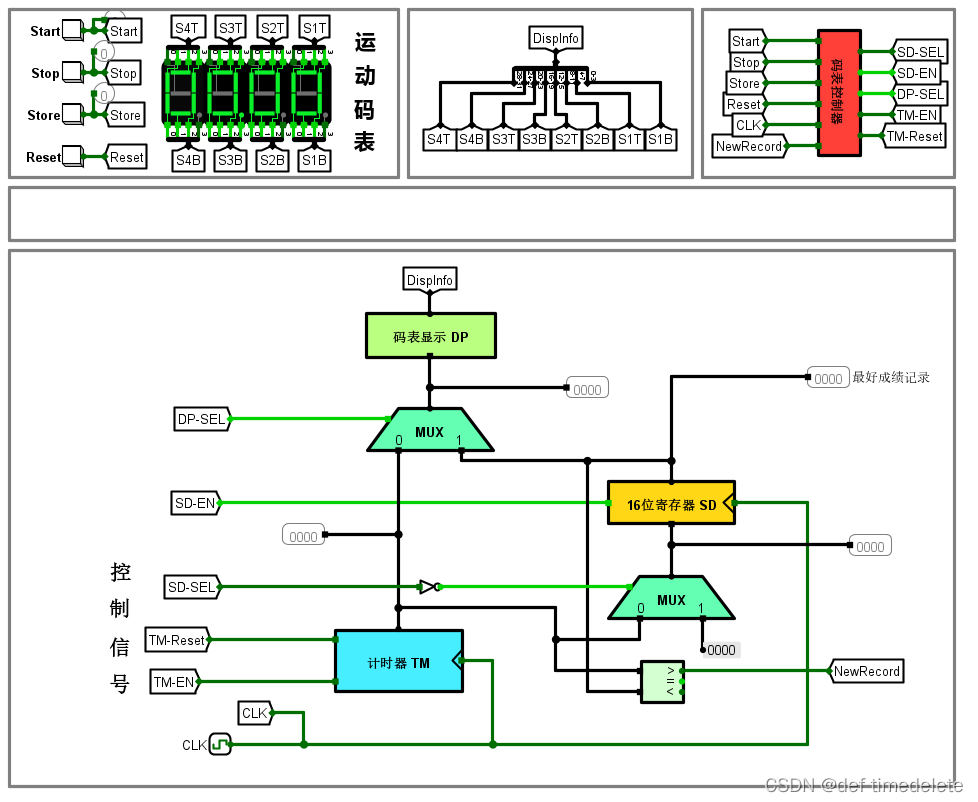

运动码表系统集成与联调

测试结果

Logisim 反向运动码表测试视频

3230

3230

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?