超低温漂,带隙基准,高电源抑制比,低功耗,高阶温度补偿带隙基准,cadence

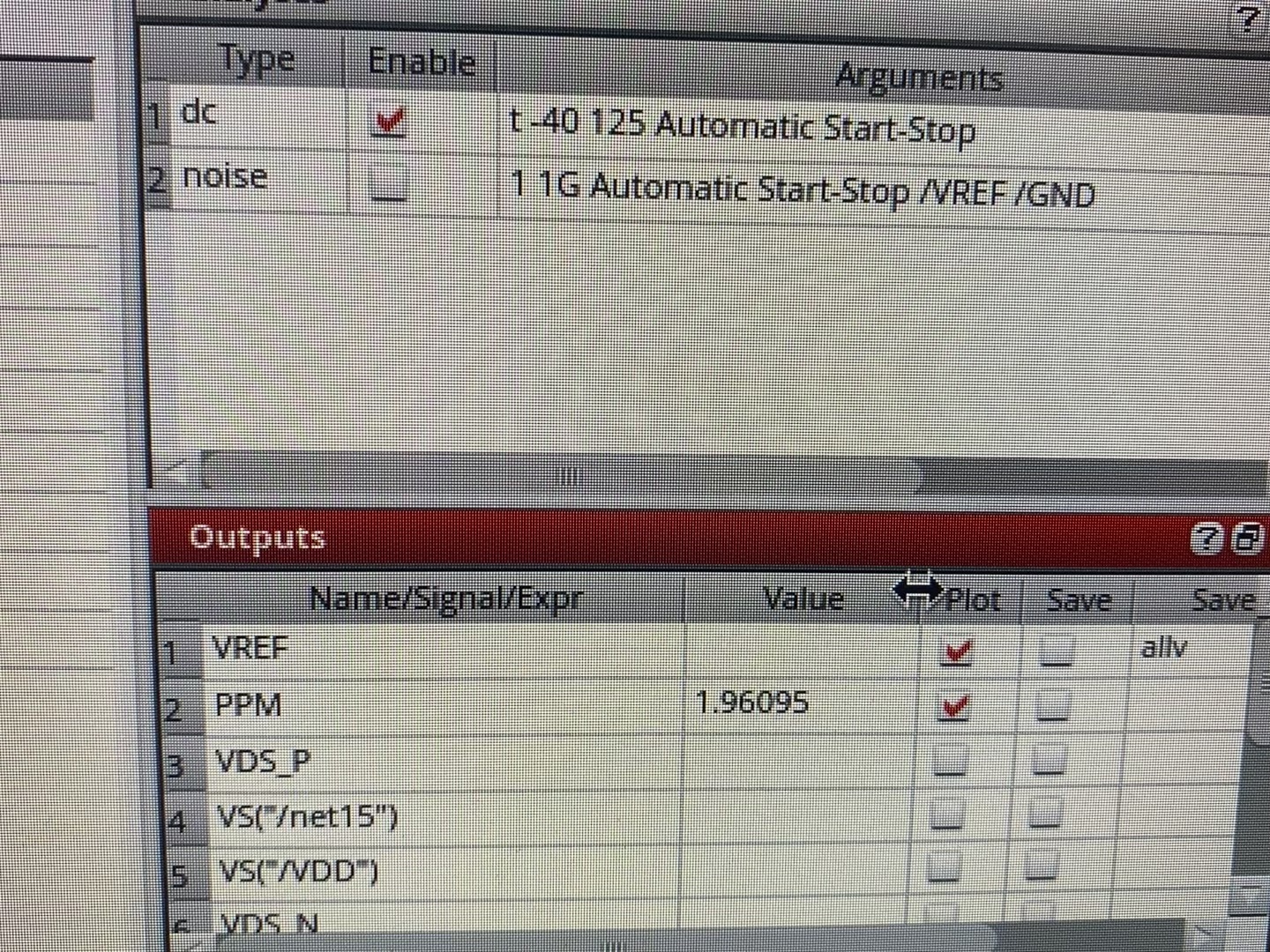

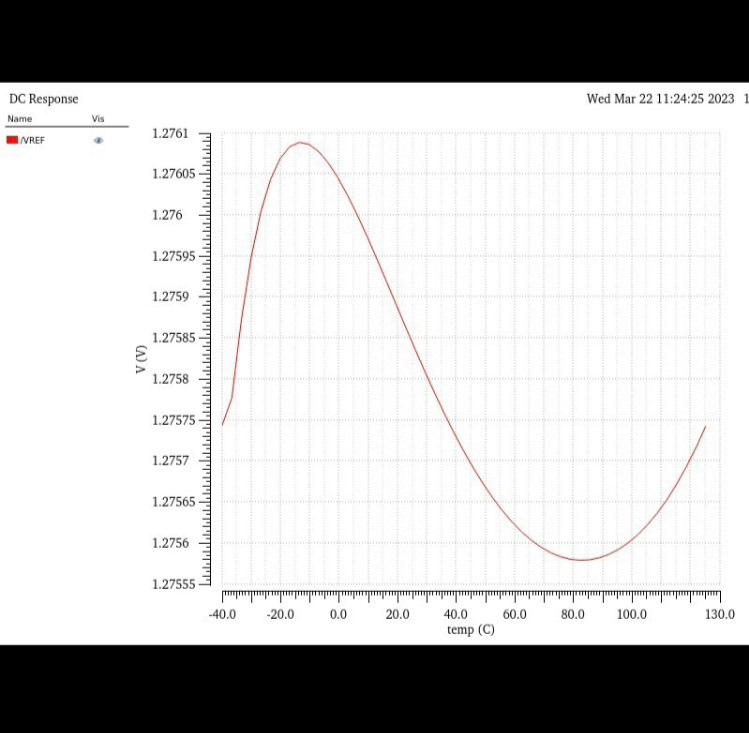

ppm:1.9

psrr:-90dB

电流:14.47uA

1.带37页设计文档PDF,有推导过程和调试过程,以及仿真设置

2.带工艺库打包,都是61OA格式,可以提供虚拟机和cadence618,包安装调试

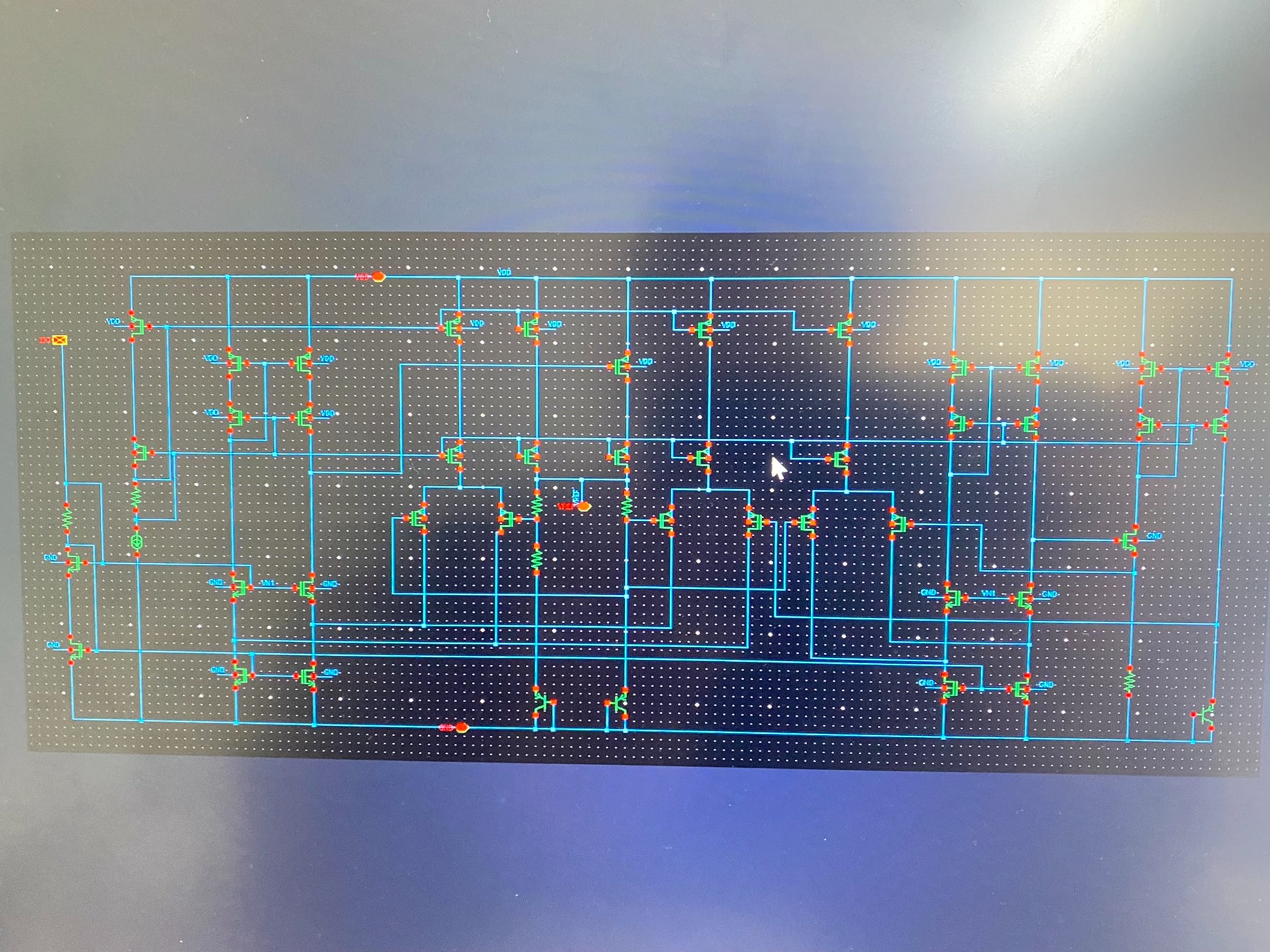

3.过程截图和电路截图

关联词:cadence电路设计,带隙基准,bandgap,低温漂,高阶温度补偿

ID:75199711391537726

老王模拟IC

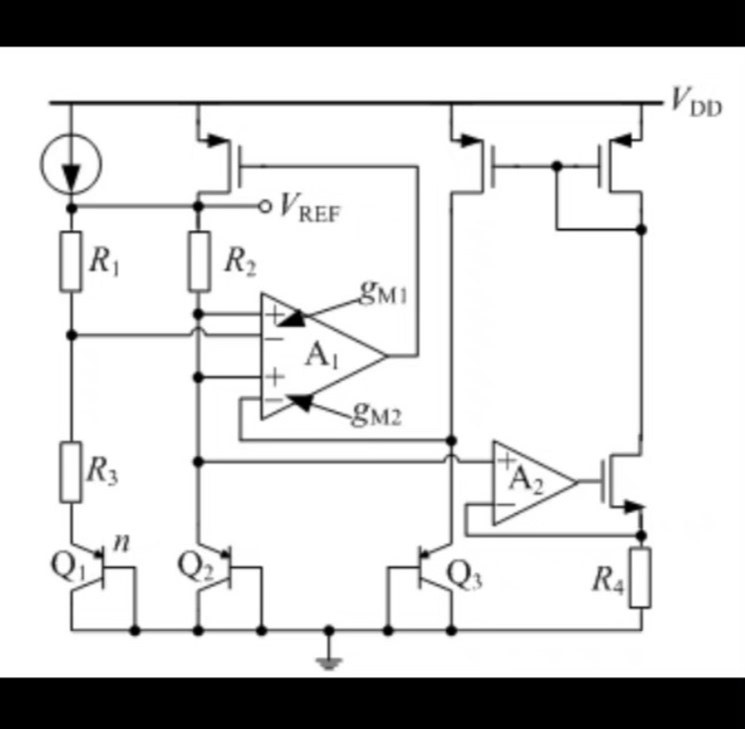

超低温漂,带隙基准,高电源抑制比,低功耗,高阶温度补偿带隙基准是现代芯片设计中非常重要的技术指标。在当今的电路设计中,cadence电路设计工具已经成为了首选的设计平台。本文将围绕着cadence电路设计工具展开讨论,探讨如何实现带隙基准,并解决低温漂和温度补偿的问题。

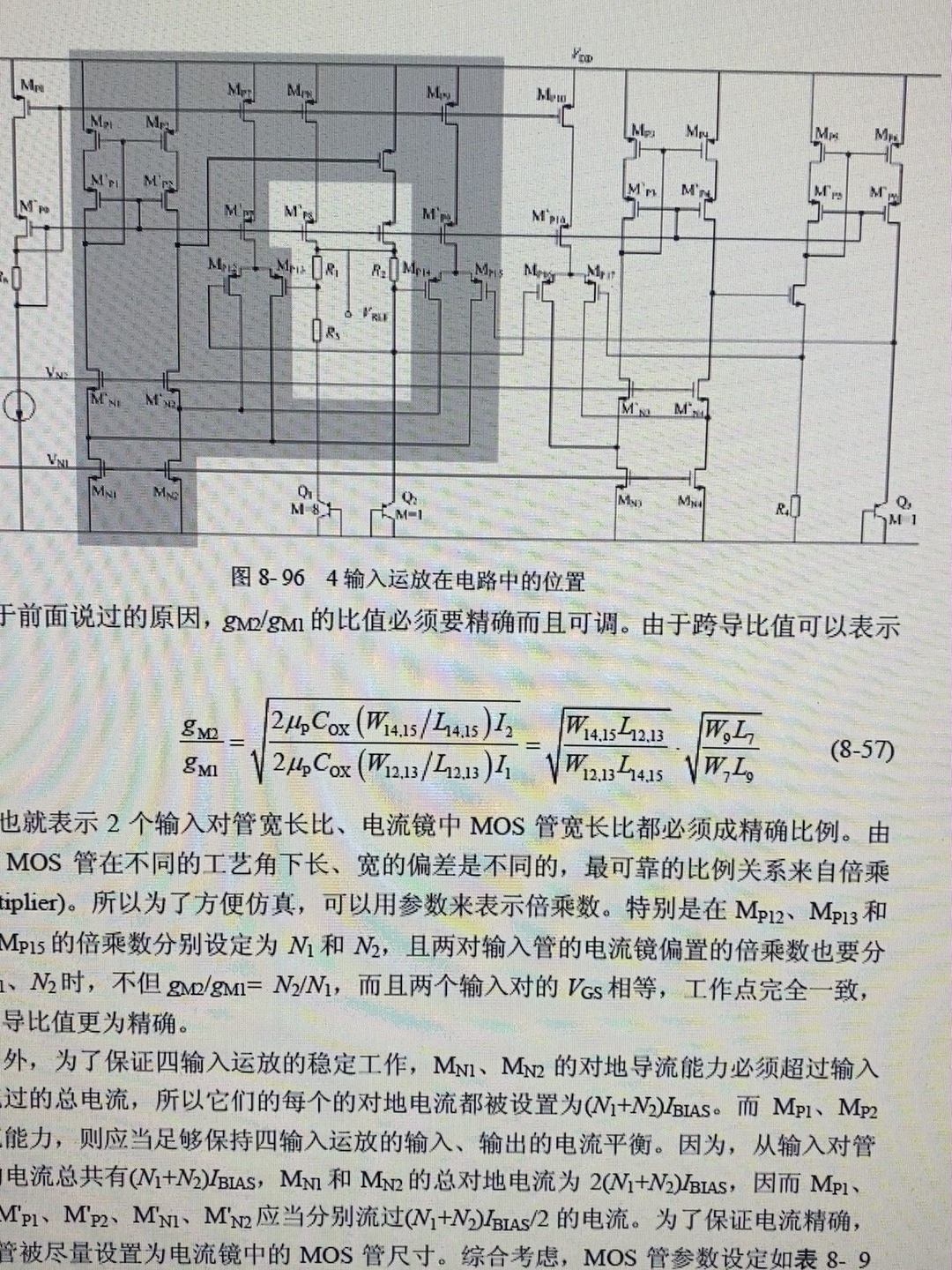

带隙基准是现代电路设计中一项重要的技术,它能够提供稳定的参考电压。带隙基准电路的设计需要考虑多个因素,包括电源抑制比、功耗等。在cadence电路设计中,可以通过使用合适的工艺库来实现带隙基准电路的设计。工艺库的选择对于电路设计的性能有着重要影响,因此在选择工艺库时需要考虑电流、温度等参数。

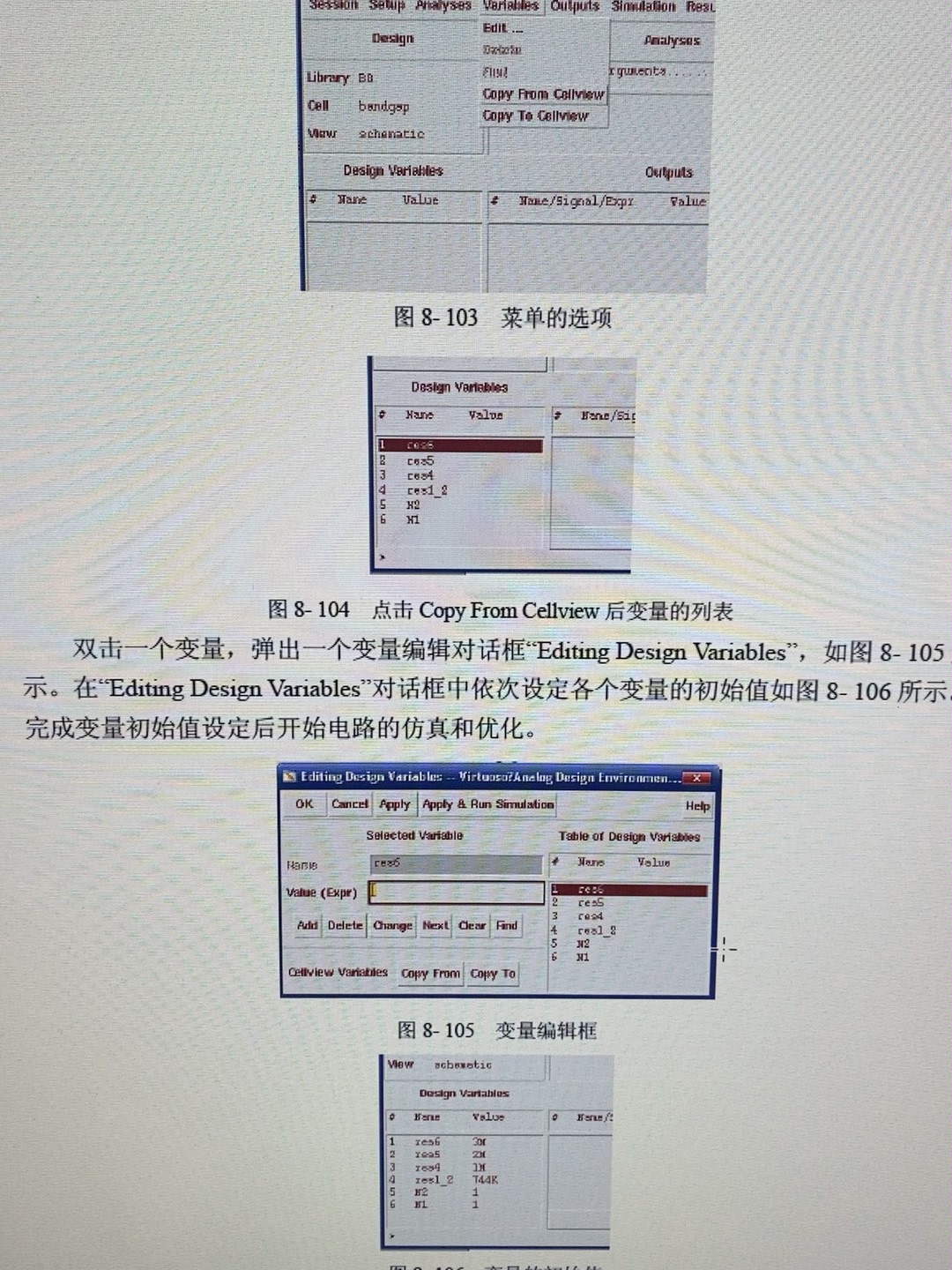

为了实现超低温漂和高阶温度补偿,我们可以借助cadence电路设计工具提供的强大仿真功能。使用cadence提供的仿真工具,我们可以对电路进行详细的仿真和分析,从而优化电路设计。在仿真过程中,可以使用cadence提供的虚拟机和cadence618来进行模拟和调试。

本文还提供了设计文档的PDF版本,该文档详细记录了设计过程和调试过程。设计文档中包含了推导过程和仿真设置,这有助于读者了解设计的思路和方法。此外,本文还提供了过程截图和电路截图,用于展示设计过程中的关键步骤和实验结果。

综上所述,本文围绕cadence电路设计工具展开讨论,介绍了如何实现带隙基准电路,并解决低温漂和高阶温度补偿的问题。通过合理选择工艺库、使用cadence提供的仿真工具以及详细的设计文档和截图,可以帮助读者更好地理解和应用该技术。希望本文能为读者在cadence电路设计领域提供一些有价值的参考。

关键词:cadence电路设计,带隙基准,bandgap,低温漂,高阶温度补偿

【相关代码,程序地址】:http://fansik.cn/711391537726.html

1689

1689

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?