一、phase机制

1、简述

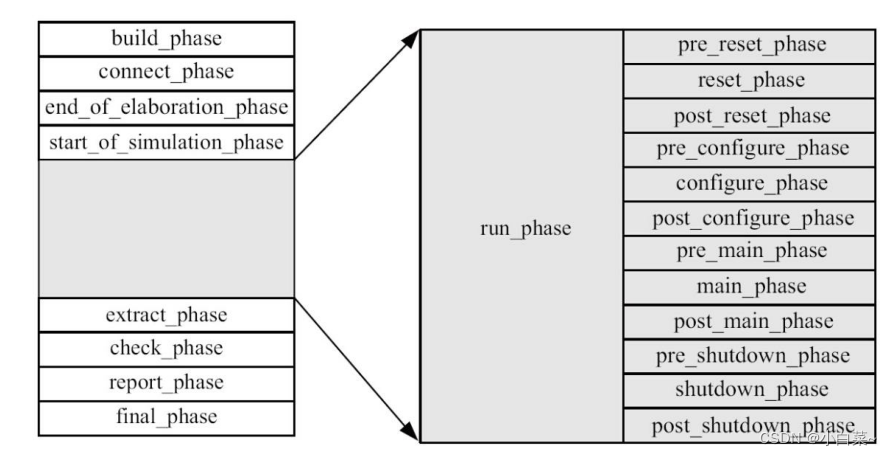

UVM中phase分两类,一类是function phase,不耗费仿真时间;另一类是task phase,消耗仿真时间。见下图,灰色是task phase,其他为function phase。

说明:

- run-time phase指run_phase包含的12个小的phase,称动态运行(run-time)的phase。

- run_phase和pre_reset_phase等12个小的phase并行运行。上图中的不同的phase之间在时间上是自上而下执行。

- reset_phase对DUT进行复位、初始化等操作

- 在configure_phase进行DUT的配置

- DUT的运行主要在main_phase完成

- shutdown_phase则是做一些与DUT断电相关的操作

- 常用的phase主要是build_phase,connect_phase,main_phase。

- build_phase作用主要是例化子组件、例化寄存器模型,get_config_db为组件设置一些值。

- connect_phase作用主要是建立连接,比如寄存器模型和组件,TLM通信中的port、export,和组件之间的连接等。

2、phase的执行顺序

- 从UVM树结构来看,除了build_phase、final_phase之外,所有不耗费仿真时间的phase(即function phase)都是自下而上执行的。对于uvm树中同一层次的组件(兄弟关系),是按例化时的那个名字字典顺序执行的。

- 对于task phase,所有组件的run_phase时自上而下顺序启动,但它们是同时运行的,并不要等待上个组件的run_phase执行完成才执行下一个组件的run_phase。

- 对于12个小phase,run-time phase,对不同组件的同一phase,是同时启动执行的,但不一定同时结束,但必须等所有组件的上一个phase执行结束后,才能同时执行下一个小phase。同一个component的run_phase与其post_shutdown_phase全部完成才会进入下一个phase(extract_phase)。

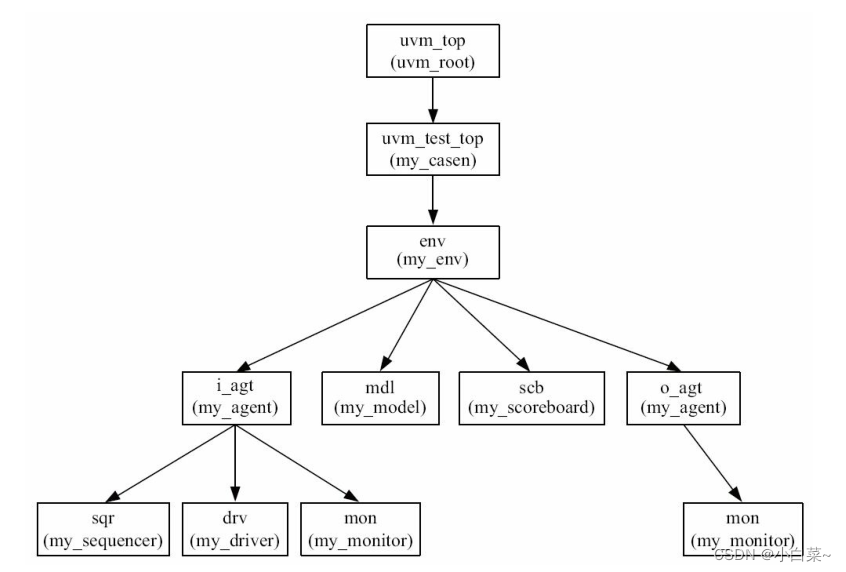

- UVM采用深度优先的原则,比如scordboard和driver的build_phase,先吧driver支路执行完再执行,再执行scordboard的build_phase,如图所示,常用UVM树结构图

- 对于build_phase来说,uvm_component自动获取通过config_db::set设置的参数,如果要关掉这个功能,可以在自己的build_phase中不调用super.build_phase,除build_phase外,在写其他phase时,完全可以不必加上super.xxxx_phase语句,这个结论只适用于直接扩展自uvm_component的类。

3、objection机制

1、用raise_objection和drop_objection来提起、撤销,控制验证平台各个phase的运行,解决何时结束仿真的问题,主要控制task phase,消耗时间的phase。

- 如果phase没有提起任何objection,那么将会直接跳转到下一个phase中,里面消耗时间的语句也不会运行。

- 如果想执行一些耗费时间的代码,那么要在此phase下任意一个component中至少提起一次objection

- 在任意一个A组件中的phase中提起objection,其他组件中的相同phase也会被相应的提起,但其他组件的执行时间受到提起phase的A组件控制,即A撤销phase,其他组件也会强制结束该phase。

- 对于run_phase,第一是其他动态运行的phase中有objection被提起,run_phase也会被相应提起,反之不成立。在这种情况下,运行时间受其他动态运行phase中objection控制,run_phase只能被动地接受。第二是在run_phase中raise_objection,这种情况下运行时间完全受run_phase控制。

- 为什么要在类似task main_phase(uvm_phase phase)任务中加入phase?

- 在UVM中,测试的不同阶段被表示为不同的

uvm_phase对象,这些阶段被组织成一个阶段(phase)序列,并通过UVM中的uvm_phase类来管理,每个测试都需要通过不同的阶段。在测试执行期间,系统会定期将当前阶段传递给每个组件,以便组件可以针对不同的阶段执行特定的行为,便于控制所有组件相同的phase的raise_objection和drop_objection,即参数phase就表示当前运行阶段的phase。

说明:

- 在命令行可以使用+UVM_PHASE_TRACE来调试phase

- 可以在命令行使用+UVM_OBJECTION_TRACE来调试objection

2、在sequence中,通过starting_phase来raise_objection和drop_objection,用于控制仿真平台的运行,主要可以控制sequence中激励的产生与发送,这些要消耗仿真时间。starting_phase的值可以通过set default_sequence(uvm1.1允许)来自动设置或者手动设置;还可以在base_test及其继承类里raise_objection和drop_objection,以便控制多个sequence的运行。

935

935

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?