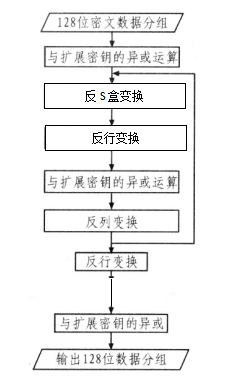

解密部分结构设计

加密部分总体概述

加密部分算法如下:

解密部分与加密部分大体一致,故而Xorkey、key8bit、用于行变换的dpram,用于key8bit的sbox是通用的,row_trans和col_trans进行了部分改变。同时,考虑到解密部分的密钥异或模块使用的密钥与密钥扩展运算顺序相反,即第一次密钥异或模块使用的密钥是密钥扩展第十轮的结果,第二次则为第九轮结果……故采取先算出十轮密钥扩展结果并进行存储,轮变换时再进行读取并运算的方法。

解密部分用于密钥扩展有Simreq, Time_adjust与Keysave模块,存储输入数据使用了一片FIFO,逆Sbox运算使用Inv_sbox模块,同时增加了用于调整运算顺序的Inv_comb模块。

解密部分的所有模块如下:

Inv_storekey:用于存输入数据的FIFO

Simkeyreq:模拟keyreq变化

Key8bit:密钥扩展模块(与加密共用)

Sbox用于密钥扩展部分(共用)

Time_adjust:密钥读写地址控制

Keysave:用于存扩展秘钥的ram

Xorkey:密钥异或模块(共用)

Inv_sbox:逆S盒变换

Row_trans:行变换(部分共用)

Dpram:用于行变换的ram(共用)

Col_tran:列变换(部分共

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?