西南交大数电实验

实验要求

一、 实验目的

1、巩固组合逻辑电路设计、仿真方法。

2、学习Verilog HDL层次化文件设计。

二、实验内容

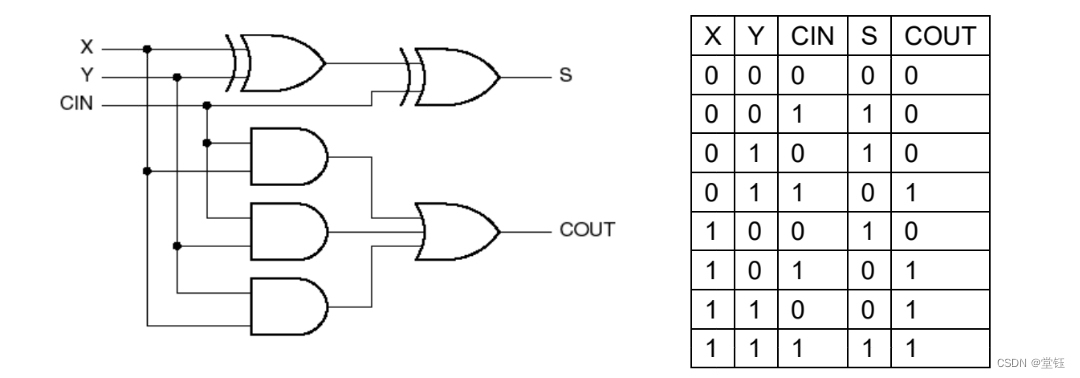

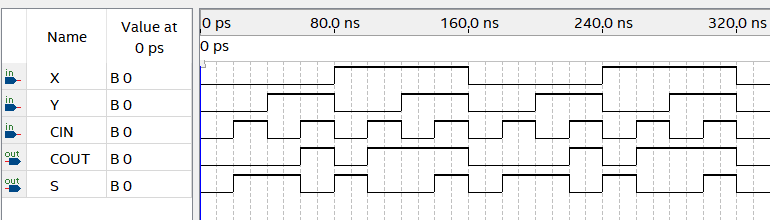

实验内容按以下步骤,用Verilog HDL描述和仿真图示电路。该电路实现1位二进制加法,X、Y分别是加数、被加数,CIN是低位来的进位,COUT是向高位的进位,S是相加的和。真值表如下:

编辑

1、门级描述与仿真

(1)新建工程文件,工程名是:_学号_V1_1bit_adder_ga(1位加法器门级描述);

(2)新建Verilog HDL文件,将代码输入。注意:输入输出端口名必须与图上的名字完全一致,否则无法仿真!【5分】

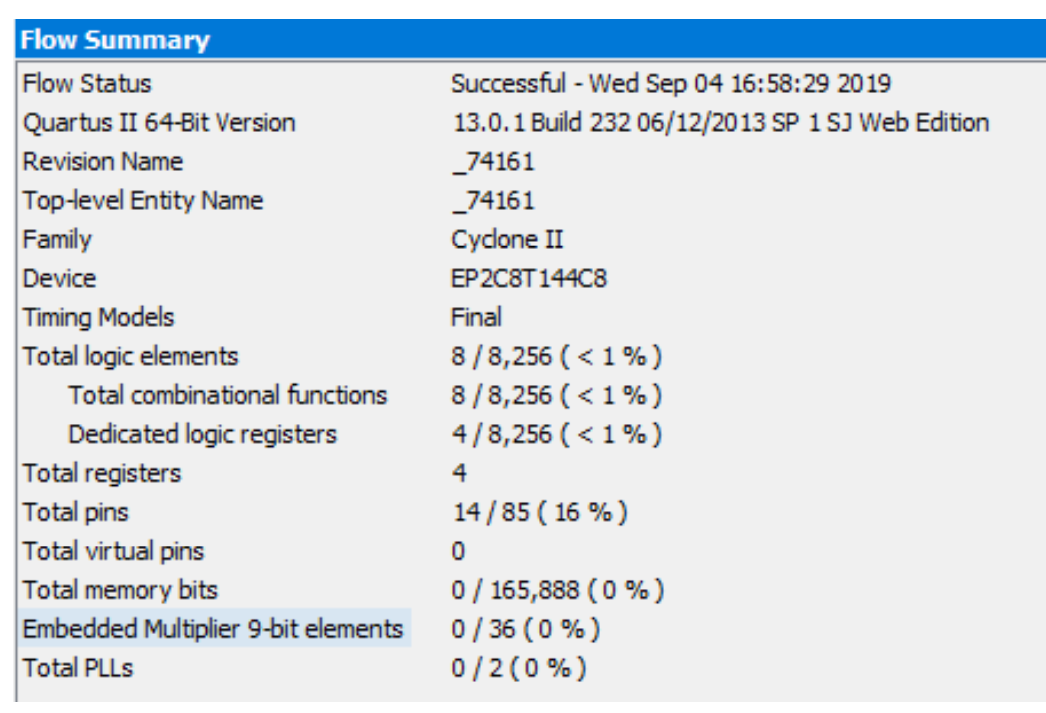

(3)选择菜单Processing--Start Compilation,分析并综合电路,若有错误请自行更正,截图代码和编译报告(Flow Summary);【5分】

(4)选择菜单Tools—Netlist Viewers—RTL Viewer,截图逻辑电路图;【5分】

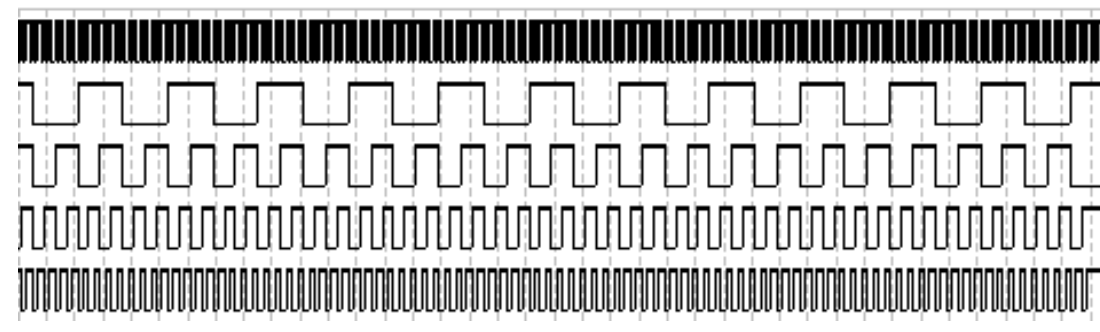

(5)建立仿真向量波形文件Waveform.vwf,运行功能仿真(Simulation—Run Functional Simulation),截图仿真结果【5分】并分析电路功能是否正确【5分】。

注:每一步都需要截图、打印、分析

2、数据流描述与仿真。【25分】

按照1中的步骤,新建工程名为:_学号_V1_1bit_adder_df(1位加法器数据流描述),完成数据流建模与仿真。

3、行为建模与仿真。【25分】

按照1中的步骤,新建工程名为:_学号_V1_1bit_adder_bh(1位加法器行为描述),完成行为建模与仿真。

4、2位二进制加电路结构化建模与仿真。【25分】

使用上面的加法器(3个中的任一个),对2位二进制加法器进行结构化建模与仿真(仿真向量Waveform.vwf1可在群文件中下载),模块名和端口定义如下:

_学号_V1_2bit_adder_st(a,b,ci,s,co); //2为二进制加法结构化建模

input a[1:0], b[1:0]; //a是2位被加数,b是2位加数

input ci; //低位来的进位输入

output co; //向高位的进位输出

output s[1:0]; //2位相加的和

其它要求同1

5、引脚锁定与下载测试

(1)查阅实验器使用说明书上的引脚号对照表,进行引脚锁定规划,填写实验报告中的引脚锁定表。将输入信号锁定到开关上(主板器件名SW0~SW15);将输出信号锁定到指示灯上(主板器件名LED0~LED7)。

(2)启动Quartus的引脚规划器Pin Planner,完成引脚锁定。

(3)重新编译整个工程,如有报错,请自行改正并重新编译通过。

(4)将下载线与实验器、电脑正确连接,并接通实验器电源。

(5)启动Programmer,将生成的工程同名sof文件用JTAG模式下载到实验器上的核心板。

(6)在实验器上测试、验证前述所设计的2位二进制加法器。

(7)将实测结果以真值表形式记录在实验报告的原始记录部分。

三、 预习要求

1、自行查找资料,自学Verilog HDL的层次化文件设计,完成本实验“实验内容”部分的设计要求。

2、对实验电路进行功能仿真,并将仿真结果截图插入报告中。

3、列出引脚锁定分配表(信号名->主板器件名->引脚号)。

4、填写编译报告。

四、 实验报告要求

1、列出通电测试结果。

2、列出实验过程出现的问题及解决措施。

3、代码和综合结果截图要求

(1)必须要有文件名(第一行红线处);

(2)代码和综合结果必须完整。

4. 仿真波形截图要求:

(1)必须要有文件名(第一行);

(2)信号名(左侧 name 列)必须清楚可读;

(3)波形必须清晰可读。

好的仿真波形示例

差的波形示例

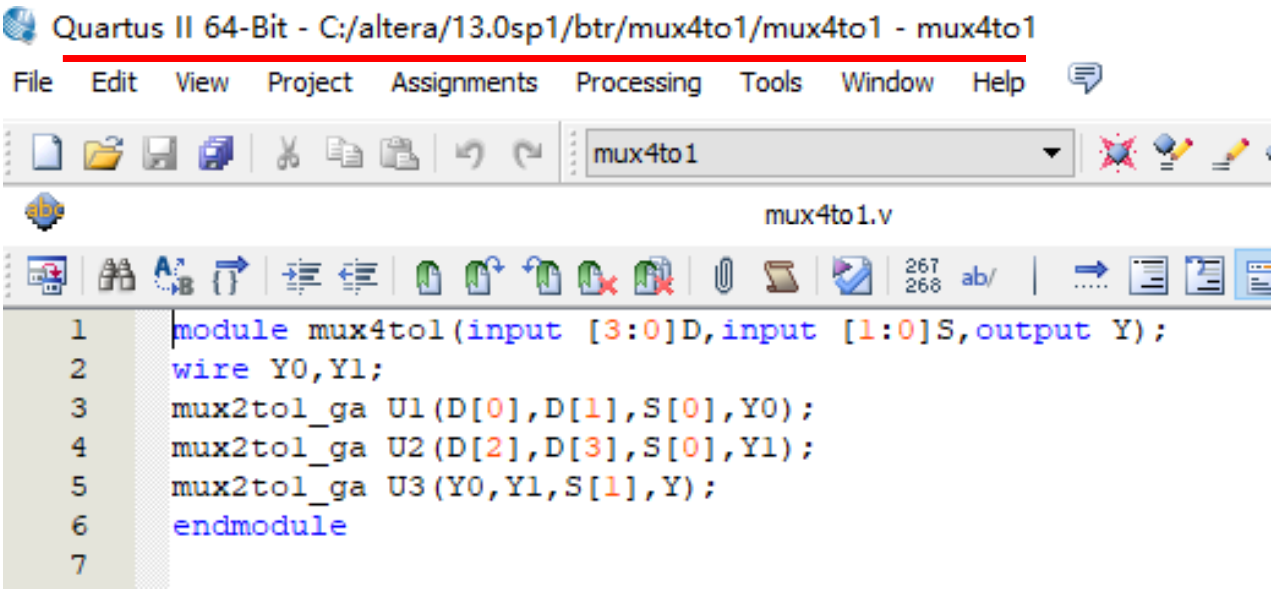

Verilog 代码及RTL电路图

一、门级描述与仿真

a.Verilog代码

module _1bit_adder_ga(X,Y,CIN,S,COUT);

input X,Y,CIN;

output S,COUT;

wire A1_xor;

wire A1_and,A2_and,A3_and;

xor

n1(A1_xor,X,Y),

n2(S,A1_xor,CIN);

and

n3(A1_and,CIN,X),

n4(A2_and,CIN,Y),

n5(A3_and,X,Y);

or

n6(COUT,A1_and,A2_and,A3_and);

endmodule b.RTL电路图

c.仿真结果

二、数据流描述与仿真

Verilog代码

module _1bit_adder_df(X,Y,CIN,S,COUT);

input X,Y,CIN;

output S,COUT;

assign S = X ^ Y ^ CIN;

assign COUT = (CIN & X) | (CIN & Y) | (Y & X);

endmoduleRTL电路图

仿真结果

三、行为建模与仿真

a.Verilog代码

module _1bit_adder_bh(X,Y,CIN,S,COUT);

input X,Y,CIN;

output S,COUT;

reg [2:0]A;

reg S,COUT;

always@(X,Y,CIN)

begin

A[2] <=X;

A[1] <=Y;

A[0] <=CIN;

end

always@(A)

begin

case(A)

3'b000:S <= 0;

3'b001:S <= 1;

3'b010:S <= 1;

3'b011:S <= 0;

3'b100:S <= 1;

3'b101:S <= 0;

3'b110:S <= 0;

3'b111:S <= 1;

endcase

case(A)

3'b000:COUT <= 0;

3'b001:COUT <= 0;

3'b010:COUT <= 0;

3'b011:COUT <= 1;

3'b100:COUT <= 0;

3'b101:COUT <= 1;

3'b110:COUT <= 1;

3'b111:COUT <= 1;

endcase

end

endmoduleb.RTL电路图

c.仿真结果

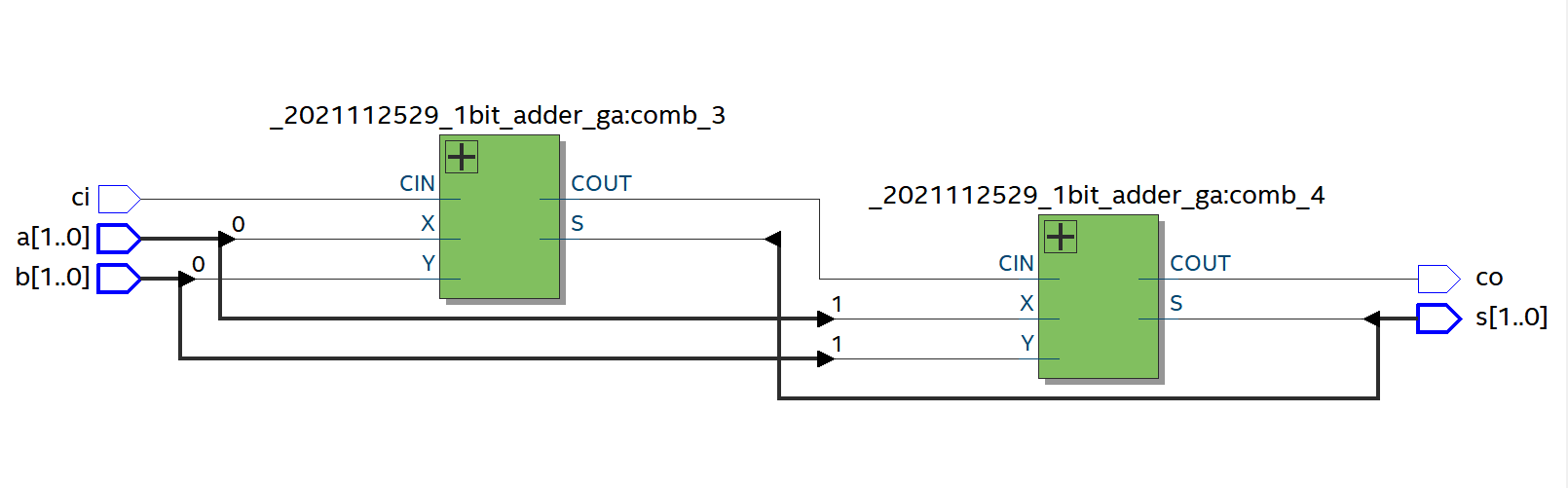

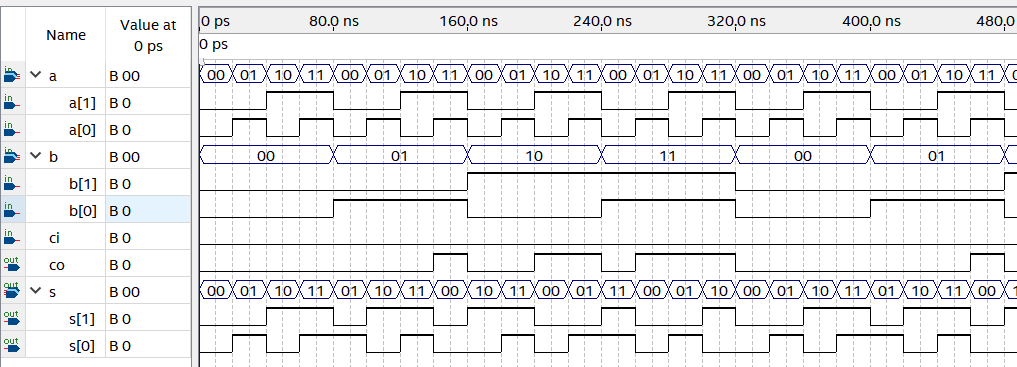

四、2位二进制加法电路结构化建模与仿真

a.Verilog代码

module _1bit_adder_ga(X,Y,CIN,S,COUT);

input X,Y,CIN;

output S,COUT;

wire A1_xor;

wire A1_and,A2_and,A3_and;

xor

n1(A1_xor,X,Y),

n2(S,A1_xor,CIN);

and

n3(A1_and,CIN,X),

n4(A2_and,CIN,Y),

n5(A3_and,X,Y);

or

n6(COUT,A1_and,A2_and,A3_and);

endmodule

module _2bit_adder_st(a,b,ci,s,co);

input[1:0] a,b;

input ci;

output co;

output[1:0] s;

wire d;

_1bit_adder_ga(a[0],b[0],ci,s[0],d);

_1bit_adder_ga(a[1],b[1],d,s[1],co);

endmodule b.RTL电路图

c.仿真结果

有什么问题欢迎评论区留言!感谢你的关注与支持!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?