module tb;

bit clk;

initial begin

forever #5ns clk <= !clk;

end

counter dut(clk);

initial begin

#500ns;

$finish();

end

endmodule

program pgm1;

initial begin : proc1

#100ns;

$display("$%0t p1.proc1 finished",$time);

end

initial begin : proc2

#400ns;

$display("$%0t p1.proc2 finished",$time);

end

endprogram

program pgm2;

initial begin : proc1

#200ns;

$display("$%0t p1.proc1 finished",$time);

end

initial begin : proc2

#300ns;

$display("$%0t p1.proc2 finished",$time);

end

endprogram

module tb;

bit clk;

initial begin

forever #5ns clk <=!clk;

end

counter dut(clk);

pgm1 p1();

pgm2 p2();

endmodule

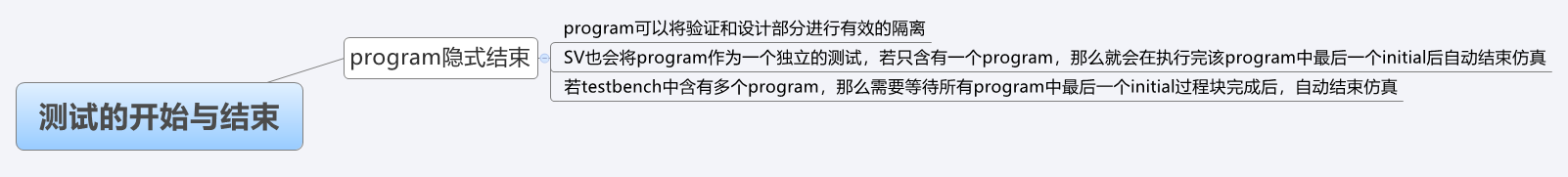

则仿真分别会在100 ns,200ns,300ns和400ns打印,在400ns时结束仿真。

如果initial语句一直运行下去,内置$exit()来强行结束。

2561

2561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?