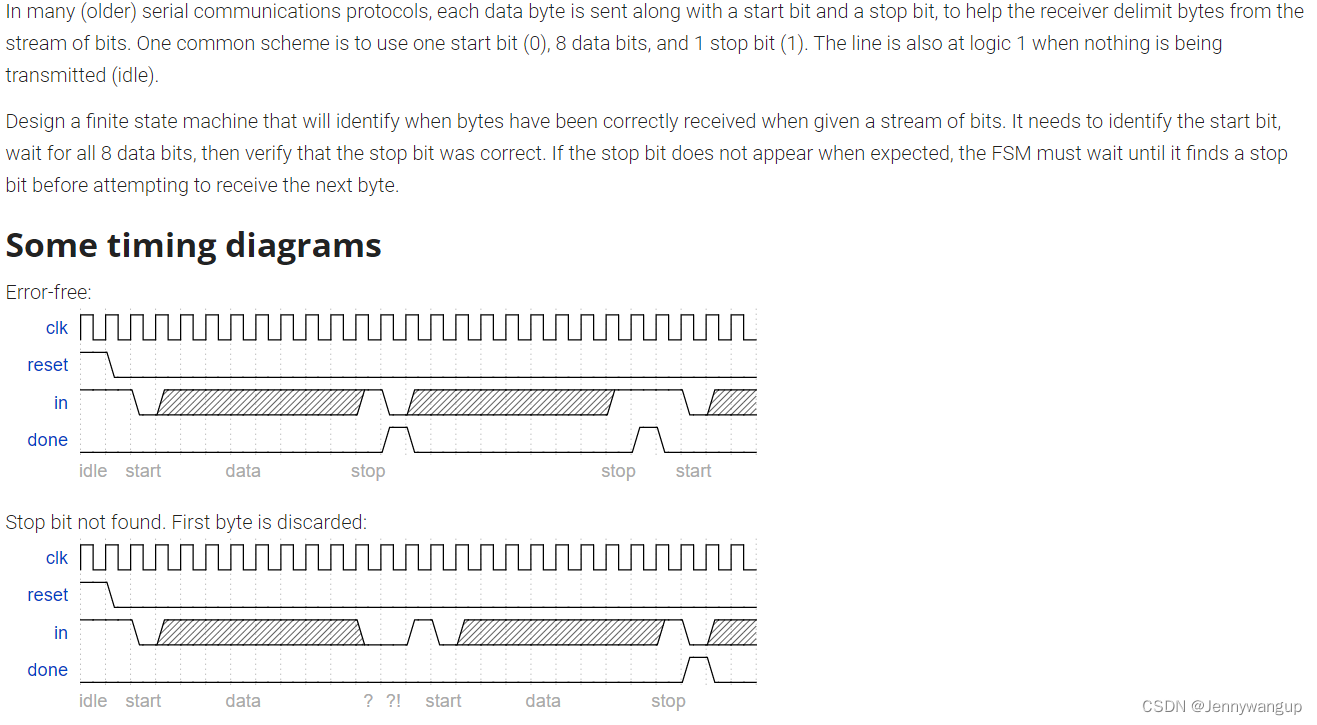

首先,这个题的主要思路是计数器加状态机。

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output done

);

parameter IDLE = 3'd0, START = 3'd1, DATA = 3'd2, STOP = 3'd3, ERROR = 3'd4;

reg[3:0]STATE, NEXT_STATE;

reg[3:0]COUNT1;

always @ (*) begin

case(STATE)

IDLE:NEXT_STATE = in ? IDLE : START;

START:NEXT_STATE = DATA;

DATA: NEXT_STATE = (COUNT1 == 4'd7)? (in ? STOP : ERROR) : DATA;

STOP: NEXT_STATE = in ? IDLE : START;

ERROR: NEXT_STATE = in ? IDLE : ERROR;

default: NEXT_STATE = IDLE;

endcase

end

always @ (posedge clk)begin

if(reset)begin

STATE <= IDLE;

end

else begin

STATE <= NEXT_STATE;

end

end

always @ (posedge clk)begin

if(reset)begin

COUNT1 <= 4'd0;

end

else if(COUNT1 == 4'd7)begin

COUNT1 <= 4'd0;

end

else if(STATE == DATA)begin

COUNT1 <= COUNT1 + 1'b1;

end

end

assign done = (STATE == STOP);

endmodule

134

134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?