题目描述

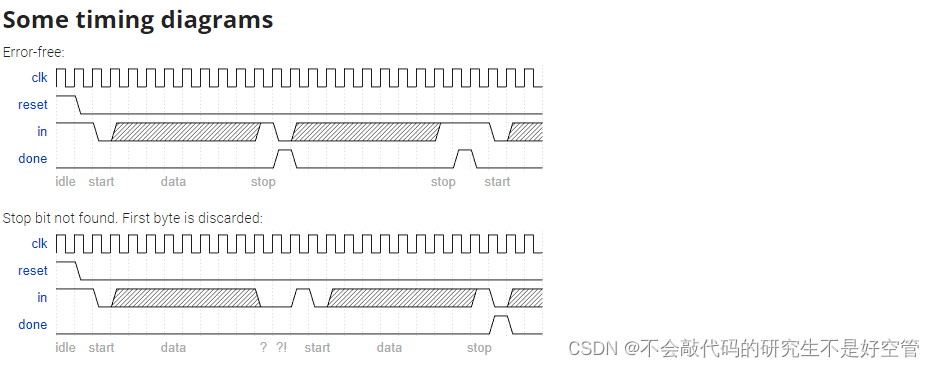

In many (older) serial communications protocols, each data byte is sent along with a start bit and a stop bit, to help the receiver delimit bytes from the stream of bits. One common scheme is to use one start bit (0), 8 data bits, and 1 stop bit (1). The line is also at logic 1 when nothing is being transmitted (idle).

Design a finite state machine that will identify when bytes have been correctly received when given a stream of bits. It needs to identify the start bit, wait for all 8 data bits, then verify that the stop bit was correct. If the stop bit does not appear when expected, the FSM must wait until it finds a stop bit before attempting to receive the next byte.

代码

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output done

);

parameter idle=0,start=1,b1=2,b2=3,b3=4,b4=5,b5=6,b6=7,b7=8,b8=9,stop=10,error=11;

reg[3:0] state,next_state;

always@(*)

case(state)

idle:next_state=(~in)?start:idle;

start:next_state=b1;

b1:next_state=b2;

b2:next_state=b3;

b3:next_state=b4;

b4:next_state=b5;

b5:next_state=b6;

b6:next_state=b7;

b7:next_state=b8;

b8:next_state=in?stop:error;

stop:next_state=(~in)?start:idle;

error:next_state=in?idle:error;

endcase

always@(posedge clk)

if(reset)

state<=idle;

else

state<=next_state;

assign done = (state==stop);

endmodule

结果

150

150

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?