-分布延迟:将延迟值赋给电路中独立的门,或是在单独的assign语句中指定延迟值。

-集总延迟:将所有路径的积累延迟汇总于输出门处。

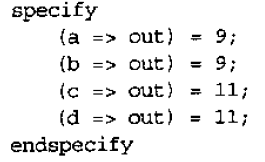

-引脚到引脚的延迟:分别把延迟给模块中从每个输入到每个输出之间的所有路径。

-路径延迟建模:在模块的源引脚(输入或输入输出)和目标引脚(输出或输入输出)之间的延迟称为模块路径延迟。

-specify块:关键字specify-endspecify;包含:给穿过模块的所有路劲指定引脚到引脚的时序延迟;在电路中设置时序检查;定

义specparam常量;

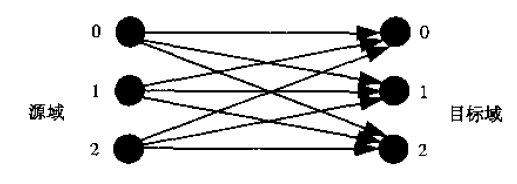

-并行连接:位与位对应连接

![]()

-全连接:

![]()

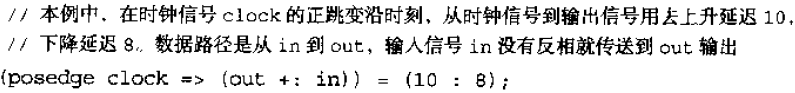

-边沿敏感路径:

-specparam声明语句:用于在specify中定义参数。

-条件路径延迟(状态以来路径延迟SDPD):关键字if(不能使用else)

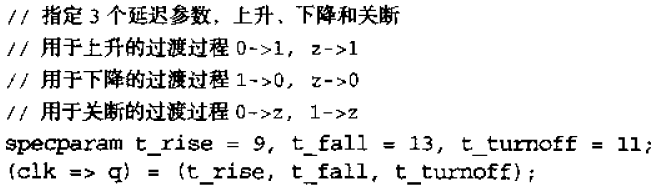

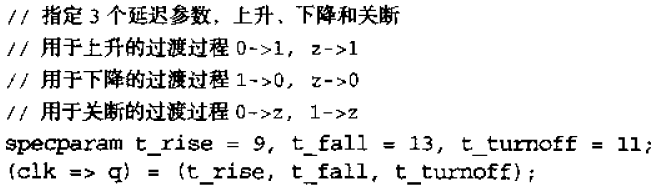

-上升、下降、关断延迟:给任意路径定义1、2、3、6、12个延迟。

-1个:

-2个:

-3个:

-6个:

-12个:

-最小值、最大值、典型延迟值:(min:typ:max)

-处理x状态转换:

1、从x到已知状态的转换应当消耗可能的最大时间;

2、从已知状态到x的转换应当消耗可能的最小时间;

-时序检查

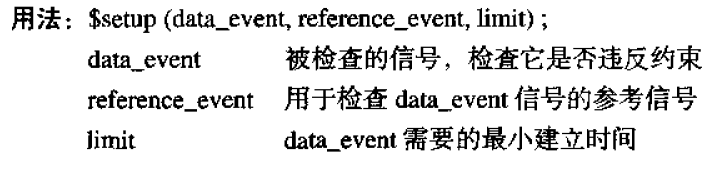

-$setup与$hold:检查设计中时序元件的建立和保持约束。

1、建立时间是数据必须在有效时钟边沿之前到达的最小时间;

2、保持时间是数据在有效时钟边沿之后保持不变的最小时间。

-$setup:

如果(Treference - Tdata_event)< limit 则报告违反约束

-$hold:

如果(Tdata_event - Treference)< limit 则报告违反约束

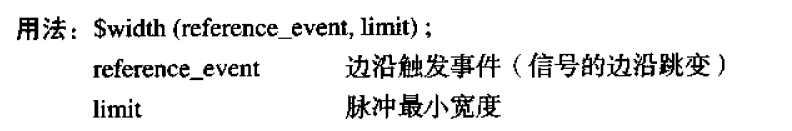

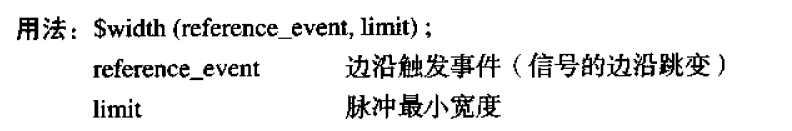

-$width:检查脉冲宽度是否满足最小宽度要求。

违约条件同setup与hold

用于检查信号值从一个跳变的下一个跳变之间的时间,data_event是reference_event信号的下一个反向跳变沿。

1211

1211

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?