IC618-偏置电路仿真,要求电源电压2.7V~3.3V

1、仿真以计算MOS管 μ C o x \mu C_{ox} μCox参数

参考https://blog.csdn.net/m0_51258866/article/details/130115911

这篇文章里的vth算出来好低,感觉不太对,应该是数据跨度太小了

由考虑沟道长度调制效应的电流方程:

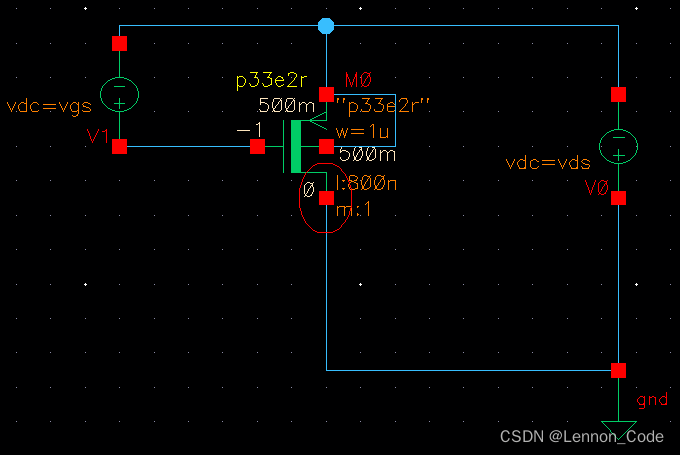

先仿真PMOS管:

W/L=1/0.8

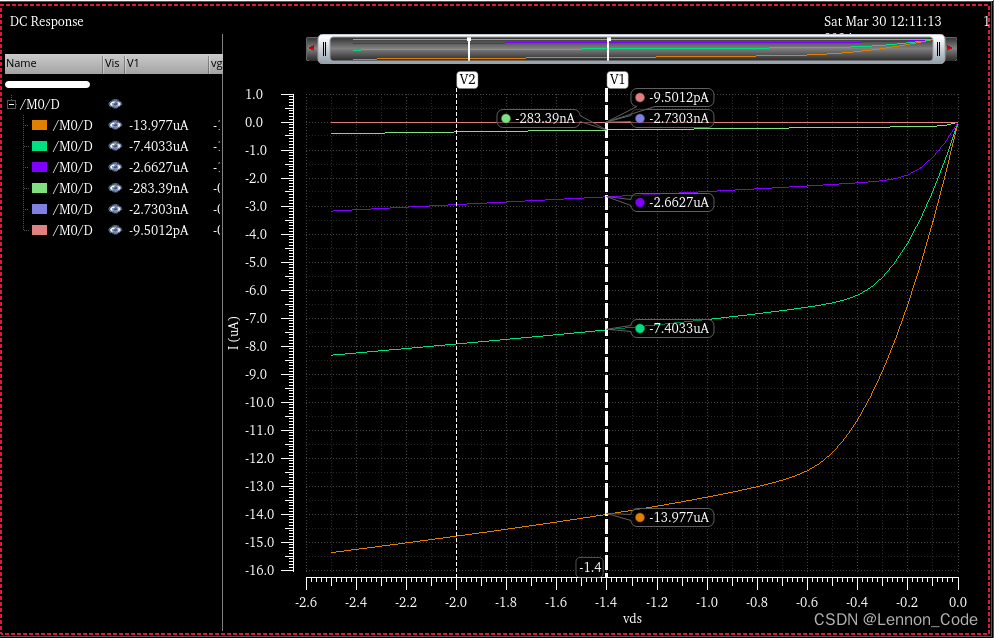

将vgs作为parameter扫描,范围设置为-1.5至-0.5V,扫描6个点,vds作为自变量,扫描范围为-2.5V至0V,因变量为漏端电流。

插入Marker,选取vds=-1.4V和-2.0V

选取两组数据,

| I D I_D ID | Vds=-1.4V | Vds=-2V |

|---|---|---|

| Vgs=-1.1V | -2.663μA | -2.940μA |

| Vgs=-1.5V | -13.997μA | -14.755μA |

代入公式计算:

I

D

=

−

1

2

μ

p

C

o

x

W

L

(

V

G

S

−

V

t

h

p

)

2

(

1

+

λ

V

D

S

)

I_D = -\frac{1}{2} \mu_p C_{ox} \frac{W}{L} (V_{GS} - V_{thp})^2 (1 + \lambda V_{DS})

ID=−21μpCoxLW(VGS−Vthp)2(1+λVDS)

解得 λ=-0.229

Vth=-0.790

///

μ

p

C

o

x

=

33.574

μ

A

/

V

2

\mu_p C_{ox}=33.574\mu A/V^2

μpCox=33.574μA/V2

但直接查看直流参数发现,Vth为-0.84V

作出修正:

μ

n

C

o

x

=

47.728

μ

A

/

V

2

\mu_n C_{ox}=47.728\mu A/V^2

μnCox=47.728μA/V2

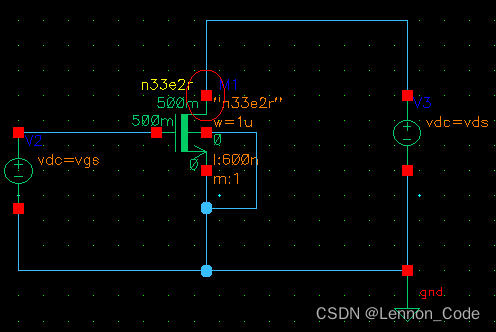

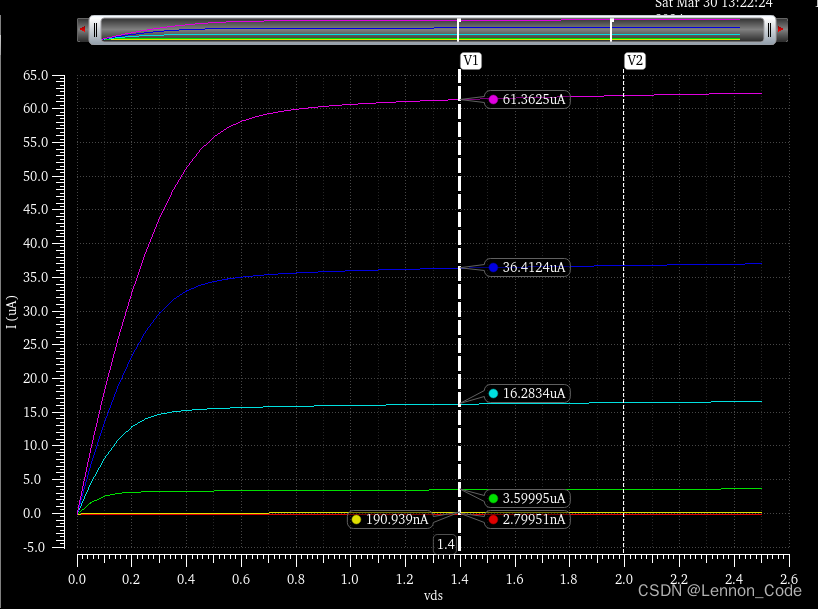

同理仿真NMOS

W/L=1/0.6

解得 λ=0.023

Vth=0.68

///

μ

n

C

o

x

=

107.313

μ

A

/

V

2

\mu_n C_{ox}=107.313\mu A/V^2

μnCox=107.313μA/V2

但直接查看直流参数发现,Vth为0.79V

作出修正:

μ

n

C

o

x

=

196.983

μ

A

/

V

2

\mu_n C_{ox}=196.983\mu A/V^2

μnCox=196.983μA/V2

综上所仿真结果:

PMOS:λ=-0.229,Vth=-0.84,

μ

p

C

o

x

=

47.728

μ

A

/

V

2

\mu_p C_{ox}=47.728\mu A/V^2

μpCox=47.728μA/V2

NMOS:λ=0.023 ,Vth=0.79 ,

μ

n

C

o

x

=

196.983

μ

A

/

V

2

\mu_n C_{ox}=196.983\mu A/V^2

μnCox=196.983μA/V2

2、计算宽长比(校正!注意!!)

考虑每路电流限制5

μ

A

\mu A

μA

取过驱动电压为0.2V

结合上面计算的工艺常数,代入得

(

W

/

L

)

P

(W/L)_P

(W/L)P=5.24 ,取5

(

W

/

L

)

N

(W/L)_N

(W/L)N=1.27 ,取1

大致取L为数倍的工艺值,180nm工艺,不妨

取L为0.9um,则

W

P

W_P

WP=4.5um,

W

N

W_N

WN=0.9um

上述的λ应该写作λ*600nm,现在是900nm,有偏差。

另外,在搭建反相器的过程中,发现5:1不能使中间电位位于vcc/2,仿真后,调整PMOS和NMOS的宽长比之比为:2.6:1,大致处于中间电位。

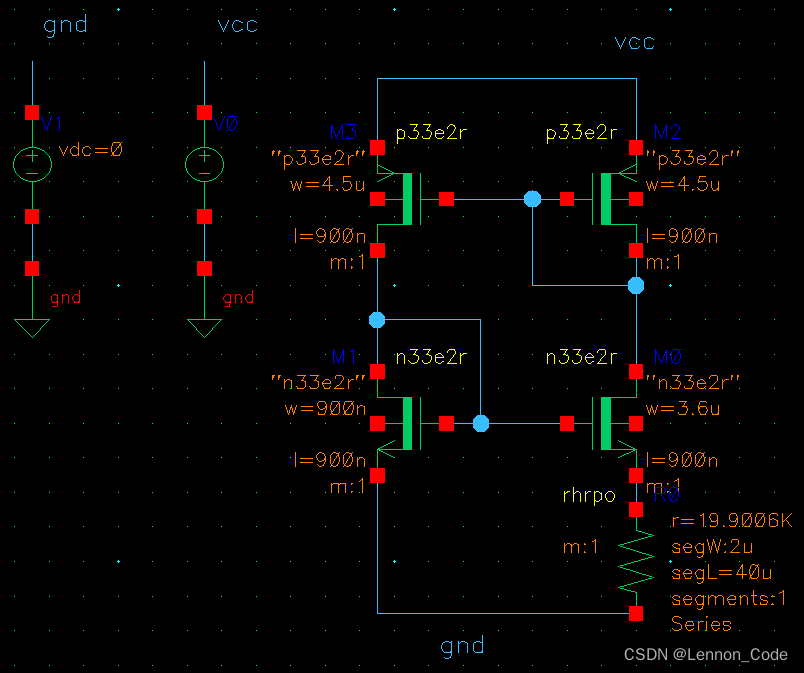

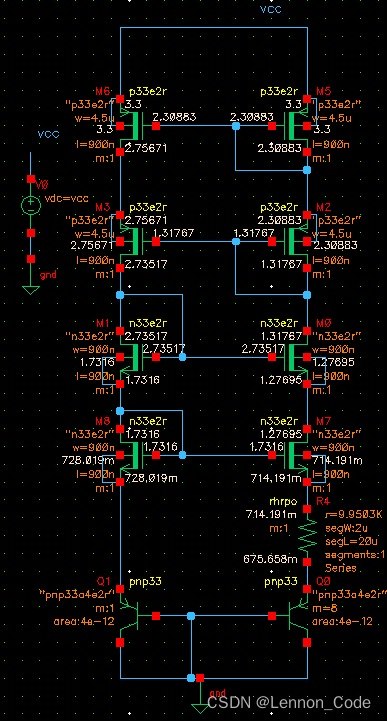

3、搭建偏置电路

1)MOS 最基本的架构(有1倍误差,原因待分析)

先采用最基本的架构,线性+非线性,构成偏置输出

此电路电流公式为:

I

D

=

2

(

N

−

1

)

2

K

1

N

R

1

2

I_D = \frac{2(\sqrt{N}-1)^2}{K_1 NR_1 ^2}

ID=K1NR122(N−1)2

按照上方已规定的,

I

D

I_D

ID=5uA,

另外取N=4,而

K

1

K_1

K1=

(

W

/

L

)

N

∗

μ

n

C

o

x

(W/L)_N *\mu_n C_{ox}

(W/L)N∗μnCox=

μ

n

C

o

x

=

196.983

μ

A

/

V

2

\mu_n C_{ox}=196.983\mu A/V^2

μnCox=196.983μA/V2

代入可得

R

1

R_1

R1约为20

k

Ω

k\Omega

kΩ

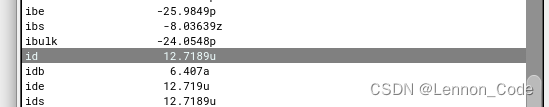

仿真结果

显示电流达到了12.7uA,达到理论5uA 2.5倍,问题出在哪里?

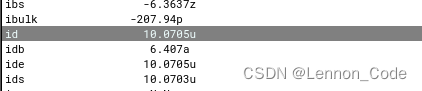

换成无衬篇效应结构,

变小了点,但还是2倍即10uA.

原因待分析

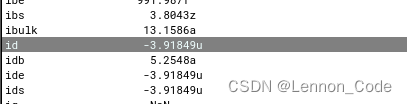

先通过提高R1把电流降下来

调整至32

k

Ω

k\Omega

kΩ

电流:3.92uA

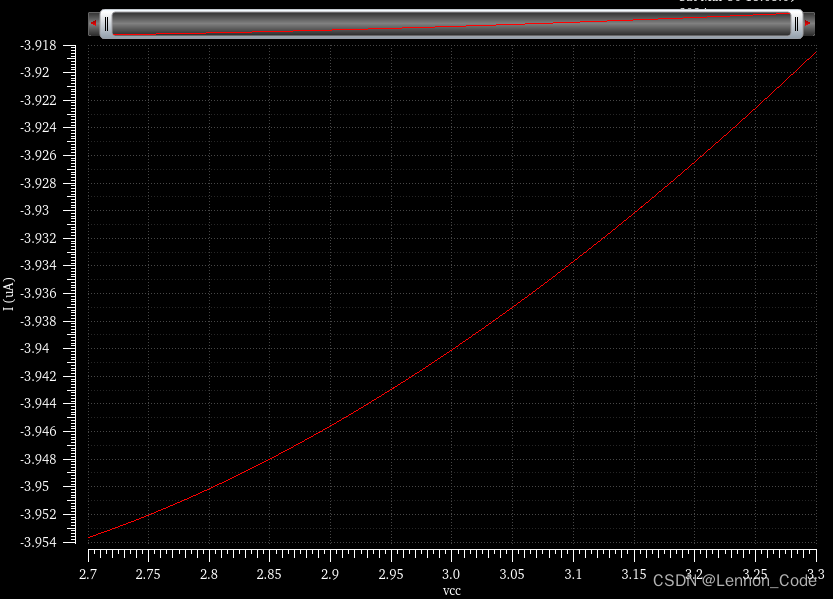

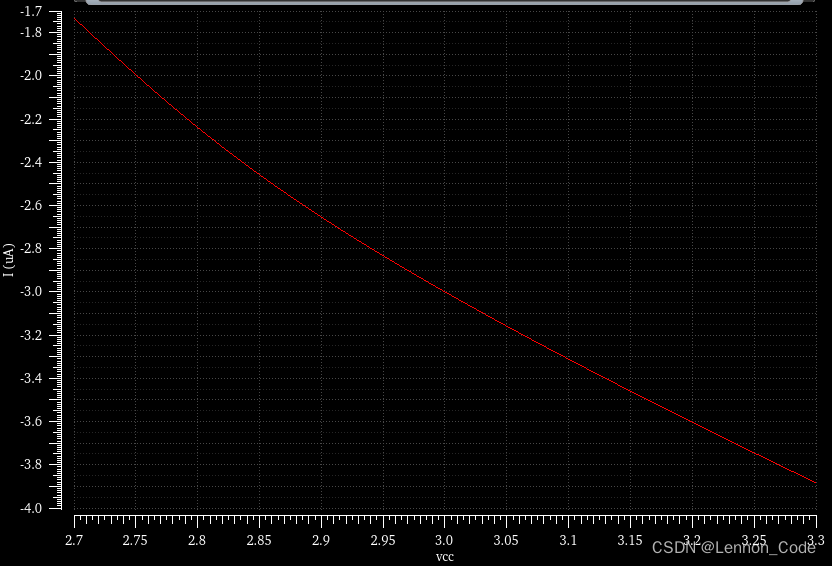

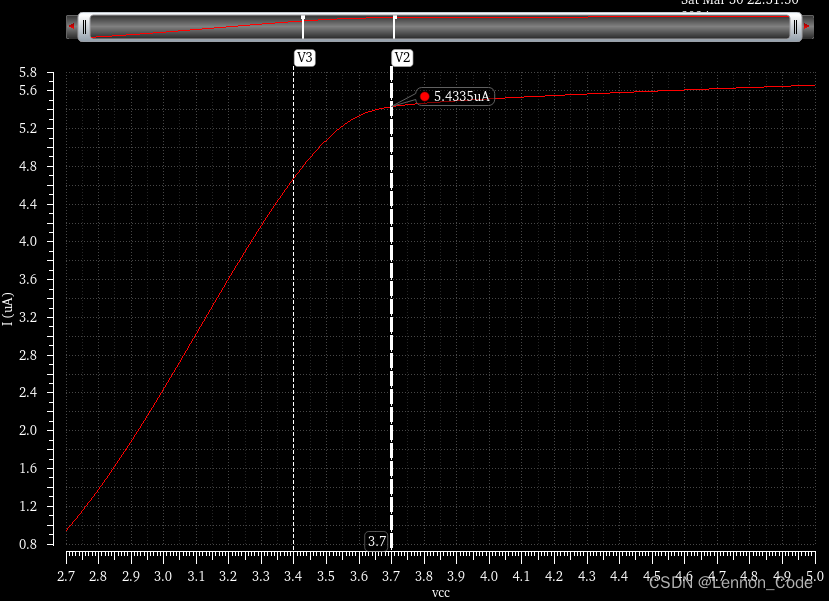

扫描电流随VCC变化曲线:

vcc2.7V至3.3V

基本无变化。

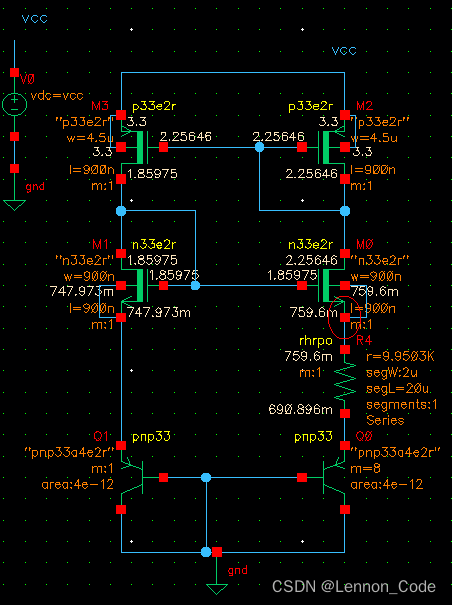

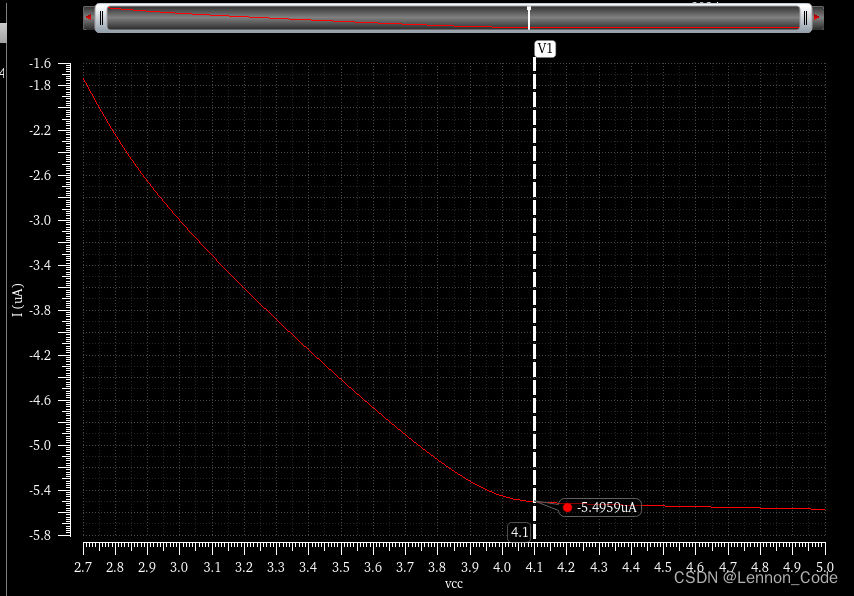

2)把下方mos换成晶体管

电流公式为:

I

D

=

Δ

V

B

E

R

=

V

T

l

n

N

R

I_D = \frac{\Delta V_{BE}}{R} = \frac{V_T lnN}{R}

ID=RΔVBE=RVTlnN

N可取8,12,16

此处取8,代入得R=10

k

Ω

k\Omega

kΩ

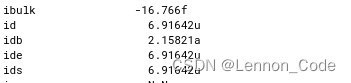

仿真结果

电流为6.9uA,偏大

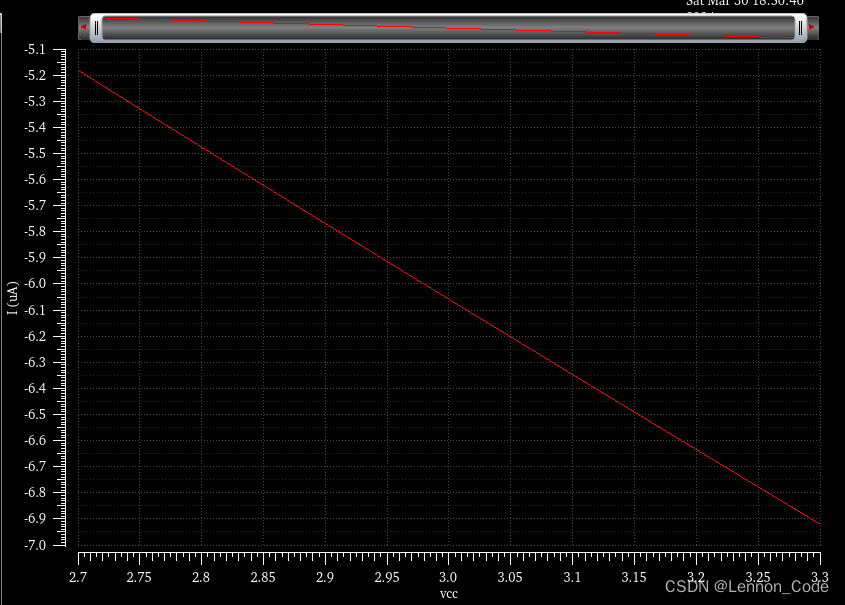

扫描电流随VCC变化曲线:

可以看到,电流有明显变化

为什么?

因为上方不是理想的恒流源,要考虑沟道长度调制效应,故vcc变化时,会影响电流变化。

怎么影响的?待分析

下面进行优化:

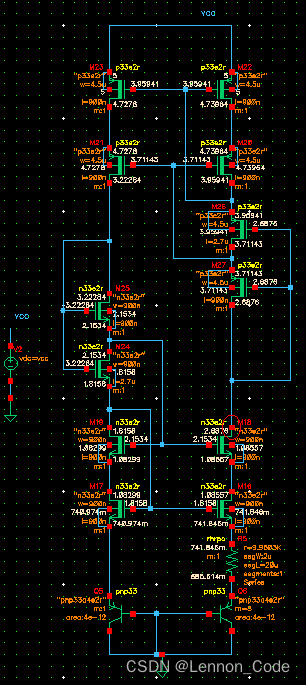

3)引入Cascode结构,增大恒流源输出阻抗

扫描电流随VCC变化曲线:

为什么电流变化仍然很大? 哪个环节出了问题呢

找到原因了,电压不够,扫描如下:

进行压降分析:

按照Vthp=0.9V,

Δ

=

0.2

V

\Delta =0.2V

Δ=0.2V来估算,即一个Vgs为1.1V

重要:则从地开始,共计上升了:0.8(BJT-diode)+ 3Vgs + Δ \Delta Δ =0.8+3.5=4.3V,3.3V电源无法满足

因此,需要旁路放大式Cascode或宽摆幅Cascode:

宽摆幅方案1不知道怎么做

4)采用宽摆幅Cascode方案2:

扫描电流随VCC变化曲线:

仍然不足

宽摆幅方案2相比正常方案能够减少一个vgs-

Δ

\Delta

Δ,即减少一个Vthn (由于P的Vth大,Nmos可工作Pmos不一定工作,所以减小的)大约为0.8V

也就是说,现在仍然需要4.3-0.8=3.5V 才能工作

可是偏置电路是不是也需要一个

Δ

\Delta

Δ 呢,这样似乎要3.7V才工作。

且实测表明,pmos的电流输出端,直到电源电压达到3.7V时,才进入饱和区

无论如何,由于晶体管的存在,结合常规及宽摆幅的cascode结构,仍需要较大的压降,

因此,需要结合运放或放大电路进行设计。

是不是可以不用晶体管?

5)采用旁路放大型(Regulate型)Cascode,即以增加两条放大器支路为代价,换取低压。

此时所需电压为BJT0.8V + vgs +

Δ

\Delta

Δ = 2.1V 即可。

但实际上,此电路好像不适用于2层改1层,只适合3层cascode改两层cascode.

6)采用运放构造等电位点?

待继续

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?