摘要:

本能篇主要讲一下AXI GPIO 中断,AXI GPIO 中断也是共享外设中断的一种。本讲和上一讲说的中断很像,区别就是AXI GPIO 中断需要AXI GPIO核。

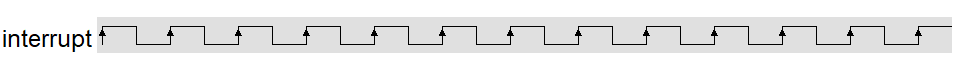

本章也是使用PL逻辑产生一组方波信号来做中断信号,方波的周期也是2秒。如下图L:

中断信号

产生的中断信号捅进AXI_GPIO0,然后输入到ZYNQ中。同时将AXI_GPIO0的中断信号连接到ZYNQ的中断输入端口。ZYNQ对中断做出响应,在中断处理函数里面读取AXI_GPIO0的值,再通过AXI_GPIO1写到LED灯上,通过LED灯来观察中断响应。同时也可以通过串口来打印响应的信息来观察中断响应的情况。

一、创建Block Design模块

整体结构如下:

说明:

a、通过PL逻辑产生中断方波信号,输入到sws_8bits.

b、从FCLK_CLK0引出CLK_100M信号

c、从FCLK_RESET0_N引出FCLK_RESET0_N信号

1、配置ZYNQ

勾选PL到PS的中断

2、引出两路时钟

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

576

576

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?