前言:前面学了一种多速率滤波器——CIC滤波器的原理和具体的FPGA实现,本节则介绍另一种非常适合于2倍抽取的FIR滤波器——半带滤波器的原理和FPGA实现。

目录

一、半带滤波器的简介

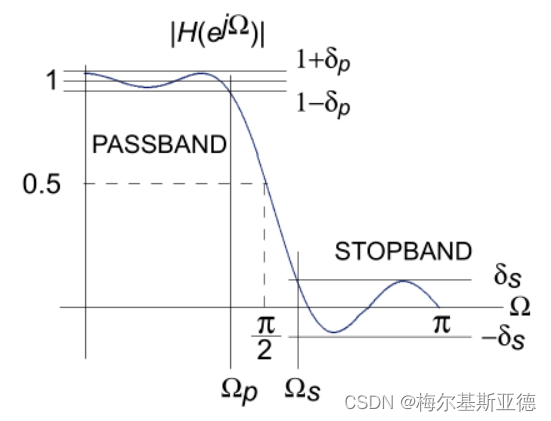

半带滤波器是一种特殊的FIR滤波器,其通带容限与阻带容限相等,滤波器的系数具有偶对称特性,长度为奇数,阶数为偶数,除了中间的系数不为0以外,其余的奇数抽头系数均为0,这使得运算时所需要的乘法和加法次数大大减少。

图1半带滤波器的频率特性

图2半带滤波器的系数分布

2倍抽取后,滤波器频率响应以π为周期,由于通带容限与阻带容限相等,故通带内没有频谱混叠,但过渡带会有频谱混叠。

二、多级半带滤波器的设计

M级半带滤波器可以实现倍抽取,因各级滤波器后均需2倍抽取,故每级滤波器的通带阻带容限均不相同,为了便于设计,令每级容限

为

式中,为各级半带滤波器的通带误差容限,K为总的级数,

为系统的通带误差容限。

信号抽样的频率为,信号要求半带滤波器的通带上限截止频率为

,阻带下限频率为

。为了避免混叠,取

,这也是多级半带滤波器最后一级对通/阻容限的要求。

实验:设计多级半带滤波器,输入信号抽样频率3200Hz,输入数据位宽8bit,有用信号的通带截止频率fp=20Hz ,阻带截止频率fs=25Hz 。要求将信号的抽样频率减小到50Hz,通带/阻带容限为0.001。

1、使用matlab获得该多级半带滤波器的各级系统函数系数

根据要求,得到系统级数为6级,故前5级是半带滤波器,第6级是一般的FIR滤波器,注意滤波器的抽取倍数都是2。前5级的通带上限频率均为20Hz,最后一级滤波器的通带上限频率为20Hz,阻带下限频率为25Hz,通带容限均为0.001/6。

matlab代码如下:

fp = 20;

fs = 25;

F0 = 3200;

Fout = 50;

dev = 0.001;

D = log2(F0/Fout);

devi = dev/D;

fpi = zeros(1,D-1);

for i=1:D-1

fpi(i) = 20*(2^i)/F0;

end

b1 = firhalfband('minorder',fpi(1),devi);

b2 = firhalfband('minorder',fpi(2),devi);

b3 = firhalfband('minorder',fpi(3),devi);

b4 = firhalfband('minorder',fpi(4),devi);

b5 = firhalfband('minorder',fpi(5),devi);

fc = [20 25];mag = [1 0];devk = [devi dev];

[n,wn,belt,type] = kaiserord(fc,mag,devk,Fout*2);

fpm = [0 fc(1)*2/Fout/2 fc(2)*2/Fout/2 1];

magpm = [1 1 0 0];

b6 = firpm(n,fpm,magpm);L6 = length(b6);采用firhalfband('minorder',fp,dev);函数设计前5级半带滤波器,最后一级使用一般方法设计FIR滤波器。

2、使用matlab产生测试信号

测试信号由10Hz、25Hz、400Hz、1000Hz的单音信号组成,可以预见经过滤波器后只剩10Hz信号,后面会进行验证。

matlab代码如下:

f1 = 10;

f2 = 25;

f3 = 400;

f4 = 1000;

fs = 3200;

t = 0:1/fs:100;

s1 = sin(2*pi*f1*t);

s2 = sin(2*pi*f2*t);

s3 = sin(2*pi*f3*t);

s4 = sin(2*pi*f4*t);

s = s1 + s2 + s3 + s4 ;3、使用FPGA实现各级滤波器

半带滤波器是特殊的低通FIR数字滤波器,前面已经有过设计FIR滤波器的经验,这里为了方便,采用altera自带的FIR ip核进行设计。

图3 第一级FIR ip核的配置

需要注意的是输出数据的位宽问题,由于输入数据8bit量化,滤波器系数12bit量化,通过仿真可知第一级半带滤波器的输出数据最大绝对值是输入数据的3435倍,小于倍,故输出数据位宽为20bit;第二级半带滤波器的输出数据最大绝对值是输入数据的3325倍,则第二级输出位宽为32bit,第三级半带滤波器的输出数据最大绝对值是输入数据的4096倍,由于FIR ip核输出最大只有32bit,则第三级输出位宽为应该取输出的高32位,其余同理。最终数据设为20bit,则取整个系统输出的高20位即可。

verilog代码如下:

module multhalfband

(

input clk , //输入频率3200Hz

input rst ,

input signed [7:0] xin , //输入数据8bit

output signed [19:0] yout , //滤波后输出数据,50Hz

output rdy

);

wire coeff_in_clk = 1'b1;

wire ast_source_ready = 1'b1;

wire ast_sink_valid = 1'b1;

wire ast_sink_error = 2'b00;

wire source_valid[6:0];

wire [1:0] source_error[6:0];

wire sink_ready[6:0];

wire [19:0] y1;

hf_1 u1

(

.clk (clk),

.reset_n (rst),

.ast_sink_data (xin),

.ast_sink_valid (ast_sink_valid),

.ast_source_ready (ast_source_ready),

.ast_sink_error (ast_sink_error),

.ast_source_data (y1),

.ast_sink_ready (sink_ready[1]),

.ast_source_valid (source_valid[1]),

.ast_source_error (source_error[1])

);

wire [31:0] y2;

hf_2 u2

(

.clk (clk),

.reset_n (rst),

.ast_sink_data (y1),

.ast_sink_valid (source_valid[1]),

.ast_source_ready (ast_source_ready),

.ast_sink_error (ast_sink_error),

.ast_source_data (y2),

.ast_sink_ready (sink_ready[2]),

.ast_source_valid (source_valid[2]),

.ast_source_error (source_error[2])

);

wire [43:0] y3;

hf_3 u3

(

.clk (clk),

.reset_n (rst),

.ast_sink_data (y2),

.ast_sink_valid (source_valid[2]),

.ast_source_ready (ast_source_ready),

.ast_sink_error (ast_sink_error),

.ast_source_data (y3),

.ast_sink_ready (sink_ready[3]),

.ast_source_valid (source_valid[3]),

.ast_source_error (source_error[3])

);

wire [44:0] y4;

hf_4 u4

(

.clk (clk),

.reset_n (rst),

.ast_sink_data (y3[43:12]),

.ast_sink_valid (source_valid[3]),

.ast_source_ready (ast_source_ready),

.ast_sink_error (ast_sink_error),

.ast_source_data (y4),

.ast_sink_ready (sink_ready[4]),

.ast_source_valid (source_valid[4]),

.ast_source_error (source_error[4])

);

wire [44:0] y5;

hf_5 u5

(

.clk (clk),

.reset_n (rst),

.ast_sink_data (y4[43:12]),

.ast_sink_valid (source_valid[4]),

.ast_source_ready (ast_source_ready),

.ast_sink_error (ast_sink_error),

.ast_source_data (y5),

.ast_sink_ready (sink_ready[5]),

.ast_source_valid (source_valid[5]),

.ast_source_error (source_error[5])

);

wire [45:0] y6;

hf_6 u6

(

.clk (clk),

.reset_n (rst),

.ast_sink_data (y5[43:12]),

.ast_sink_valid (source_valid[5]),

.ast_source_ready (ast_source_ready),

.ast_sink_error (ast_sink_error),

.ast_source_data (y6),

.ast_sink_ready (sink_ready[6]),

.ast_source_valid (source_valid[6]),

.ast_source_error (source_error[6])

);

assign yout = y6[43:24];

assign rdy = source_valid[6];

endmodule其实就是依次连接6个ip核,最后得到系统输出,代码十分简单。

4、对FPGA滤波后的数据用matlab仿真测试

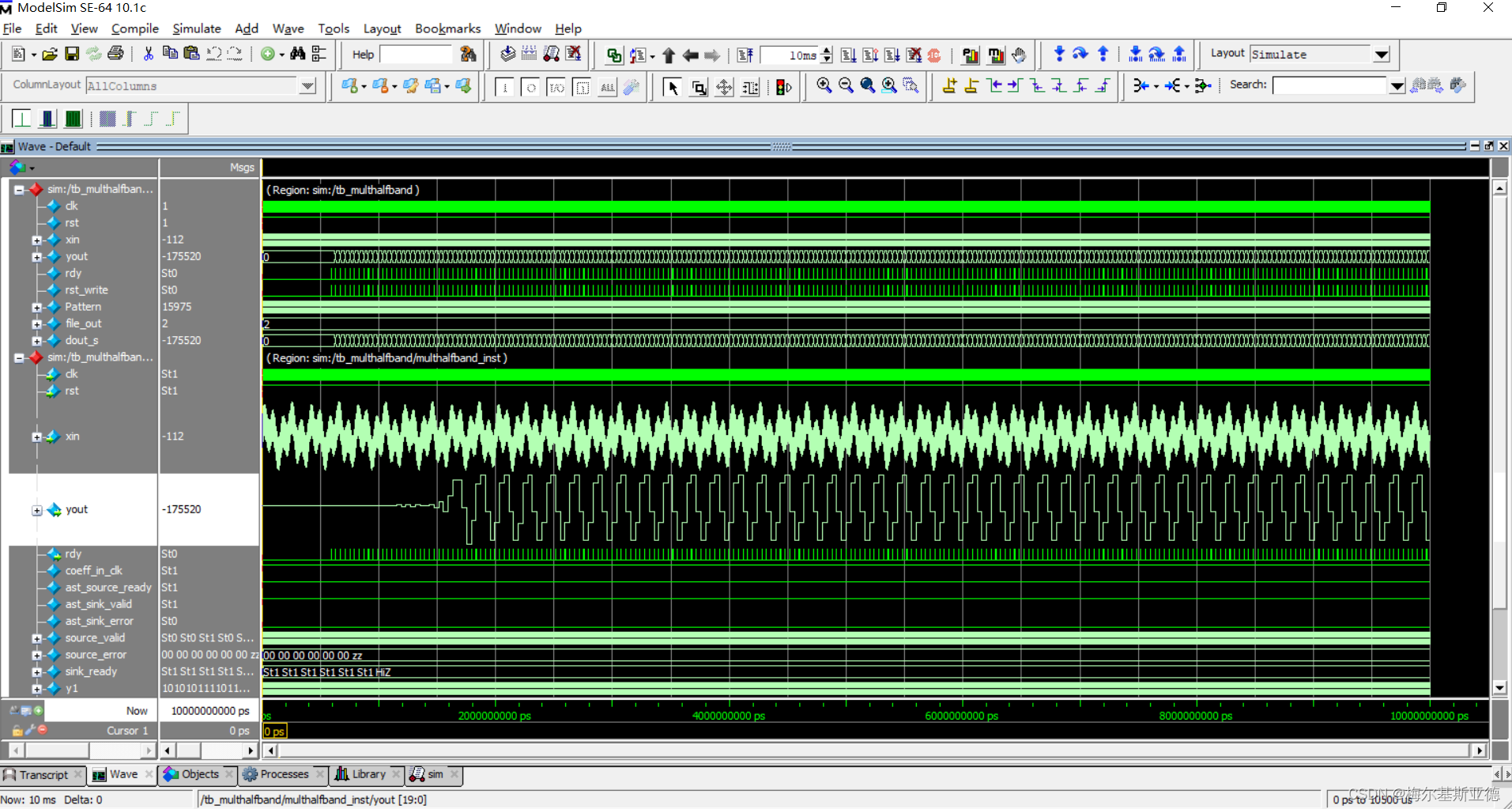

编写仿真测试文件,对测试数据进行仿真,查看modelsim仿真结果

图4 FPGA仿真结果

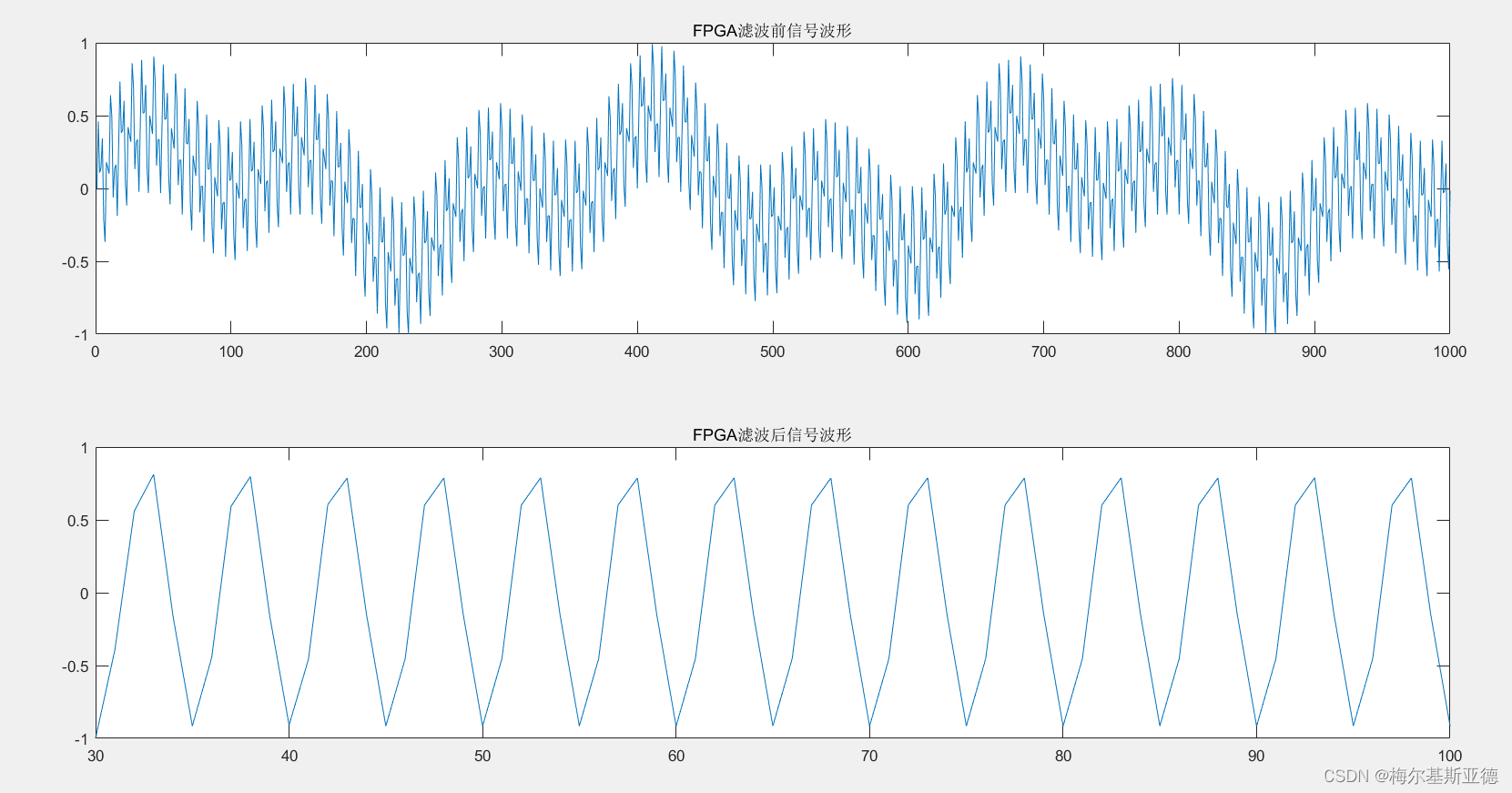

虽然可以看出的确将信号进行了滤波,得到了单音信号,但不能直观地看出是否降低了信号的抽样频率,这里依然是采用modelsim与matlab联调的方法,将FPGA滤波的数据保存下来,然后使用matlab读取数据进行分析

图5 matlab观察仿真结果(一)

图5 matlab观察仿真结果(二)

结果表明,与前面的猜想一致,该多级半带滤波器确实将10Hz信号保留下来,同时将抽样频率降低到了50Hz。

至此,完成了实验目标,本人也对半带滤波器有了更深入的理解。

参考文献:

[1] 杜勇.数字滤波器的MATLAB与FPGA实现——Altera/Verilog版(第二版).北京:电子工业出版社,2019

3936

3936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?