一. 硬件资源

- AD芯片(TLC549)

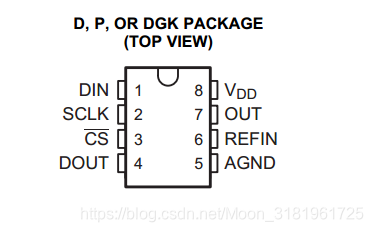

- DA芯片(TLC5615)

- LCD1602/LCD12864接口

- 6个独立按键

- 液晶背光可通过电位器(U6)调节

- 自带模拟测试信号,可通过(U20)调节测试信号幅值大小

二. 模数转换(AD转换)

1.知识背景

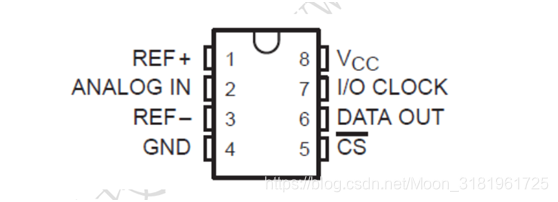

AD芯片采用TLC549,该芯片的功能为将模拟信号转换成数字信号。通常的模数转换器是将一个输入电压信号转换为一个多位的数字信号。由于数字信号本身不具有实际意义,仅仅表示一个相对大小。故任何一个模数转换器都需要一个参考模拟量作为转换的标准。比较常见的参考标准为最大的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小

芯片主要性能:

1)8位分辨率A/D转换器

2)差分参考输入电压

3)最大转换时间17us

2.实验原理

注意: TLC549是 TI公司生产的一种低价位、高性能的8位 A/D转换器,它以8位开关电容逐次逼近的方法实现 A/D转换,其转换速度小于 17us,最大转换速率为 40000HZ,4MHZ典型内部系统时钟,电源为 3V至 6V。TLC549的使用只有输入/输出时钟( I/O时钟)以及芯片选择( CS)输入的数据控制。 TLC549的I/O时钟被指定至1.1MHz。

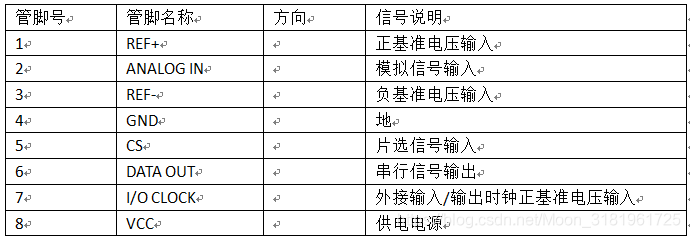

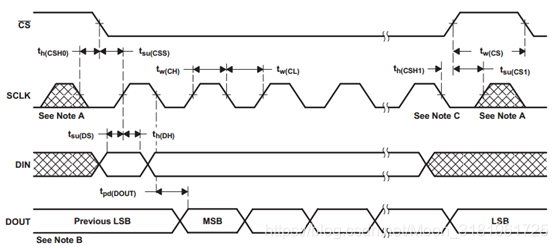

时序图

当 CS 为高时,数据输出(DATA OUT)端处于高阻状态,此时 I/O CLOCK不起作用。这种 CS 控制作用允许在同时使用多片 TLC549 时,共用 I/O CLOCK,以减少多路 (片)A/D 并用时的 I/O 控制端口。

通常的控制时序为:

- 将 CS 置低。内部电路在测得 CS 下降沿后,再等待两个内部时钟上升沿和 一个下降沿后,然后确认这一变化,最后自动将前一次转换结果的最高位(D7)位输出到 DATA OUT 端上。

- 前四个 I/O CLOCK 周期的下降沿依次移出第 2、 3、 4 和第 5 个位(D6、D5、D4、 D3),片上采样保持电路在第 4 个 I/O CLOCK 下降沿开始采样模拟输入。

- 接下来的 3 个 I/O CLOCK 周期的下降沿移出第 6、 7、 8(D2、 D1、 D0) 个转换位。

- 最后,片上采样保持电路在第 8 个 I/O CLOCK 周期的下降沿将移出第 6、7、 8(D2、 D1、 D0)个转换位。保持功能将持续 4 个内部时钟周期,然后开始进行32 个内部时钟周期的 A/D 转换。第 8 个 I/O CLOCK 后, CS 必须为高,或将 I/O CLOCK 保持低电平,这种状态需要维持 36 个内部系统时钟周期以等待保持和转换工作的完成。如果 CS 为低时 I/O CLOCK 上出现一个有效干扰脉冲,则微处理器/控制器将不器件的 I/O 时序失去同步;若 CS 为高时出现一次有效低电平,则将使引脚重新初始化, 从而脱离原转换过程。在 36 个内部系统时钟周期结束之前,实施步骤 (1)-(4),可重新启动一次新的 A/D 转换,不此同时,正在进行的转换终止,此时的输出是前一次的转换结果而不是正在进行的转换结果。若要在特定的时刻采样模拟信号,应使第 8个 I/O CLOCK 时钟的下降沿不该时刻对应,因为芯片虽在第 4 个 I/O CLOCK 时钟下降沿开始采样,却在第 8 个 I/O CLOCK 的下降沿开始保存。

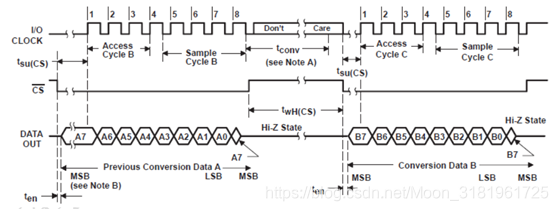

原理图

3. 实验目的

该模块可以工作在两种模式。

1)测试模式

用跳线帽将J33的AIN_TEST和ADC_IN两个脚短接。转动模拟量控制器(U20),通过 TLC549 芯片的 AD 转换,将相应的模拟量转化为数字量,并将数字量显示在LCD1602上。

2)工作模式

J33不用跳线帽短接。外部模拟信号接入BNC(ADC_IN),通过 TLC549 芯片的 AD 转换,将相应的模拟量转化为数字量,并将数字量显示在LCD1602上。

4. 实验结果

调节U20,可观察到LCD1602上的数字在不断变化

三. 数模转换(DA转换)

1. 知识背景

DA芯片采用的是TLC5615,该芯片的功能为将数字信号转换成模块。

芯片主要性能:

1)10bitD/A转换器

2)电压输出范围为2倍参考电压

3)数据更新速度最高为1.21Mhz

2. 实验原理

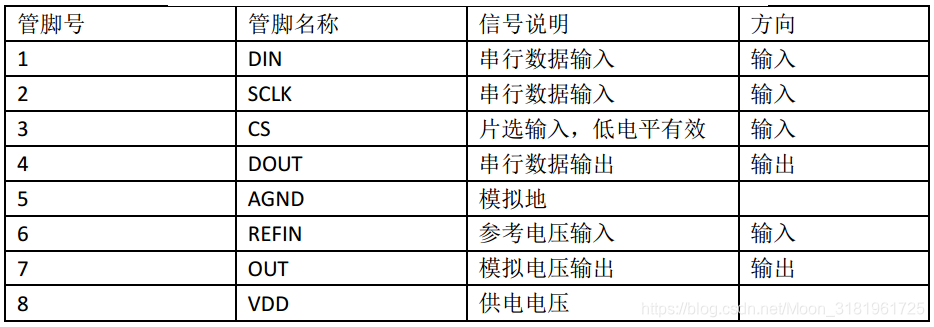

时序图

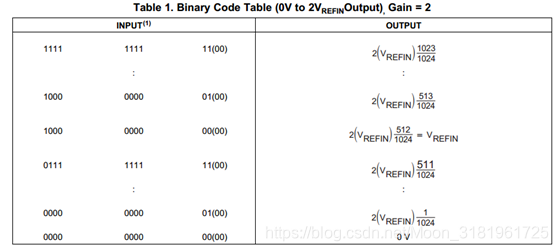

模拟输出公式及对应关系

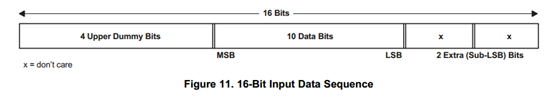

数字信号格式

根据数据手册,我们可以知道DA的位宽是10bit,参考电压(Vrefin)是2.048V。数据手册第8页根据公式:Vout=2Vrefindata/1024。当data=1024时最大输出是4.096V,当data=0时最小输出是0V。由于原理图中,我们给的参考电压是3.3V,如果我们要输出最大电压,data=Vout*1024/2/Vrefin,Vout=4.096,Vrefin=3.3,那么data=636。

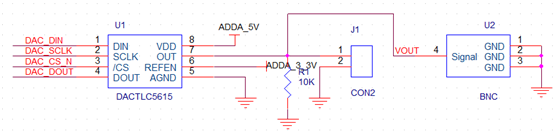

原理图

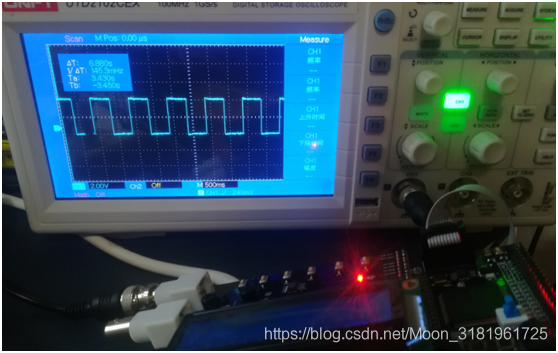

3. 实验目的

输出频率为1HZ占空比为50%,幅值为4V的方波信号。由于模拟输出管脚接了一个LED指示灯,可以观察到LED闪灯现象,用示波器可观测到方波信号

4. 实验现象

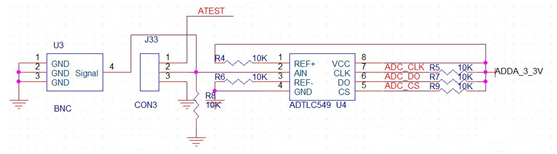

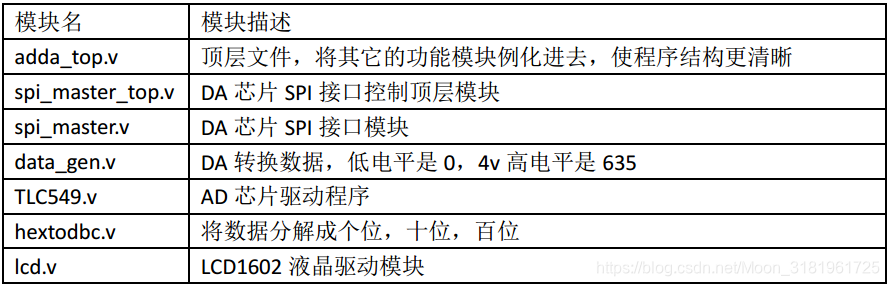

四. 代码结构分析

该例程包括三个文件夹

- Project 工程文件夹,里面有QuartusII工程文件

- Source 源码文件夹,包括所有.v文件

- Sim 仿真文件夹,里面包含仿真测试文件以及批处理文件

源码分析

本文详细介绍了使用TLC549进行模数转换和TLC5615进行数模转换的实验,涵盖硬件资源、转换原理、实验操作及代码结构分析。通过实验证明了AD和DA转换的有效性。

本文详细介绍了使用TLC549进行模数转换和TLC5615进行数模转换的实验,涵盖硬件资源、转换原理、实验操作及代码结构分析。通过实验证明了AD和DA转换的有效性。

1306

1306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?