2.2 基本指令格式

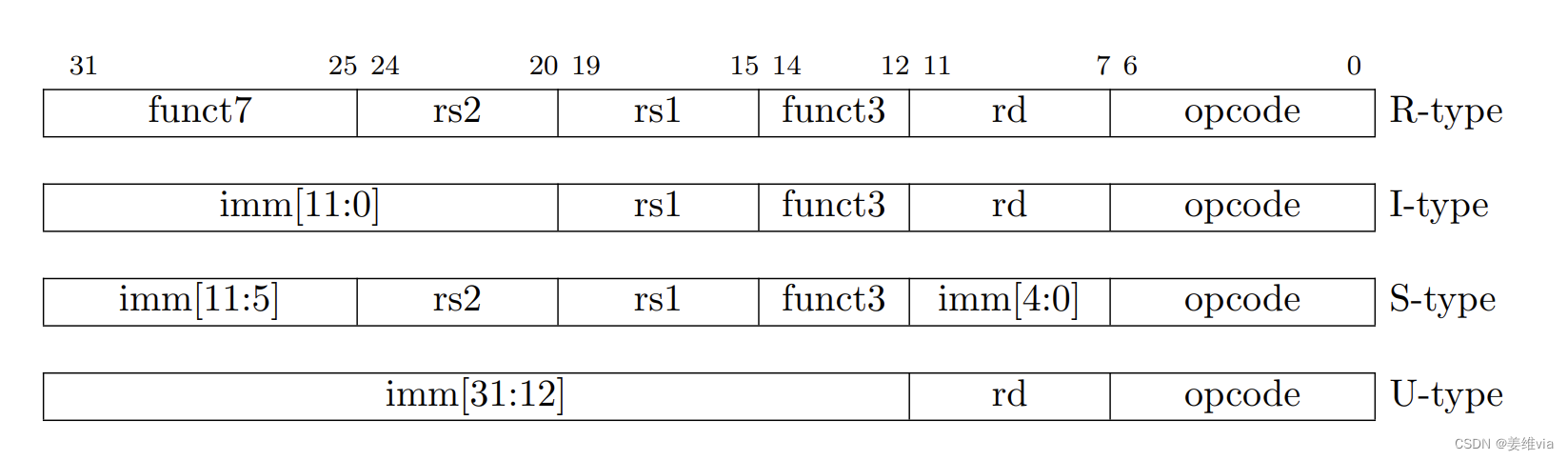

在基本ISA中,有四种核心指令格式(R/I/S/U),如下图:

在所有格式中,RISC-V ISA将源寄存器(rs1和rs2)和目标寄存器(rd)固定在同样的位置,以简化指令译码。在指令中,立即数被打包,朝着最左边可用位的方向,并且是分配好的,以减少硬件复杂度。特别地,所有立即数的符号位总是在指令的第31位,以加速符号扩展电路。

事实上,绝大多数立即数要么很小,要么需要所有的 XLEN 位。我们选择了一种非对称的立即数切分方法(在常规的指令中的低 12 位,加上一条特殊的 load 立即数指令提供高 20 位)来增加常规指令的可用操作码空间。(加载一个 32 位立即数,需要两步:load 指令提供该立即数的高 20 位[31:12],常规指令提供该立即数的低12 位[11:0],最后拼接成一个 32 位立即数)。另外,这些立即数都是符号扩展的(有符号数)。我们并没有观察到使用零扩展(无符号数)带来的好处,并且我们想把 ISA 做得尽可能简单。

2.3 立即数编码变种

基于立即数处理,还有额外两种指令格式变种(B/J),如下图所示。

每个立即数字段被所生成的立即数值中的位的位置(imm[x])标签,而不是在指令的立即数字段中的通常位的位置。上图给出了每一种基本指令格式生成的立即数,并被标签,以显示对应指令位(inst[y])生成了立即数值中的对应位。

RISC-V 指令生成的立即数。用指令的位标注了用于构成立即数的字段。符号扩展总是使用 inst[31]。

2.4 整数计算指令

整数寄存器-立即数指令

ADDI:将符号扩展的12位立即数加到寄存器rs1上。算术溢出被忽略,将运算结果的低XLEN位写进rd中。ADDI rd,rs1,0用于实现MV rd,rs1汇编语言伪指令。

SLTI(set less than immediate)将数值1放到寄存器rd中,如果寄存器rs1小于符号扩展的立即数(比较时,两者都作为有符号数),否则将0写入rd。

SLTIU与之相似,但是将两者作为无符号数进行比较(也就是说,立即数被首先符号扩展为XLEN位,然后被作为一个无符号数)。注意,SLTIU rd,rs1,1将设置rd为1,如果rs1等于0,否则将rd设置为0(汇编语言伪指令SEQZ rd,rs)。

ANDI、ORI、XORI是逻辑操作,在寄存器rs1和符号扩展的12位立即数上执行按位与;或;异或操作,并把结果写入rd。注意,XORI rd,rs1,-1在rs1上执行一个按位取反操作(汇编语言伪指令NOT rd,rs)。

被移位常数次,被编码为I类格式的特例。被移位的操作数放在rs1中,移位的次数被编码到I立即数字段的低5位。右移类型被编码到I立即数的一位高位。SLLI是逻辑左移(0被移入低位);SRLI是逻辑右移(0被移入高位);SRAI是算术右移(原来的符号位被复制到空出的 高位中)。

逻辑右移与算术右移的区别:逻辑右移高位补0,算术右移高位补符号位(正数补0;负数补1)

LUI(load upper immediate)用于构建32位常数,并使用U类格式。LUI将U立即数放到目标寄存器rd的高20位,将rd的低12位填0。

AUIPC(add upper immediate to pc)用于构建pc相对地址,并使用U类格式。AUIPC从20位U立即数构建一个32位偏移量,将其低12位填0,然后将这个偏移量加到pc上,最后将结果写入寄存器rd。

整数寄存器-寄存器操作

RV32I定义了几种算术R类操作。所有操作都是读取rs1和rs2寄存器作为源操作数,并把结果写入到寄存器rd中。funct7和funct3字段选择了操作的类型。

ADD和SUB分别执行加法和减法。溢出被忽略,并且结果的低XLEN位被写入目标寄存器 rd。SLT和SLTU分别执行符号数和无符号数的比较,如果rs1<rs2,则将1写入rd,否则将0写入rd。(汇编伪指令:SNEZ rd,rs,被译成SLTU rd,x0,rs,如果rs不为0,则把1写入rd,否则把0写入rd)。

AND、OR、XOR执行按位逻辑操作,类似于ANDI、ORI、XORI,对应源操作数换成rs1和rs2。

SLL、SRL、SRA分别执行逻辑左移,逻辑右移,算术右移操作,类似于SLLI、SRLI、SRAI,对应源操作数换成rs1和rs2。

NOP 指令

NOP指令并不改变任何用户可见的状态,除了使得pc向前推进。NOP被编码为ADDI x0,x0,0。

2.5 控制转移指令

无条件跳转

JAL(jump and link),指令使用了UJ类格式,此处J立即数编码了一个2的倍数的有符号偏移量。这个偏移量被符号扩展,加到pc上,形成跳转目标地址,跳转范围因此达到±1MB。 JAL将跳转指令后面指令的地址(pc+4)保存到寄存器rd中。标准软件调用约定使用寄存器x1来作为返回地址寄存器。

注:由上图可知,立即数没有[0]位,即2的倍数;至于跳转范围,由于偏移量offset为21位,除去最高位符号位,剩下20位,即2^20=1M,故跳转范围为±1MB。

普通的无条件跳转指令(汇编语言伪指令J)被编码为rd=x0的JAL指令。(注:x0是只读寄存器,无法写入,因此只跳转,不保存pc+4到rd中)。

JALR(jump and link register)使用I类编码。通过将12位有符号I类立即数加上rs1,然后将结果的最低位设置为0,作为目标地址。跳转指令后面指令的地址(pc+4) 保存到寄存器rd中。如果不需要结果,则可以把x0作为目标寄存器。

JAL指令和JALR指令会产生一个非对齐指令取指异常(address_misaligned),如果目标地址没有对齐到4字节边界。

514

514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?