先说概念

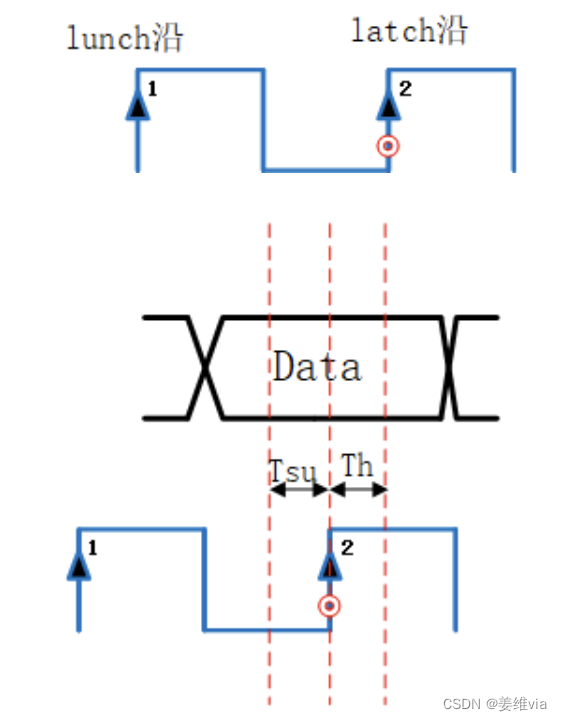

Tsetup建立时间:时钟有效边沿之前输入数据有效且稳定不变的时间

Thold保持时间:时间有效边沿之后输入数据有效且稳定不变的时间

理想最优的建立时间和保持时间出现在数据中间采样的位置,如下所示,实质就是使触发器在采样沿得到稳定的数据,如果数据在时钟上升沿的建立保持时间内发生跳变,则会产生亚稳态输出,即输出值在短时间内处于不确定态,有可能是1,有可能是0,也可能什么都不是,处于中间态。

至于为什么不满足建立时间或者保持时间就会出现亚稳态,我们首先需要了解一下D触发器的结构,最常用的就是边沿触发的D触发器。

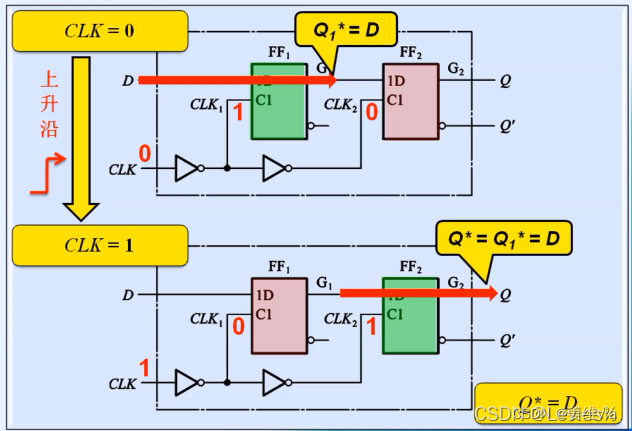

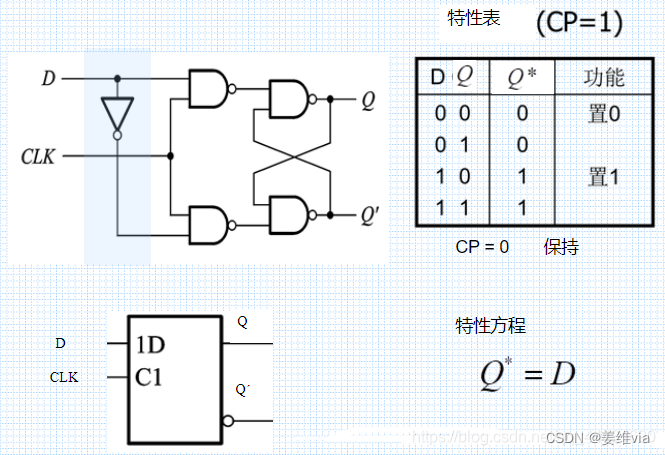

边沿触发的D触发器

边沿触发的D触发器由两个电平触发的D触发器组成:

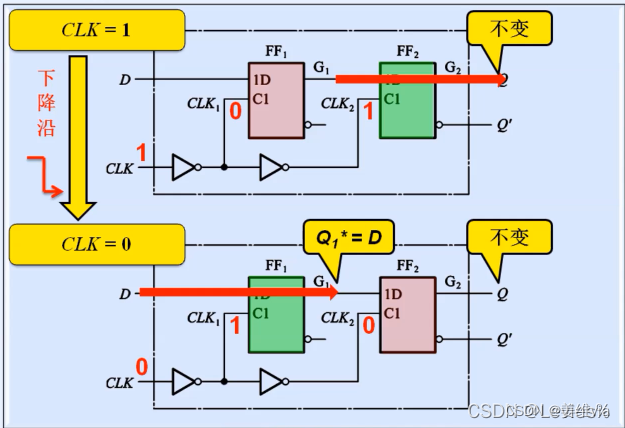

由于边沿的变化导致两个触发器并不能同时导通,因此实现了在上升沿/下降沿数据导通,那么其实还是没有明白为什么输入数据需要在边沿之前或者之后保持稳定一段时间,别急接着看。

我们已经知道了边沿D触发器的结构是由电平触发器构成,那么电平触发器是由什么组成的呢

电平触发的D触发器

我们可以看到输入D会经过一个反相器进入输入端,反相器是由两个mos管组成,具有一定的噪声容限,超出这个容限我们就认为其为亚稳态,所以需要保持输入的信号有效且稳定,但是为什么要需要有效且稳定一段时间(即建立时间和保持时间)因为从对于一个触发器来说,从输入到输出都是要经过一段的逻辑门,这中间必然会存在一定的延时,所以在输出没有稳定之前,我们需要保持输入的相对稳定,否则还是会出现亚稳态。

综上所述,从触发器角度来看,建立时间是为了保证边沿触发器的第一段电平触发器能稳定输出,保持时间则是保证第二段电平触发器能够稳定输出,只有同时都满足建立时间和保持时间,才能保证不出现亚稳态。

参考链接

欢迎大家留言批评指正交流,互相学习

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?