简介

PCI Express 是一种高性能、通用的 I/O 互连技术,适用于各类未来计算与通信平台。它保留了 PCI 局部总线的核心特性,如使用模型、加载 - 存储架构及软件接口,同时以高度可扩展的全串行接口取代了 PCI 局部总线的并行总线实现方式。PCI Express 借助点对点互连、基于交换机的技术及分组协议等方面的进步,实现了更高水平的性能与功能。该技术支持的高级特性包括电源管理、服务质量(QoS)、热插拔支持、数据完整性及错误处理等。

I/O 需求

这种不断发展的 I/O 互连技术的高层需求如下:

-

支持多市场领域及新兴应用:

-

为桌面设备、移动设备、工作站、服务器、通信平台及嵌入式设备提供统一的 I/O 架构

-

能够提供低成本、高容量的解决方案:

-

系统级成本达到或低于 PCI 的成本结构

-

支持多种平台互连用途:

-

芯片到芯片、通过连接器或线缆实现的板到板连接

-

多种机械形态规格:

-

[M.2]、[CEM](卡机电规格)、[U.2]、[OCuLink]

-

与 PCI 兼容的软件模型:

-

无需修改 PCI 系统配置软件,即可枚举和配置 PCI Express 硬件

-

无需修改现有操作系统,即可启动运行

-

无需修改现有 I/O 设备驱动程序,即可支持其运行

-

采用 PCI 配置范式,能够配置 / 启用 PCI Express 的新功能

-

性能:

-

低开销、低延迟通信,以最大化应用有效载荷带宽和链路效率

-

高每引脚带宽,以减少每个设备及连接器接口的引脚数量

-

通过聚合通道和信号频率实现可扩展性能

-

高级特性:

-

支持不同数据类型和排序规则

-

电源管理与功耗控制

-

能够识别特定功能的设备的电源管理能力

-

能够将设备或功能转换至特定电源状态

-

能够接收设备或功能当前电源状态的通知

-

能够在主电源关闭状态下生成唤醒请求

-

能够对设备上电进行时序控制,以在功耗预算中实现平稳的平台策略

-

能够支持差异化服务,即不同的(服务质量,QoS)

-

够为每个 QoS 数据流分配专用链路资源,以提高结构效率,并在面临队头阻塞时提升有效的应用级性能

-

能够在每个组件内配置结构 QoS 仲裁策略

-

能够为每个数据包标记端到端 QoS

-

能够创建端到端等时(基于时间、注入速率控制)解决方案

-

热插拔支持

-

能够支持现有的 PCI 热插拔解决方案

-

能够支持原生热插拔解决方案(无需边带信号)

-

能够支持异步移除

-

能够为所有形态规格提供统一的软件模型

-

数据完整性

-

能够为所有类型的事务包和数据链路包提供链路级数据完整性支持

-

能够为高可用性解决方案提供端到端数据完整性支持

-

错误处理

-

能够支持与 PCI 兼容的错误处理

-

能够支持高级错误报告和处理,以改进故障隔离和恢复解决方案

-

工艺技术独立性

-

能够支持发送器和接收器采用不同的直流共模电压

-

易于测试

-

能够通过与测试设备的简单连接进行电气合规性测试

PCIE链路

-

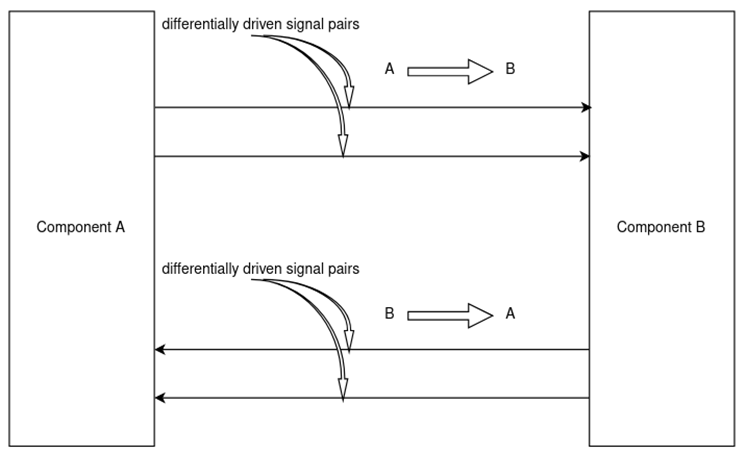

组件之间使用双单工通信。

-

链路由两对低压差分信号组成,一对是发送信号,一对是接收信号。

图1-1 传输方式以及差分信号对

通信方式对比

|

术语(中文 / 英文) |

核心传输特性 |

典型应用 |

效率对比 |

|---|---|---|---|

|

全双工通信通道 |

同一时刻双向同步传输 |

USB 3.0+、千兆以太网 |

最高(无等待时间) |

|

双单工通信通道 |

双向传输,但需分时进行(同一时刻仅单向) |

早期 PCIe 链路、部分串行总线 |

中等(存在微小分时延迟) |

|

半双工通信通道 |

双向传输,但需手动 / 自动切换方向(收发互斥) |

早期以太网(10Mbps)、对讲机 |

最低(切换存在等待延迟) |

差分信号介绍

低压差分信号(Low-Voltage Differential Signaling,简称LVDS)是一种用于高速、低功耗、长距离数据传输的物理层信号技术,核心特点是通过 “差分电压” 传输数据,而非传统的 “单端电压”(如 TTL 信号),广泛应用于工业控制、汽车电子、显示面板、高速通信等场景(例如 LCD 屏幕的 LVDS 接口、工业相机的图像传输)

LVDS 通过 “两根紧密耦合的差分线(通常标记为 P 正线和 N 负线)” 传输:

-

数据表示:不依赖地线参考,而是通过 “两根线的电压差” 判断逻辑 —— 当 P 线电压比 N 线高 200mV±100mV 时,表示 “1”;当 N 线电压比 P 线高 200mV±100mV 时,表示 “0”(标准 LVDS 的差分电压摆幅为 350mV max,典型值 250mV);

-

供电电压:“低压” 体现在供电端 —— 通常为 3.3V 或 2.5V(早期为 5V,现已淘汰),部分低功耗版本支持 1.8V,大幅降低芯片功耗。

PCIE链路属性

-

基础链路 ——链路由两条单向差分链路构成,具体实现为一对发送信号和一对接收信号。通过编码方案嵌入数据时钟,以实现极高的数据速率。后续会介绍具体的实现方案。

-

信号传输方式 ——实际有效数据速率取决于调制方式、编码方式与数据速率的组合。这部分后续会有更为详尽的介绍

|

Data Rate |

Modulation |

Encoding |

Effective Data Rate |

|---|---|---|---|

|

2.5 GT/s |

NRZ |

8b/10b |

2 Gbit/s |

|

5.0 GT/s |

NRZ |

8b/10b |

4 Gbit/s |

|

8.0 GT/s |

NRZ |

128b/130b |

~8 Gbit/s |

|

16.0 GT/s |

NRZ |

128b/130b |

~16 Gbit/s |

|

32.0 GT/s |

NRZ |

128b/130b |

~32 Gbit/s |

|

64.0 GT/s |

PMA4 |

1b/1b |

64 Gbit/s |

-

通道(Lanes)—— 每条链路必须至少支持 1 条通道,每条通道包含一组差分信号对(一对用于发送,一对用于接收)。为扩展带宽,链路可聚合多条通道,以 xN 表示(其中 N 为支持的链路宽度)。例如,工作在 2.5 GT/s 数据速率下的 x8 链路,每个方向的原始聚合带宽为 20 Gbps(千兆比特每秒)。

-

初始化 —— 硬件初始化阶段,PCI Express 链路的两端设备会协商通道宽度和工作频率,完成链路建立。此过程无需固件或操作系统软件参与。后续会介绍这部分如何实现。

-

对称性 —— 每条链路在两个方向上必须支持对称的通道数量,例如,x16 链路表示每个方向均有 16 对差分信号。

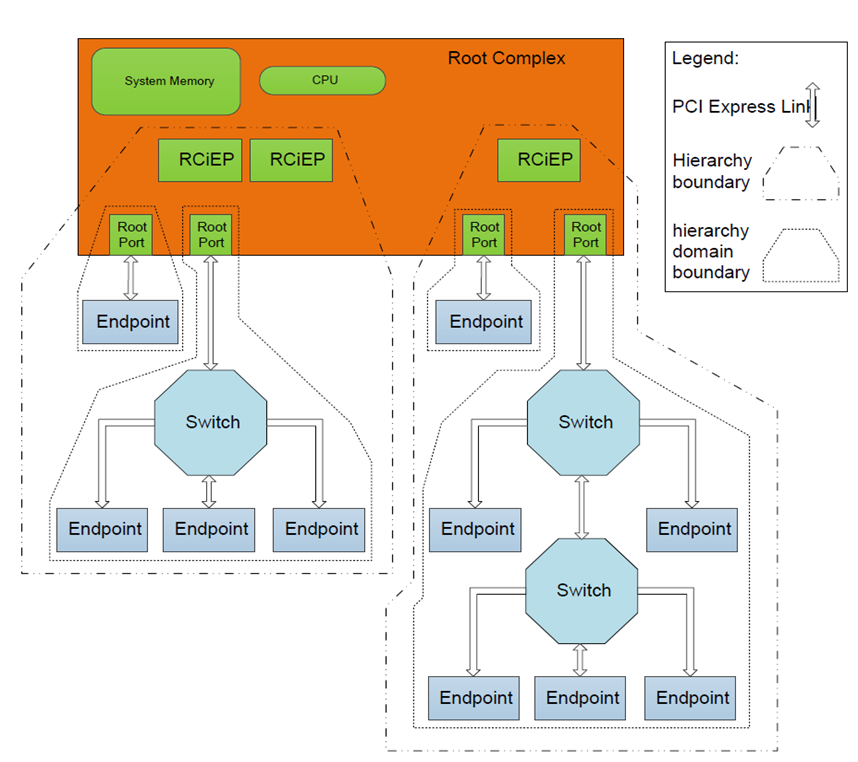

PCIE拓扑图

PCIE拓扑图里面会涉及到根复合体(root complex),端点(endpoint)和交换机(switch)。PCIE里面会对根复合体,端点和交换机有一些具体的要求和各部分负责的内容。这部分后续也会有介绍,此处只作为一个简单的介绍。不会具体去列举出来所有的内容。

图 1-2 Example PCI Express Topology

PCIE软硬件模型的发现、配置和操作

PCI/PCIe 硬件 / 软件模型包含实现 “发现、配置及使用功能(Function)” 所需的架构组件,且无需掌握该功能的专属信息。其核心要素包括:

-

配置模型:为系统软件提供发现系统中可用硬件功能(Function)的手段;

-

资源分配机制:用于为可寻址资源(如内存空间、中断)执行基础资源分配;

-

使能 / 禁用控制:控制功能(Function)是否响应接收到的请求(Request),以及是否发起请求(Request);

-

明确的排序与流量控制模型:支持硬件 / 软件接口的一致性与稳健性实现。

PCI Express 配置模型支持两种机制:

-

PCI 兼容配置机制:该机制支持与 “识别传统 PCI(Conventional PCI)的操作系统” 及其对应的总线枚举、配置软件实现 100% 二进制兼容;

-

PCI Express 增强型配置机制:提供该机制的目的是增大可用配置空间(Configuration Space)的容量,并优化访问机制。

每条 PCI Express 链路均通过虚拟 PCI 到 PCI 桥接器(virtual PCI-to-PCI Bridge)结构进行映射,且关联一条逻辑总线(Logical Bus)。该虚拟 PCI 到 PCI 桥接器结构可属于以下组件:PCI Express 根复合体端口(Root Complex Port)、交换机上行端口(Switch Upstream Port)或交换机下行端口(Switch Downstream Port)。根端口(Root Port)是一种虚拟 PCI 到 PCI 桥接器结构,可从 PCI Express 根复合体(Root Complex)发起一个 PCI Express 层次结构域(hierarchy domain)。设备会被映射到配置空间(Configuration Space)中,且每个设备仅响应特定的设备编号(Device Number)。

PCIE层级介绍

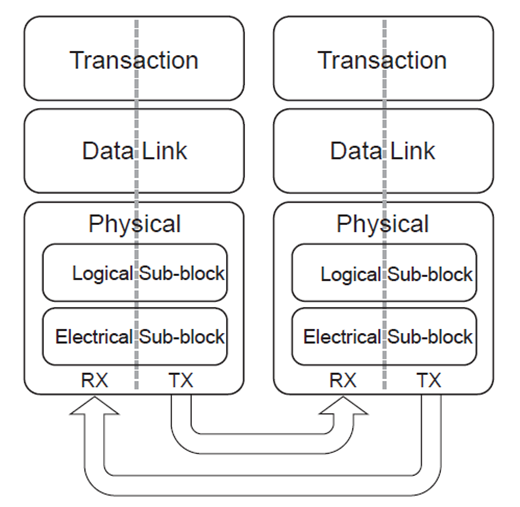

本文档从三个独立的逻辑层角度定义 PCI Express 架构,分别是事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer)。这里面涉及到很多的技术后续会在文档中逐一介绍。

层级图

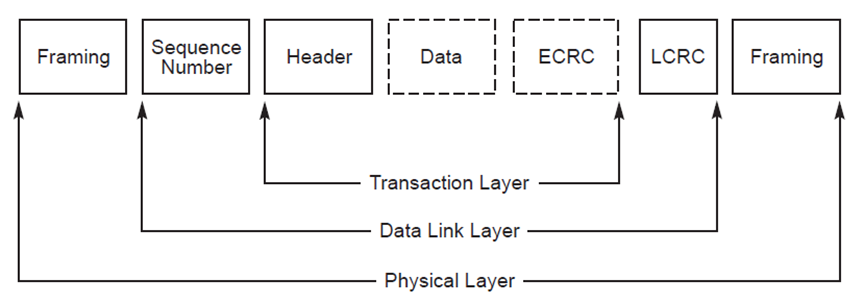

PCI Express 采用数据包(packet)在组件间传递信息。数据包在事务层(Transaction Layer)和数据链路层(Data Link Layer)中构建,用于将信息从发送端组件传输到接收端组件。当发送的数据包流经其他层级时,会被添加该层级处理数据包所需的额外信息。在接收端则进行反向处理:数据包从物理层(Physical Layer)格式转换为数据链路层格式,最终(对于事务层数据包(TLPs)而言)转换为可被接收端设备的事务层处理的格式。事务级数据包信息在各层级间的概念性流转过程,如下图所示。

数据包传输

传输层

架构的上层是事务层(Transaction Layer)。事务层的主要职责是事务层数据包(TLPs)的组装与拆解。TLPs 用于传递事务(如读写操作)以及特定类型的事件。事务层还负责管理基于信用(credit-based)的 TLP 流量控制。

所有需要响应包的请求包均通过拆分事务(Split Transaction)实现。每个数据包都有唯一标识符,确保响应包能被定向到正确的发起方。数据包格式支持多种寻址方式,具体取决于事务类型(内存(Memory)、I/O、配置(Configuration)和消息(Message))。数据包还可包含一些属性,如非窥探(No Snoop)、松弛排序(Relaxed Ordering)和基于 ID 的排序(ID-Based Ordering, IDO)。

事务层支持四个地址空间:包括 PCI 的三个传统地址空间(内存、I/O 和配置空间),并新增了消息空间(Message Space)。本规范通过消息空间将所有原有的边带信号(如中断、电源管理请求等)转换为带内消息事务(in-band Message transactions)。可以将 PCI Express 消息事务理解为 “虚拟线路(virtual wires)”,因为它们的作用是消除平台实现中目前使用的大量边带信号。

事务层(Transaction Layer)在生成和接收事务层数据包(TLPs)的过程中,会与链路(Link)另一端的对等事务层交换流量控制(Flow Control)信息。它还负责支持由软件和硬件发起的电源管理(power management)。

初始化与配置功能要求事务层:

-

存储由处理器或管理设备生成的链路配置信息;

-

存储由物理层(Physical Layer)硬件通过宽度和工作频率协商生成的链路能力信息。

事务层的数据包生成与处理服务要求其:

-

根据设备核心(device core)的请求(Requests)生成 TLPs;

-

根据设备核心(device core)的请求(Requests)生成事务层数据包(TLPs);

-

将接收到的请求事务层数据包(Request TLPs)转换为设备核心(device core)可处理的请求(Requests)

-

将接收到的完成数据包(Completion Packets)转换为可交付给设备核心的有效载荷(payload)或状态信息;

-

检测不支持的 TLPs,并调用适当的机制进行处理;

-

若支持端到端数据完整性(end-to-end data integrity),则生成端到端数据完整性循环冗余校验(CRC),并相应地更新 TLP 头部。

流量控制服务:

-

事务层跟踪链路上 TLPs 的流量控制信用(Flow Control credits);

-

事务信用状态通过数据链路层(Data Link Layer)的传输服务定期发送至远端事务层;

-

远端流量控制信息用于调节 TLP 的传输(防止发送过量导致缓冲区溢出)。

排序规则:

-

兼容 PCI/PCI-X 的生产者 / 消费者(producer/consumer)排序模型;

-

扩展支持松弛排序(Relaxed Ordering);

-

扩展支持基于 ID 的排序(ID-Based Ordering)。

电源管理服务(Power management services)

-

软件控制的电源管理:通过系统软件(system software)规定的机制实现。

-

硬件控制的自主电源管理:在设备处于全功率开启状态(full-on power states)时,将功耗降至最低。

虚拟通道与流量类别(Virtual Channels and Traffic Class):

-

虚拟通道(Virtual Channel)机制与流量类别(Traffic Class)标识相结合,旨在为特定类型的应用提供差异化服务(differentiated services)和服务质量(QoS,Quality of Service)支持。

-

虚拟通道(Virtual Channels):虚拟通道提供了一种在链路(Link)的特定公共物理资源上支持多个独立逻辑数据流的方式。从概念上讲,这一机制是将不同的数据流复用到同一条物理链路上。

-

流量类别(Traffic Class):流量类别是事务层数据包(Transaction Layer Packet)的一个标签,在整个架构(fabric)中端到端传输时保持原样(不被修改)。在架构内的每个服务点(如交换机(Switch)),流量类别标签用于应用相应的服务策略。每个流量类别标签定义一个唯一的排序域(ordering domain)—— 对于包含不同流量类别标签的数据包,不提供排序保证。

数据链路层

架构栈中的中间层是数据链路层(Data Link Layer),它充当事务层(Transaction Layer)与物理层(Physical Layer)之间的中间环节。数据链路层的主要职责包括链路管理(Link management)和数据完整性保障,具体涵盖错误检测与错误纠正。

数据链路层的发送端会接收由事务层组装完成的事务层数据包(TLPs),计算并添加数据保护码(data protection code)与 TLP 序列号(sequence number),随后将其提交至物理层,以通过链路(Link)传输。数据链路层的接收端负责校验所接收 TLP 的完整性,并将校验通过的 TLP 提交至事务层进行后续处理。若检测到 TLP 错误,该层需请求重新传输 TLP,直至信息被正确接收,或判定链路已失效。

数据链路层还会生成并消费用于链路管理功能的数据包。为将此类数据包与事务层使用的数据包(TLP)区分开,对于在数据链路层生成并消费的数据包,将使用术语 “数据链路层数据包(DLLP,Data Link Layer Packet)” 进行指代。

数据链路层(Data Link Layer)负责与链路(Link)另一端的对等数据链路层实现信息的可靠交换。

初始化与电源管理服务(Initialization and power management services):

-

接收来自事务层(Transaction Layer)的电源状态请求(power state Requests),并将其传递给物理层(Physical Layer);

-

向事务层传递链路的活跃(active)、复位(reset)、断开(disconnected)及电源管理(power managed)状态。

数据保护、错误检查与重传服务(Data protection, error checking, and retry services):

-

生成循环冗余校验码(CRC,Cyclic Redundancy Check),用于校验数据完整性;

-

存储已发送的事务层数据包(TLP),为数据链路层级别的重传(retry)提供支持;

-

执行错误检查,识别传输过程中出现的数据包错误;

-

发送事务层数据包的确认信息(acknowledgement)及重传消息(retry Messages);

-

提供错误指示(error indication),为错误报告与日志记录(error reporting and logging)提供依据。

物理层

物理层(Physical Layer)包含接口运行所需的全部电路,具体包括驱动电路与输入缓冲器、并串转换(parallel-to-serial conversion)与串并转换(serial-to-parallel conversion)电路、锁相环(PLL (s))以及阻抗匹配电路。此外,物理层还包含与接口初始化及维护相关的逻辑功能。物理层以 “依赖具体实现的格式” 与数据链路层(Data Link Layer)交换信息,其核心职责是将从数据链路层接收的信息转换为合适的串行格式,并以 “与链路另一端组件兼容的频率和位宽”,通过 PCI Express 链路(Link)进行传输。

PCI Express 架构预留了 “扩展接口(hooks)”,可通过速率升级与高级编码技术支持未来的性能提升。未来的速率标准、编码技术或传输介质变更,可能仅会影响物理层的定义(而无需修改事务层、数据链路层的核心架构)。

接口初始化、维护控制与状态跟踪(Interface initialization, maintenance control, and status tracking):

-

复位(Reset)/ 热插拔(Hot-Plug)的控制与状态管理;

-

互连(Interconnect)的电源管理;

-

链路宽度(Width)与通道映射(Lane mapping)的协商;

-

通道极性反转(Lane polarity inversion)的处理。

符号与特殊有序集生成(Symbol and special Ordered Set generation)

-

8 位 / 10 位(8b/10b)的编码与解码。

-

嵌入式时钟调谐与对齐(Embedded clock tuning and alignment):通过调整时钟信号参数,确保发送端与接收端的时钟同步,保障数据传输时序准确性。

块与特殊有序集生成(Block and special Ordered Set generation)

-

128 位 / 130 位(128b/130b)编码与解码:PCIe 4.0 及以上版本采用的高效编码技术,在 128 位数据基础上添加 2 位校验信息,兼顾传输效率与数据完整性;

-

1 位 / 1 位(1b/1b)编码与解码:简化的编码方式,适用于特定控制信号或低带宽场景,直接对单比特信号进行编码传输;

-

链路均衡(Link Equalization):通过调整信号放大增益、补偿链路损耗等方式,优化高速传输下的信号质量,减少信号衰减与失真。

符号传输与对齐(Symbol transmission and alignment)

-

发送电路(Transmission circuits):负责将编码后的符号转换为电信号,通过链路发送至接收端;

-

接收电路(Reception circuits):接收来自链路的电信号,将其转换为数字符号并传递至后续解码环节;

-

接收端弹性缓冲器(Elastic buffer at receiving side):缓解发送端与接收端的时钟偏差,避免因时序微小差异导致的数据丢失;

-

接收端多通道去偏移(Multi-Lane de-skew,适用于宽度>x1 的链路):当链路包含多条通道(如 x4、x8)时,消除不同通道间的信号传输延迟差异,确保多通道数据同步接收。

系统可测试性(DFT)支持特性(System Design For Testability (DFT) support features)

-

合规性测试图案(Compliance Pattern):用于验证设备是否符合 PCIe 规范要求的标准测试信号图案);

-

修改版合规性测试图案(Modified Compliance Pattern):在标准合规图案基础上调整的测试信号,适用于特定场景下的合规性验证;

-

抖动测量图案(Jitter Measurement Pattern):用于检测信号抖动(时序偏差)的专用测试图案,辅助评估链路传输稳定性;

-

帧错误注入(Flit Error Injection):主动向传输数据中注入错误,用于测试系统对错误的检测、处理与恢复能力,验证错误机制有效性。

事务层到数据链路层的接口(Transaction to Data Link interface)

该接口提供以下信息与机制:

-

待通过链路(Link)发送的字节级或多字节级数据;

本地事务层数据包(TLP)传输握手机制(Local TLP-transfer handshake mechanism):确保事务层发送的 TLP 能被数据链路层正确接收,避免数据丢失或重复;

事务层数据包边界信息(TLP boundary information):标识单个 TLP 的起始与结束位置,帮助数据链路层准确拆分连续传输的数据流,避免 TLP 拼接或截断。

-

链路所需的电源状态(Requested power state for the Link):由事务层发起对链路电源状态的请求(如进入低功耗状态),传递给数据链路层以协调后续状态切换。

数据链路层到事务层的接口(Data Link to Transaction interface)

该接口提供以下信息:

-

从 PCI Express 链路接收的字节级或多字节级数据;

-

接收字节对应的事务层数据包成帧信息(TLP framing information):标注接收数据属于哪个 TLP、在 TLP 中的位置等,帮助事务层正确重组 TLP;

-

链路的实际电源状态(Actual power state for the Link):反馈链路当前的真实电源状态(可能与事务层请求状态一致或存在差异),供事务层调整后续操作;

-

链路状态信息(Link status information):包括链路连接状态、错误状态、同步状态等,为事务层判断链路可用性、触发错误处理提供依据。

数据链路层到物理层的接口(Data Link to Physical interface)提供:

-

待通过链路(Link)发送的字节级或多字节级宽度的数据。

数据传输握手机制(Data transfer handshake mechanism):确保数据链路层发送的数据能被物理层正确接收的交互机制,避免传输冲突或数据丢失;

字节对应的事务层数据包(TLP)与数据链路层数据包(DLLP)边界信息:标识连续字节流中单个 TLP 或 DLLP 的起始与结束,帮助物理层准确区分不同类型的数据包并按规范处理。

-

链路所需的电源状态(Requested power state for the Link):数据链路层将从事务层接收的电源状态请求传递给物理层,以协调链路的电源状态切换。

物理层到数据链路层的接口(Physical to Data Link interface)提供:

-

从 PCI Express 链路接收的字节级或多字节级宽度的数据;

-

数据对应的 TLP 与 DLLP 成帧信息:标注接收数据属于哪个数据包(TLP 或 DLLP)、在数据包中的位置等,帮助数据链路层正确重组数据包;

-

物理层检测到的错误指示:包括信号完整性错误、编码错误等物理层级别的错误信息,供数据链路层触发相应的错误处理(如重传请求);

-

链路的实际电源状态:反馈链路当前的真实电源状态,确保数据链路层与物理层的状态同步;

-

连接状态信息:包括链路是否建立连接、通道同步状态等,为数据链路层判断链路可用性提供依据。

681

681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?