首先,确保自己的Quartus软件安装并破解完成,这里我要以自己的quartus II13.0为例做仿真。

1、创建VHDL文件并运行操作步骤

我是以自己的8位数码扫描显示电路为例,程序统调:实现8位七段数码管动态扫描显示电路设计,显示字型固定为自己的学号。

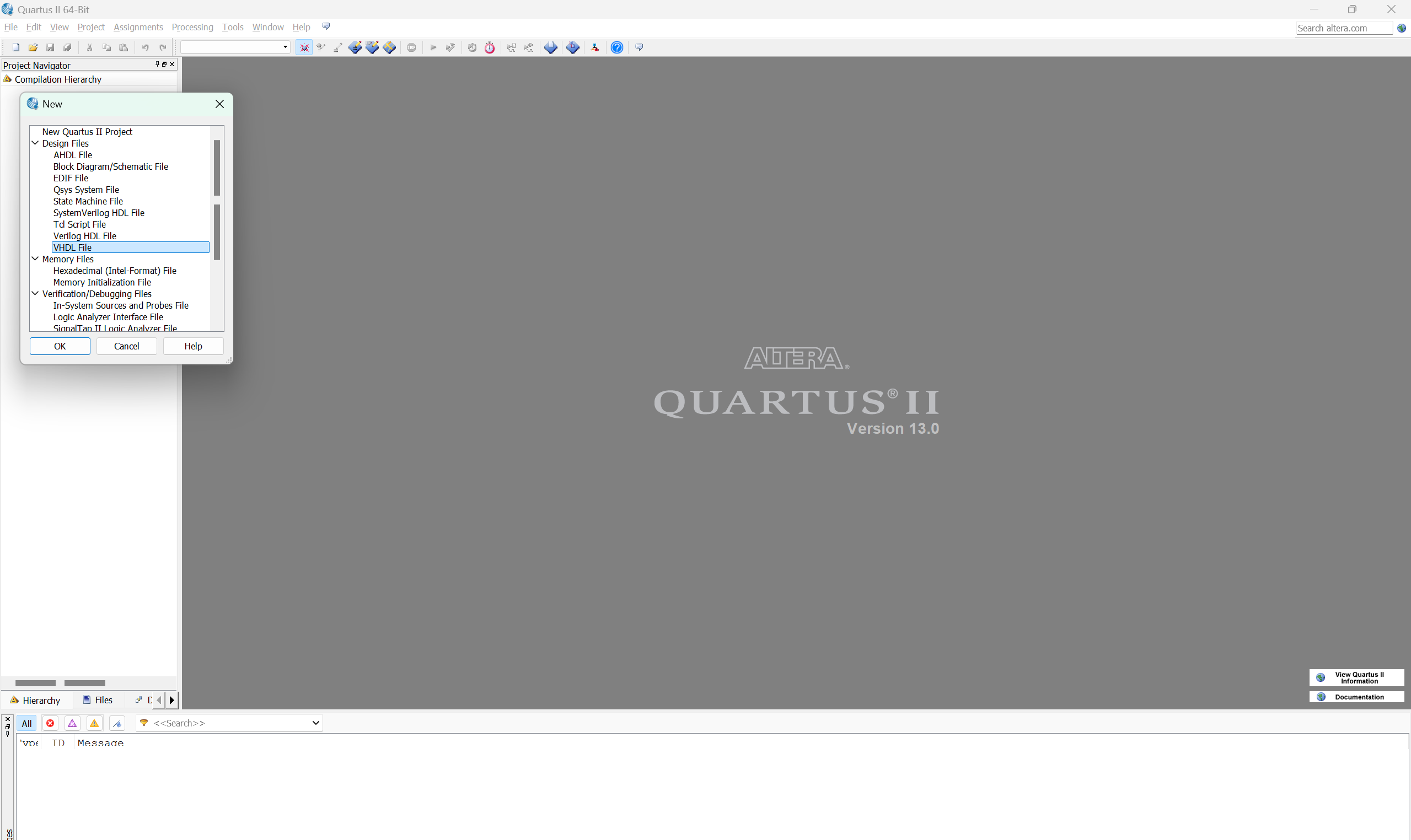

首先,以管理员身份运行quartus II13.0 --> File --> New --> VHDL File(新建项目)。

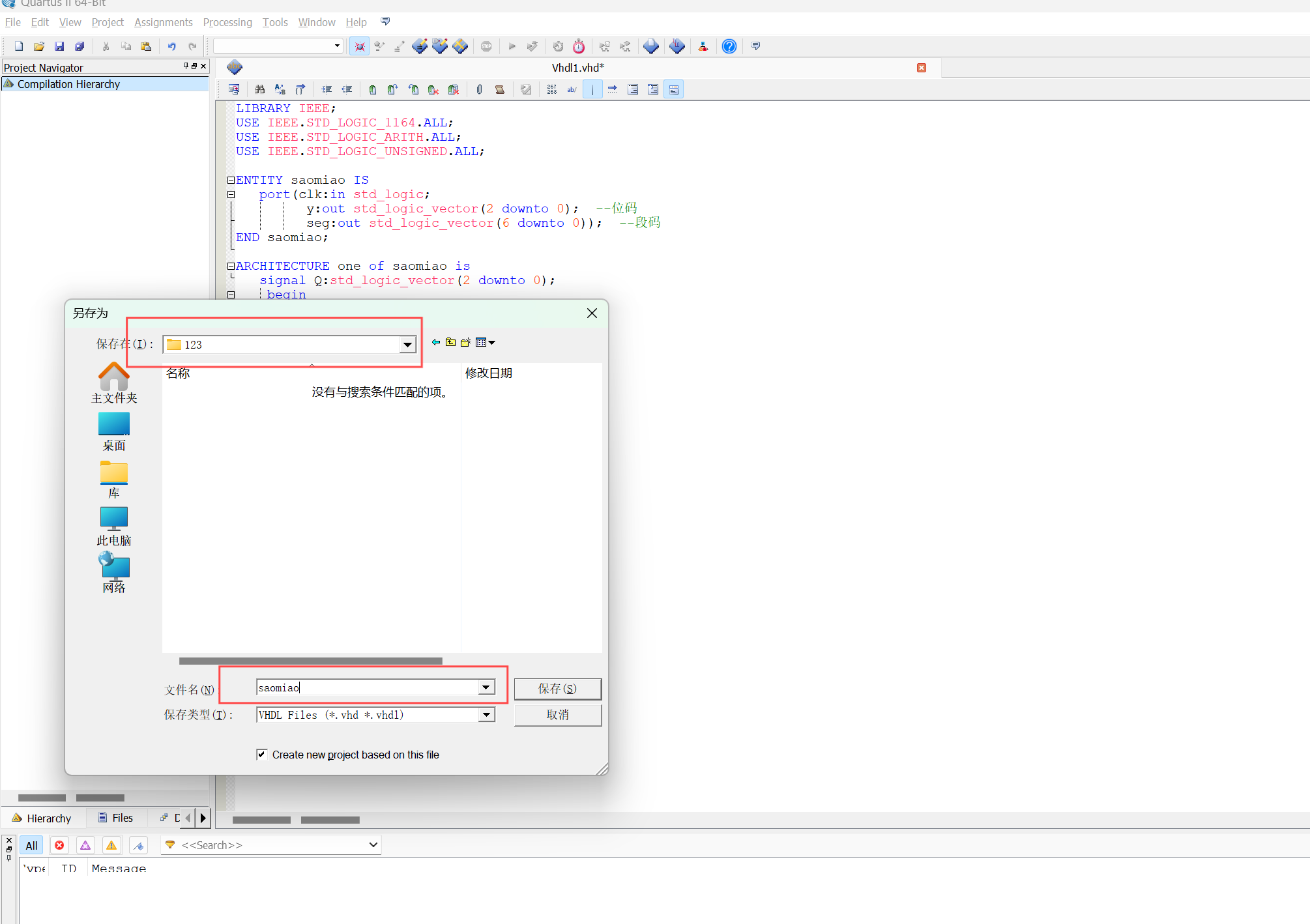

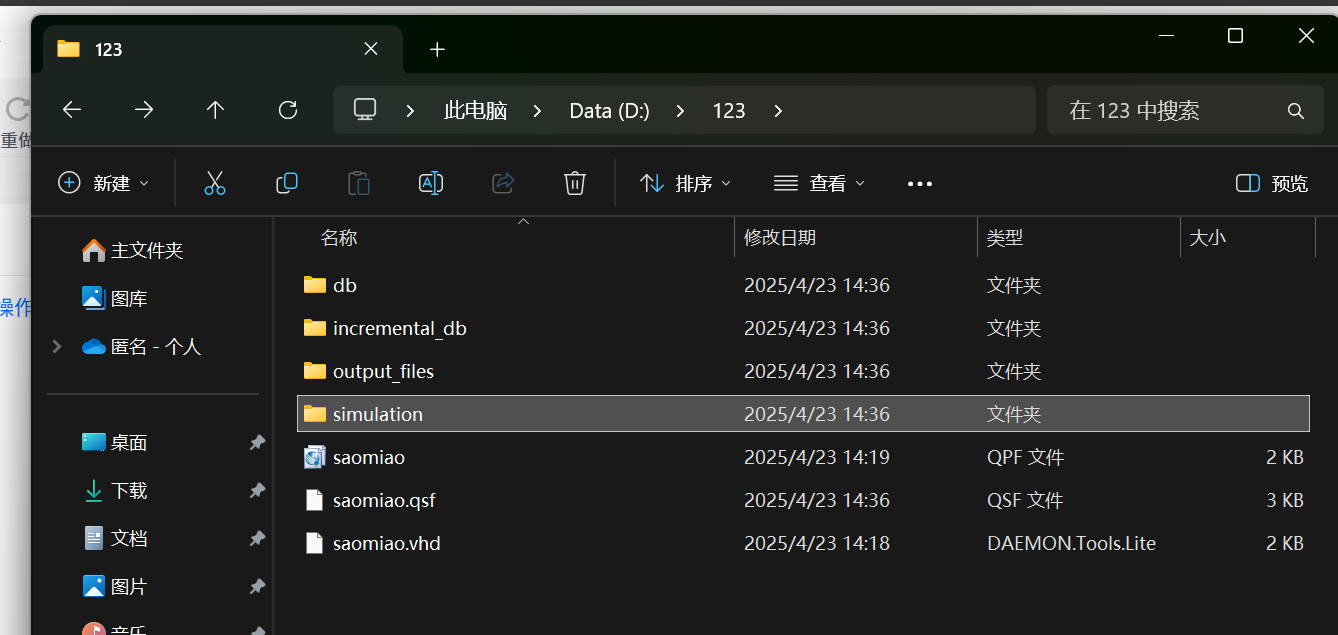

输入VHDL代码( 实现8位数码扫描显示电路),ctrl+s保存,会弹出如下窗口:可以新建一个空文件夹进行保存(我的是123/),文件名要与实体名一致。

点击保存,会弹出多个页面,一直Next即可,直到弹出如下页面,注意要根据自己程序的需求填写。 其中,Ayallable devices是需要安装的工具库,如果未安装,则不会出现选择项。

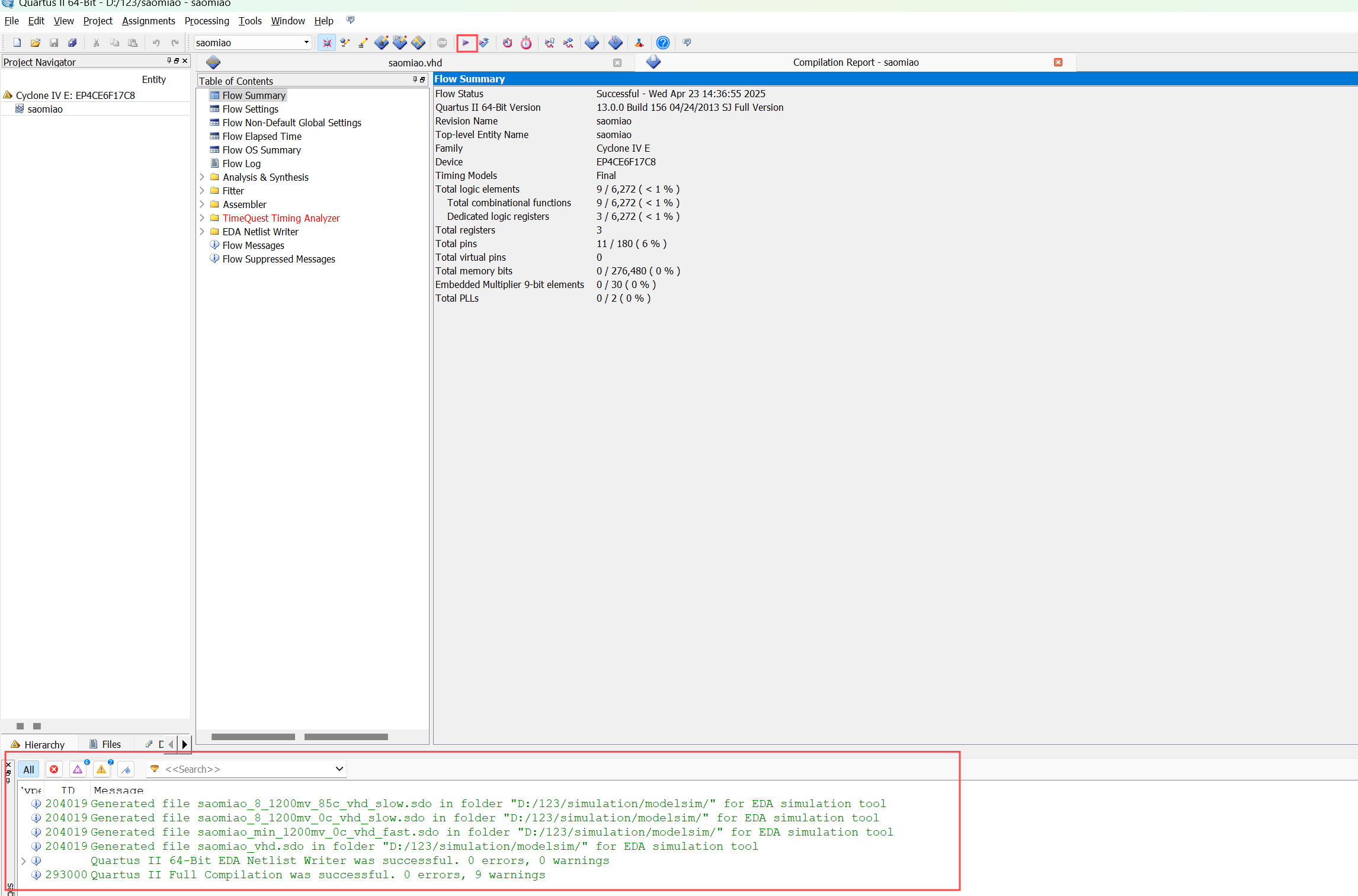

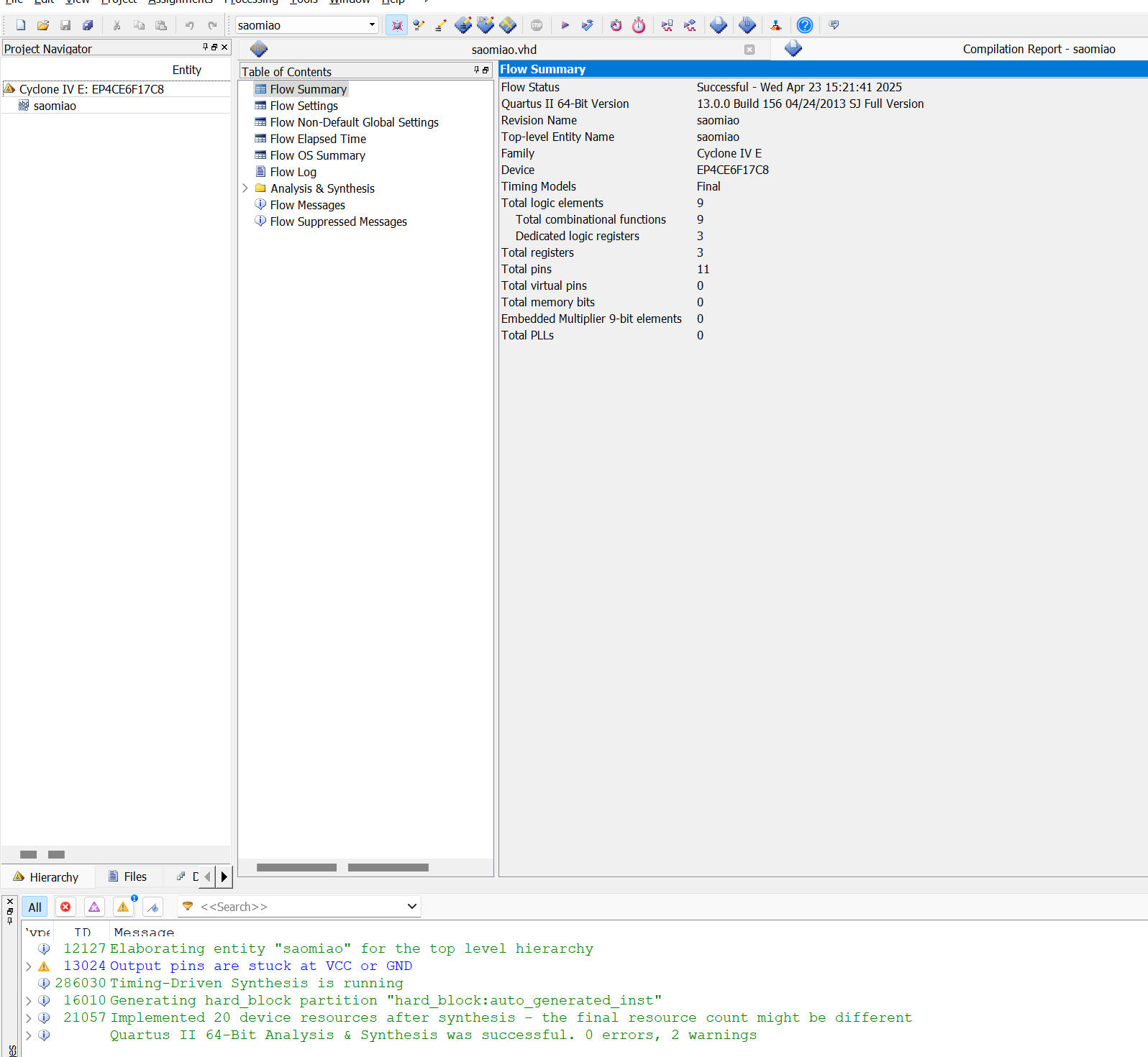

之后一直按Next --> finish即可。 运行代码直到出现以下界面,即为运行成功:

2、生成仿真文件夹

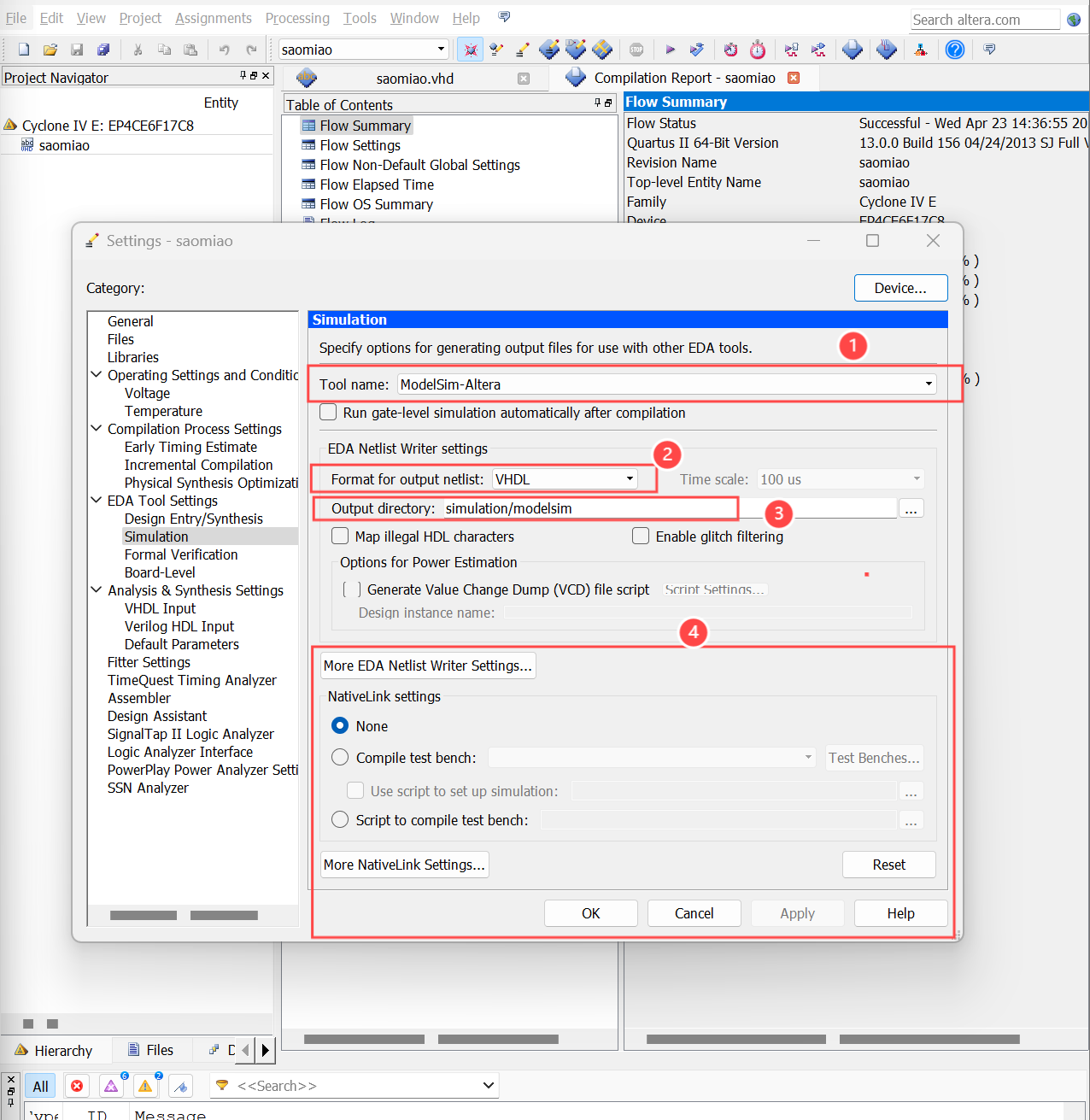

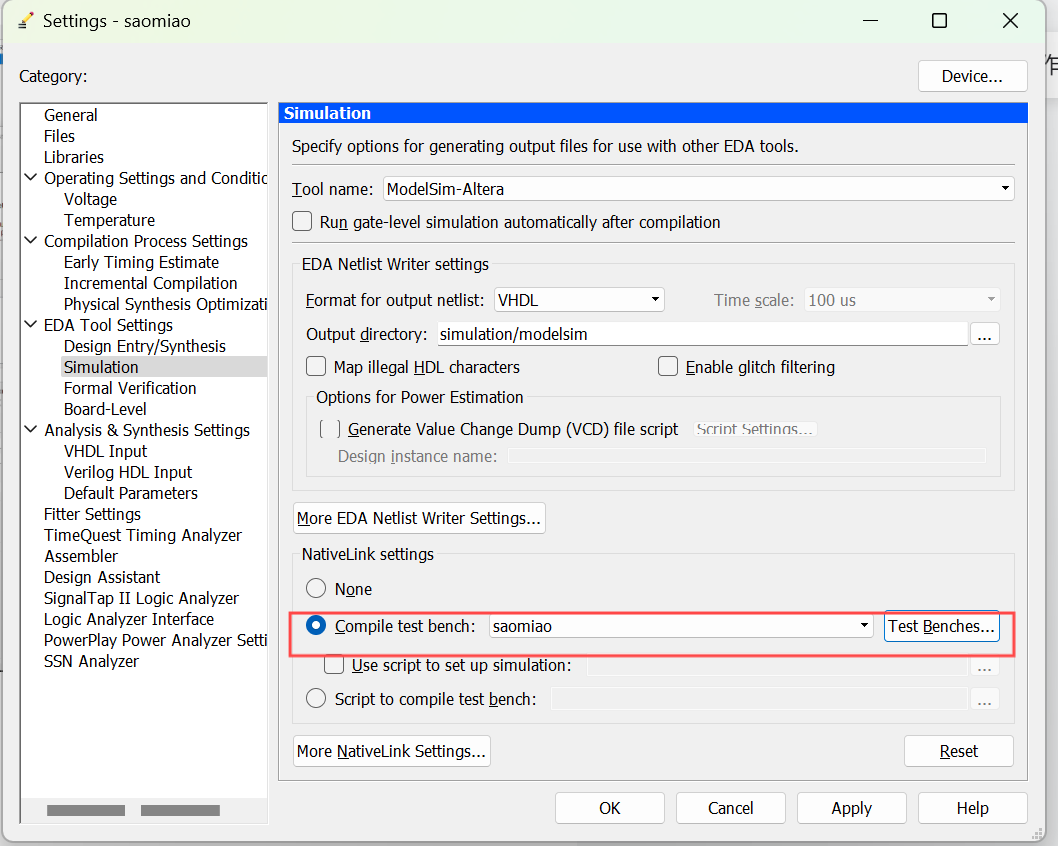

Assignments --> settings,会出现如下界面, 设置完成后,最后点击下面的Apply 和OK按钮退出设置。

注意:

1.Tool name:设置所用的仿真工具名称,选择ModelSlm-Altera或者ModelSlm,根据自己安装的环境而定。

2.Format for output netlist:设置工程编写用的代码VHDL,要与自己的工程代码一致。

3.Output directory:设置modelsim-altera的执行路径,要选择到自己安装的modelsim目录下,不然后续会报错,这个目录一般在123/工程目录下的saomiao文件夹的modelsim下 (即D:\123\simulation\modelsim)。

4.NativeLink settings:本地仿真链接设置,先选None,才能在工程下生成仿真simulation 文件夹。

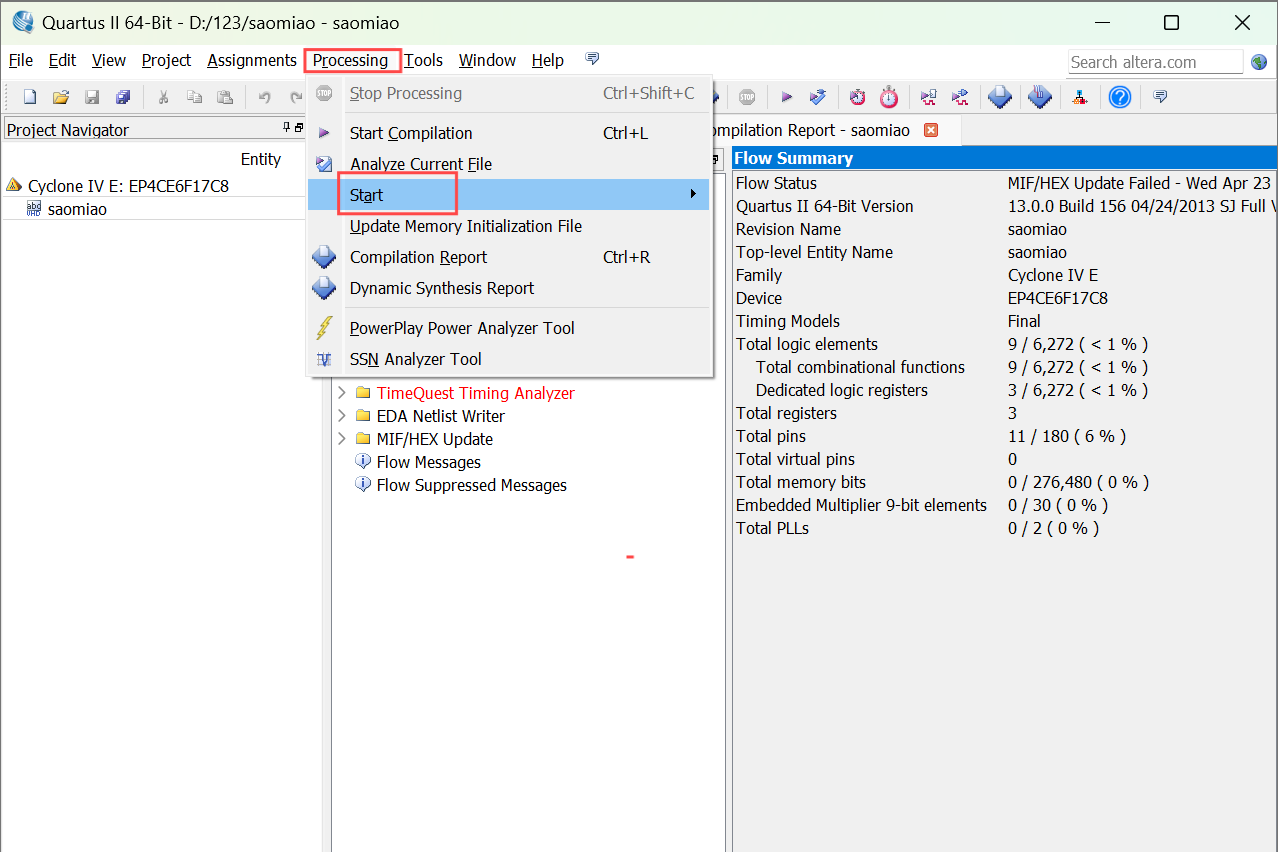

综合工程,点击Processing --> Start --> Start Analysis &Synthesis 编译通过,

3、设置工程仿真文件

有两种方法生成仿真文件:

(1)直接建立 xxx.vho文件

(2)自动生成工程仿真文件

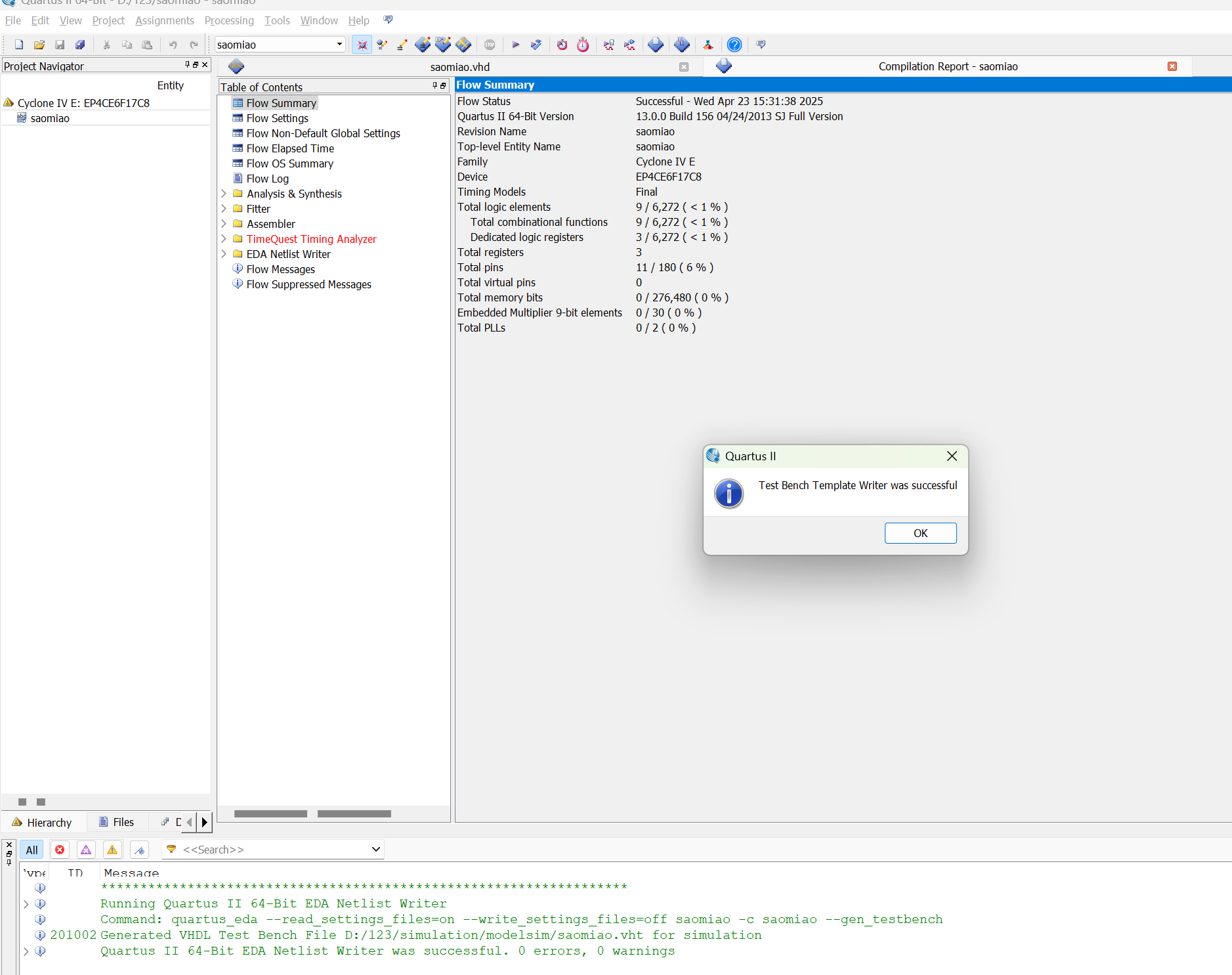

根据工程文件,自动生成仿真文件,点击 Processing->Start ->Start Test bench Template Writer,自动生成仿真文件后缀是 .vho。

注意: Quartus会根据语言生成对应的仿真网表文件(.vho为VHDL,.vo为Verilog)。

运行后出现如下界面:

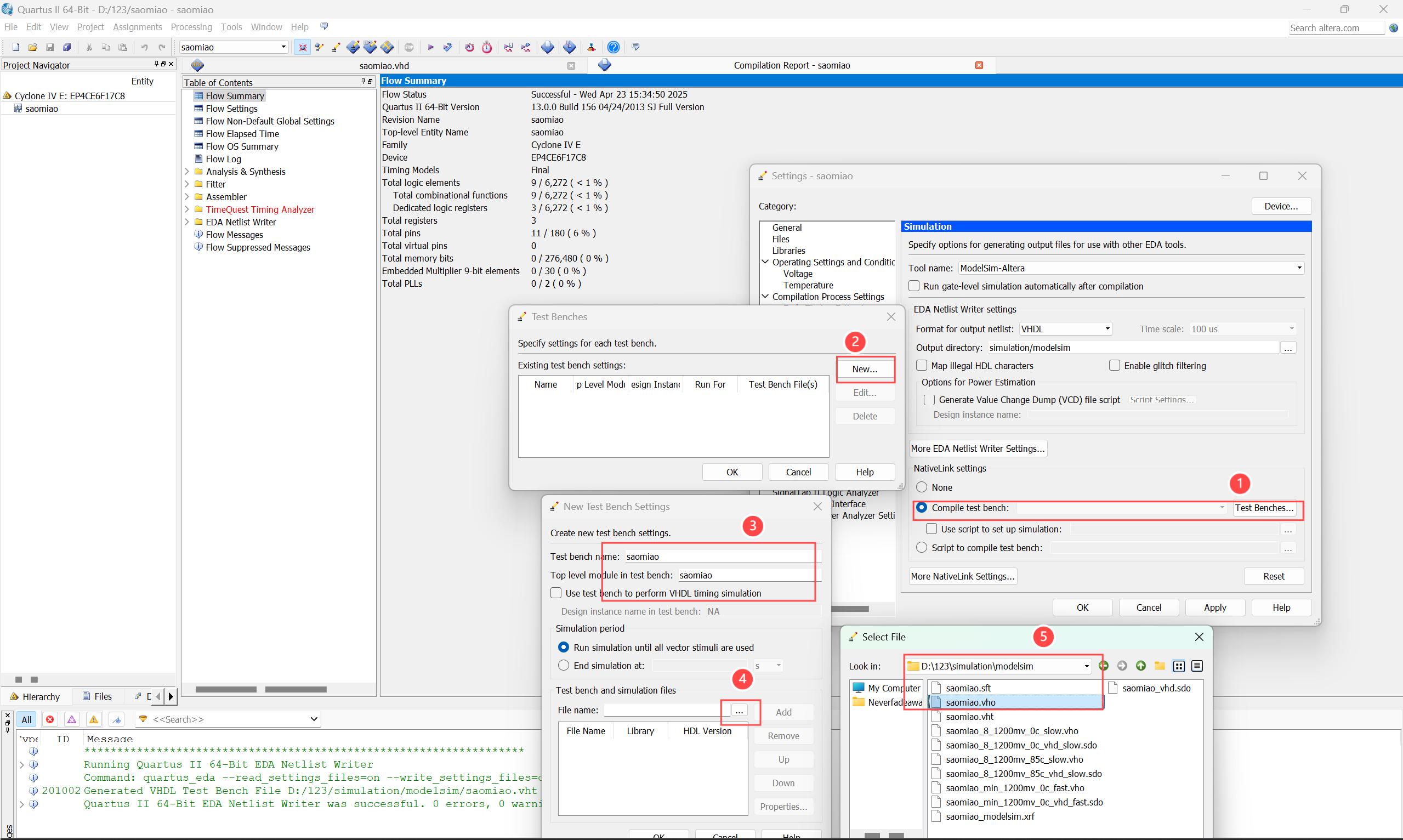

4、将仿真文件添加到工程中

将仿真文件(VHDL)添加到工程中,Assigments ->Settings

找到对应的.vho文件(工程仿真文件)。 Open --> Add --> ...... --> Apply --> Ok

注意:

其中第3步,Test bench name:标识当前Testbench文件配置的名称,仅用于Quartus工程管理,不影响仿真逻辑,不强制要求与VHDL实体名相同。

Top level module in test bench:指定Testbench的顶层实体/模块名,ModelSim将从这个模块开始仿真,必须与工程仿真文件中的实体名完全一致(区分大小写)。

故,这里直接取为工程文件中的实体名saomiao。

添加成功页面如下:

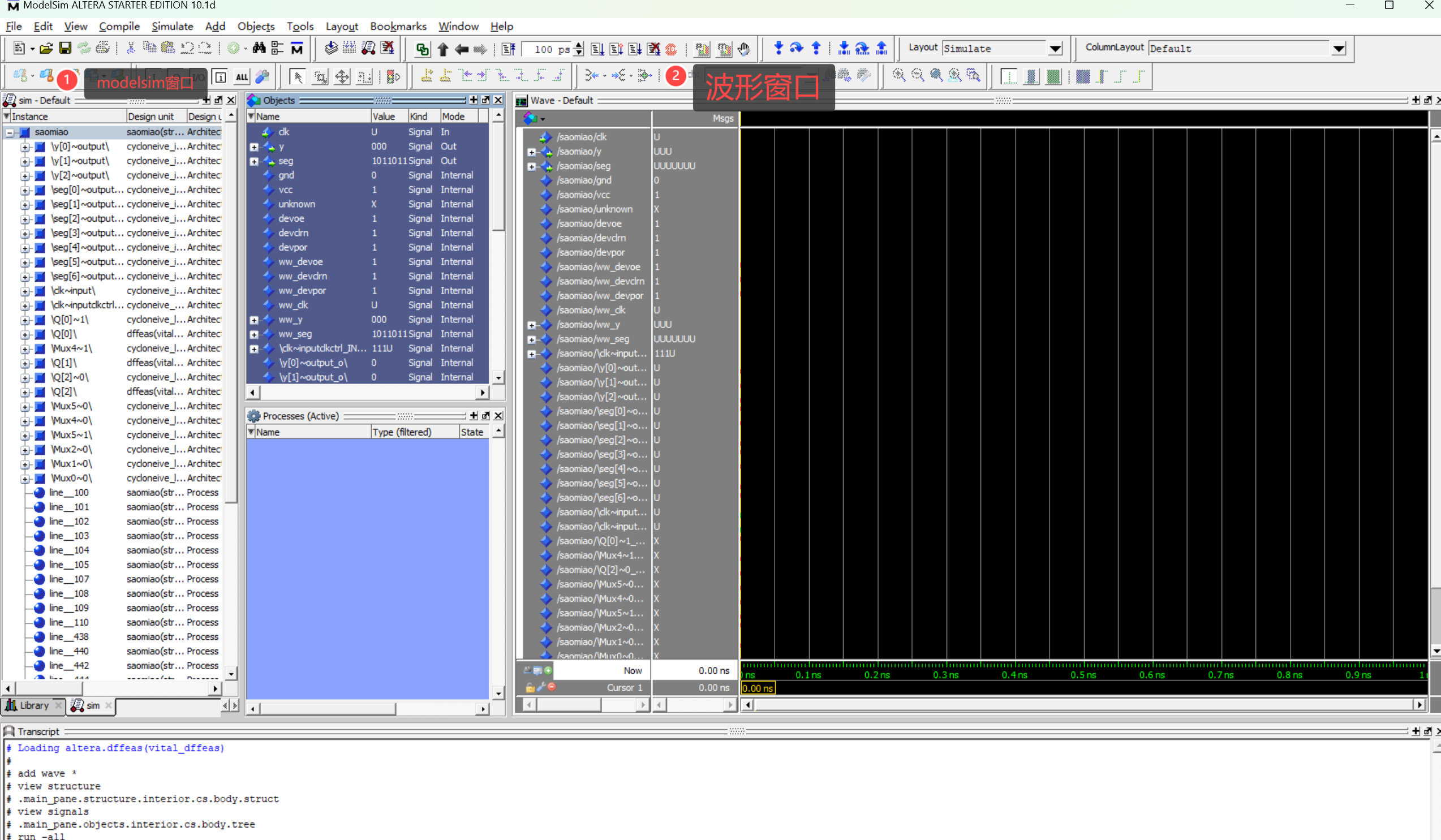

5、运行仿真

依次选择Tools ->Run Simulation Tool ->单击RTL Simulation 进入RTL仿真 ,会跳转到ModelSim页面:

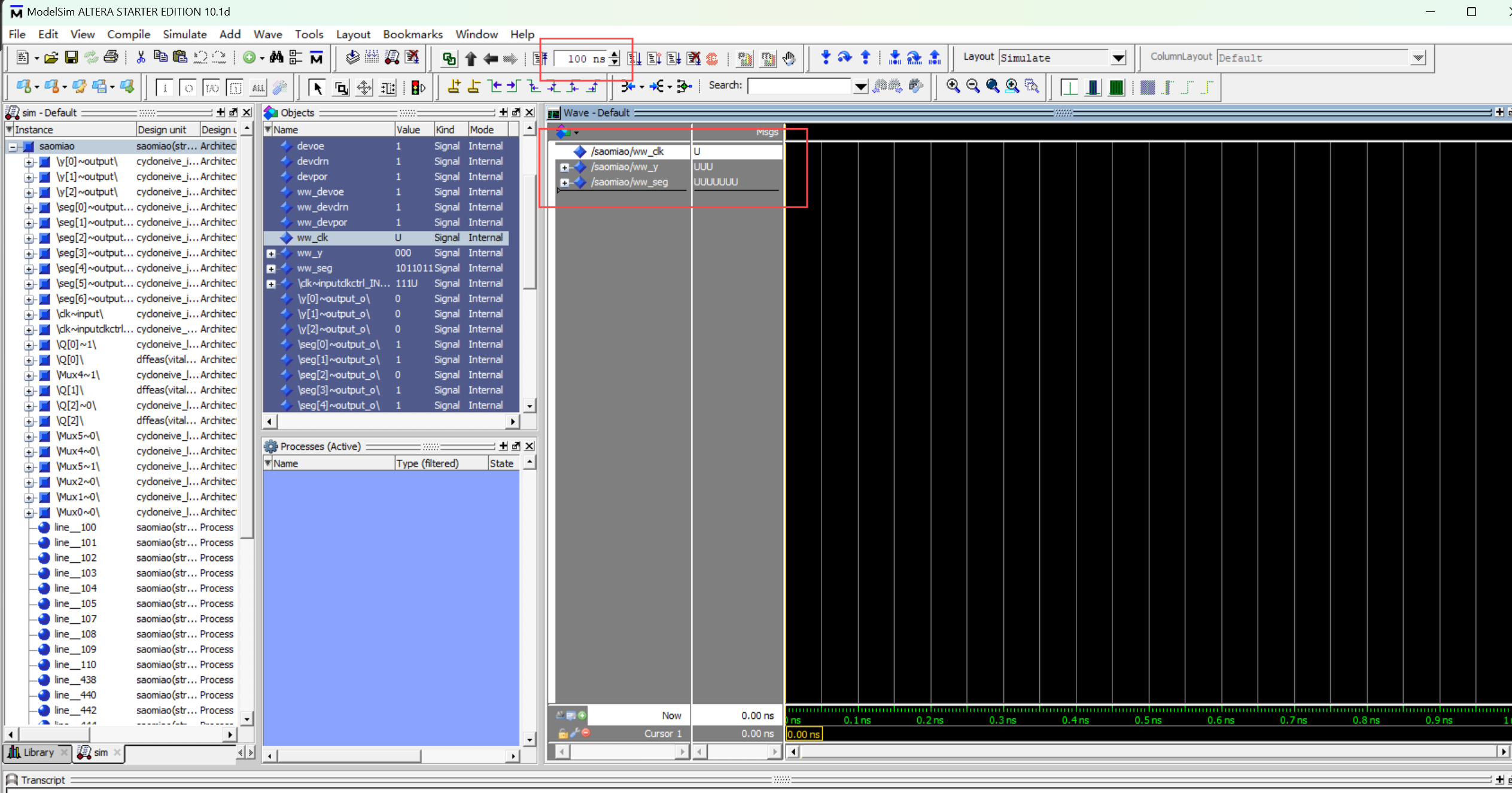

保留波形窗口中需要的输入输出量即可,

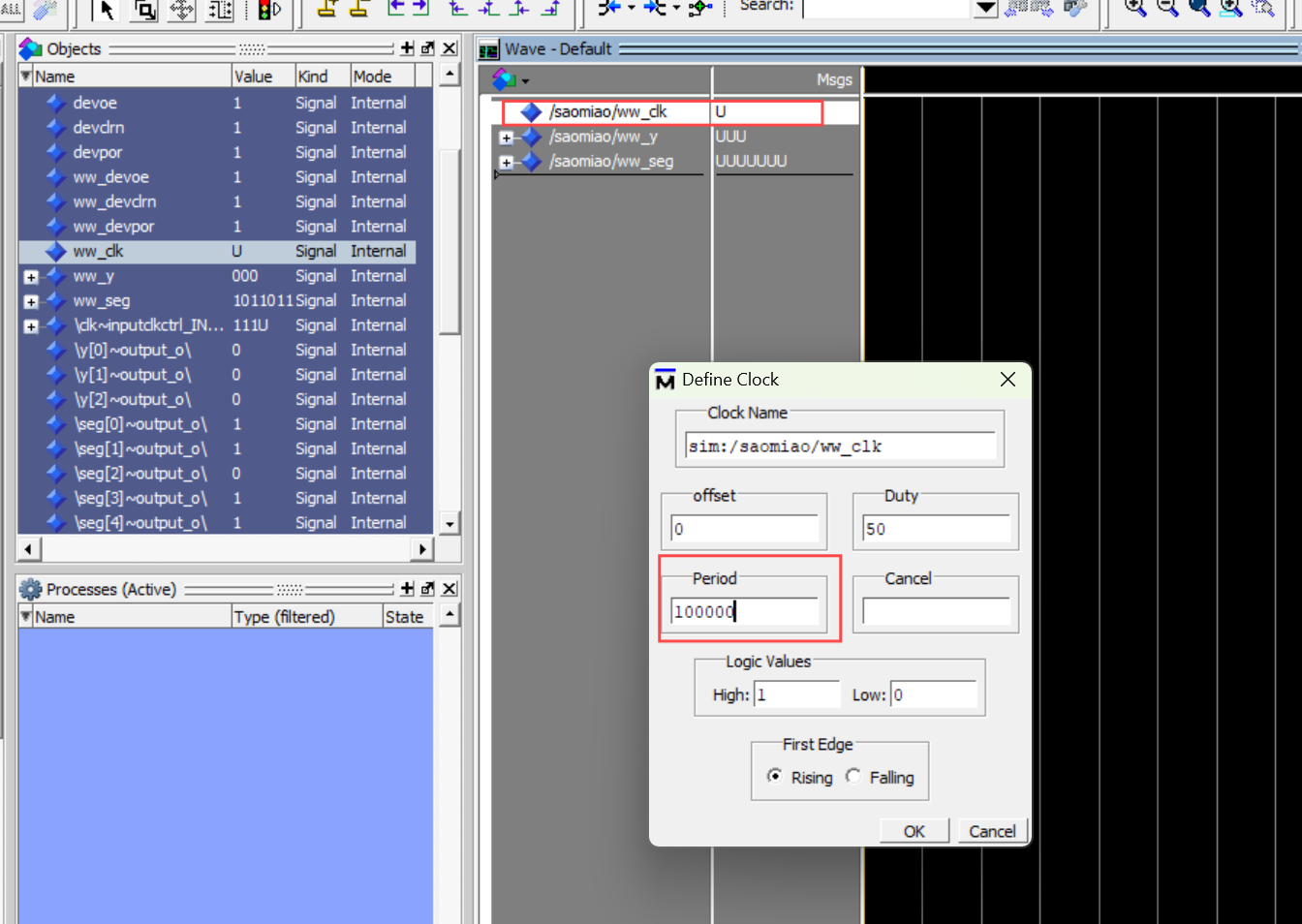

右键www.clk --> clock... --> 修改一下值即可。

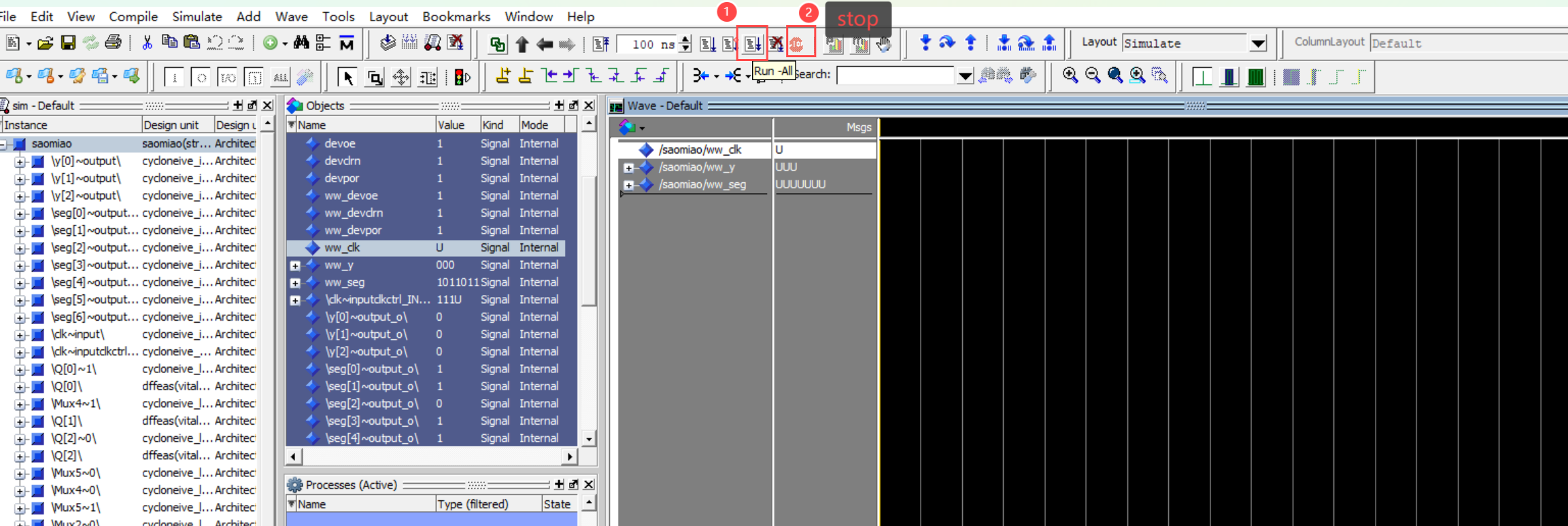

点击窗口上方工具栏Run all,运行起来,运行10s,差不多就可以停止了,点击stop:

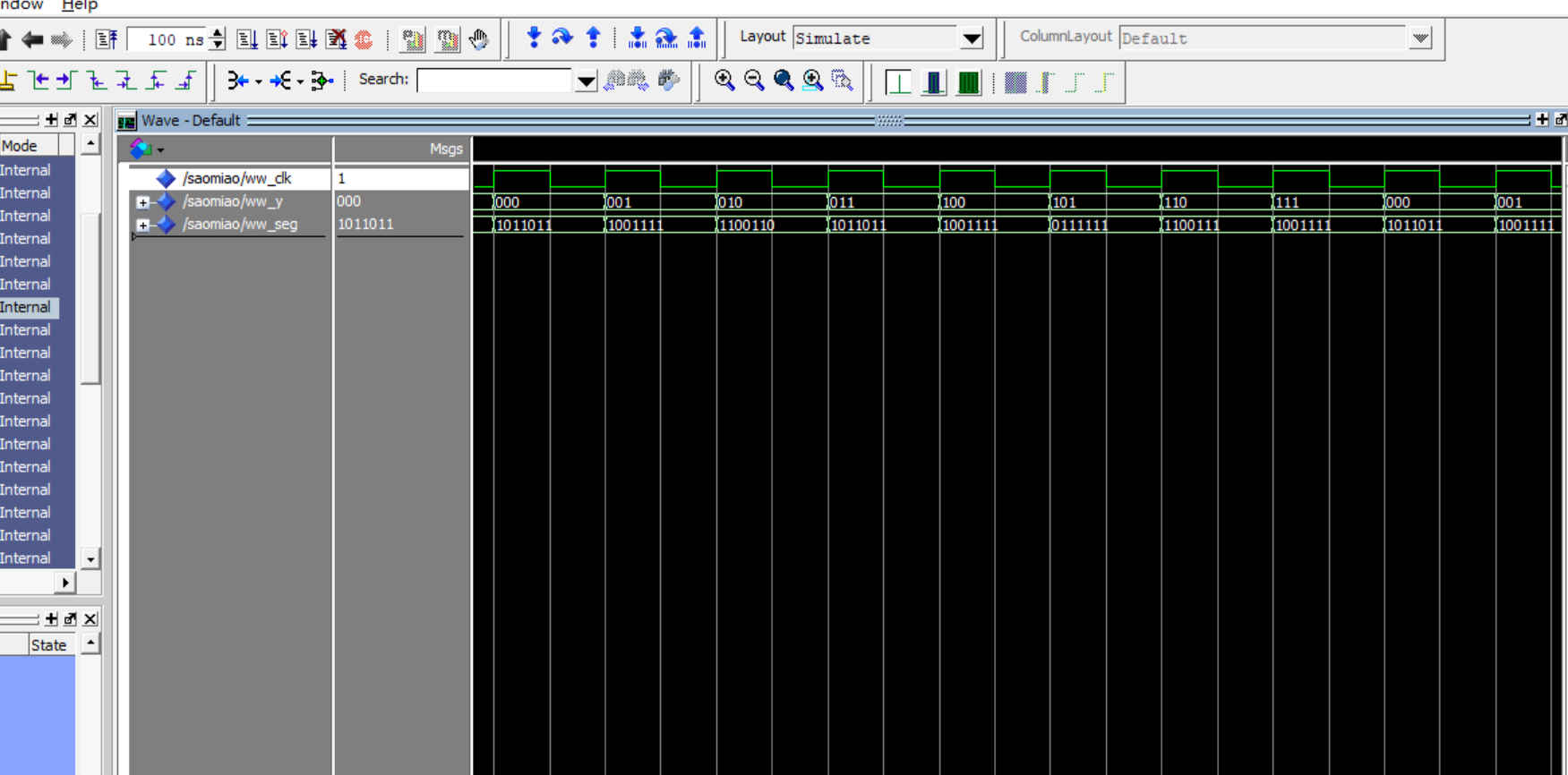

可以看到波形图,波形窗口可按ctrl+滚轮调节大小。

6、附录

可以显示学号为23423093:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY saomiao IS

port(clk:in std_logic;

y:out std_logic_vector(2 downto 0); --位码

seg:out std_logic_vector(6 downto 0)); --段码

END saomiao;

ARCHITECTURE one of saomiao is

signal Q:std_logic_vector(2 downto 0);

begin

process(clk)--计数器模块

begin

if clk' event and clk ='1' then

Q<=Q+1;

end if;

end process;

process(Q)--位码控制模块

begin

case Q is

when "000"=>y<="000";

when "001"=>y<="001";

when "010"=>y<="010";

when "011"=>y<="011";

when "100"=>y<="100";

when "101"=>y<="101";

when "110"=>y<="110";

when others=>y<="111";

end case;

end process;

process(q)--代码控制模块

begin

case q is

when "000"=>seg<="1011011";

when "001"=>seg<="1001111";

when "010"=>seg<="1100110";

when "011"=>seg<="1011011";

when "100"=>seg<="1001111";

when "101"=>seg<="0111111";

when "110"=>seg<="1100111";

when others=>seg<="1001111";

end case;

end process;

end one;以上就是我的一些学习经验,希望可以帮到大家。欢迎大家留言评论!!

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?