前言

网络上面有很多Quartus搭配modelsim仿真的文章,但是看了很多发现遇到了很多没出现过或分布各处的问题,网络上的解释非常的离散,因此这里把我遇到的所有的问题集中写下来,希望对初学者有用。

一、Quartus搭配Modelsim仿真全流程

本部分将详细介绍如何在Quartus中使用Modelsim完成仿真的过程,此处使用的是Quartus 18.0以及Modelsim 10.4版本。

编写verilog代码,确保能通过quartus的compile;

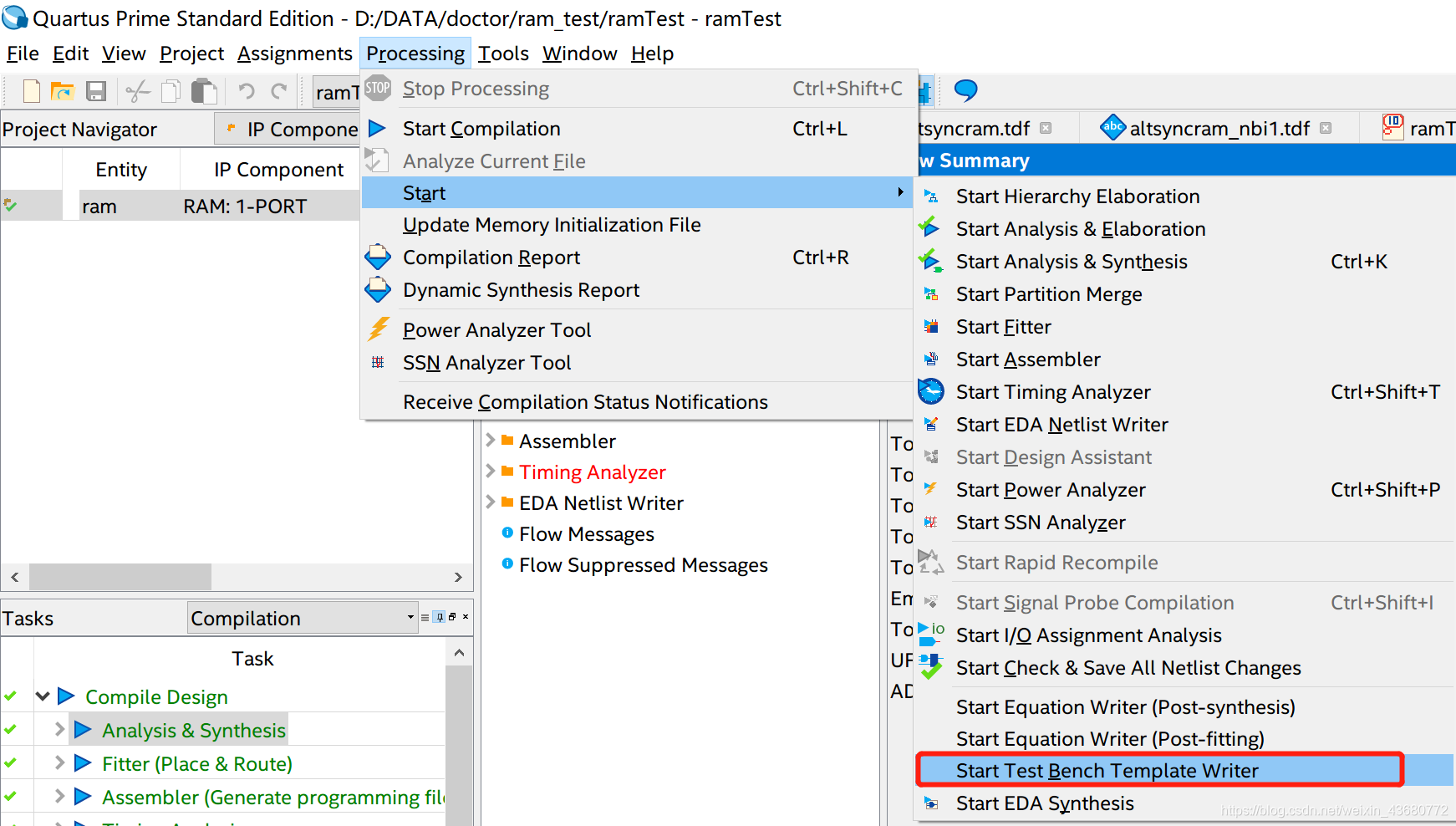

点击Processing-Start-Start Test Bench Template Writer,如下图所示

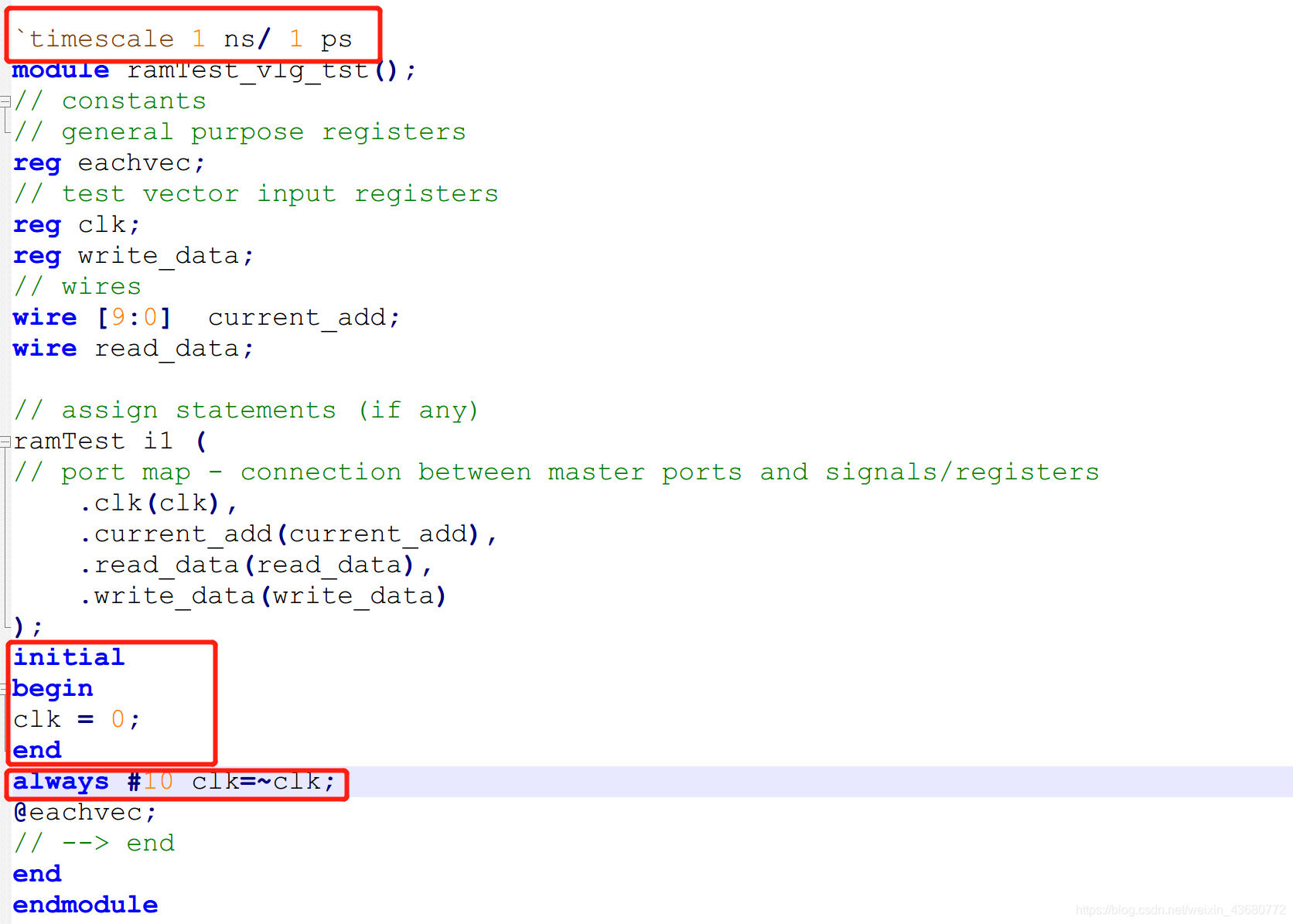

第2步会在当前项目目录下面的simulation-modelsin中生成一个与top-Level Entity名字一样的.vt文件,修改该.vt文件,关键修改三个地方:

1. 修改timescale为1ns/1ps

2. 修改initial begin中的内容,设置变量的初始值

3. 修改always begin块中的内容,修改为always语句,不用块包装

<

<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1028

1028

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?