高速PCB面临问题:电磁兼容,信号完整性,电源完整性。

1.1 高速信号

1.1.1 高速的界定

如果一个数字系统的时钟频率达到或者超过50MHz,而且工作在这个频率之上的电路已经占到了整个电子系统一定的分量(比如说1/3),这就称为高速电路。

实际上信号的谐波频率比信号本身的重复频率高,是信号快速变化的上升沿与下降沿引发了信号传输的非预期结果。因此,通常约定如果走线传播延时大于20%驱动端的信号上升时间,则认为此类信号是高速信号并可能产生传输线效应。

令 “Tr”为信号上升时间;“TD”为信号线传播延时

有如下经验法则:

如果Tr≥5TD,信号落在安全区域;

如果2TD≤Tr≤5TD,信号落在不确定区域;

如果Tr≤2TD,信号落在问题区域。

对于落在不确定区域及问题区域的信号(即Tr≤5TD),应该使用高速电路设计方法进行设计。

1.1.2 高速信号的频谱

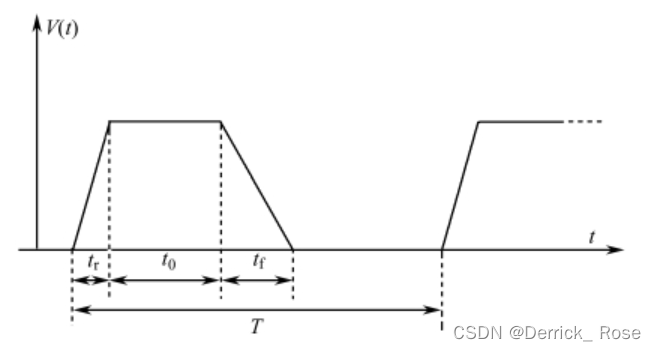

标准时钟信号波形是梯形的周期数字脉冲,如下图所示,脉冲周期为T,高电平维持时间为t0,信号上升时间为tr;信号下降时间为tf。且假设tr=tf。定义数字脉冲宽度为t0+tr。

通过傅里叶展开可以得到大致的时钟信号离散频谱。数字信号的频谱并不局限于其时钟频率,而是覆盖很宽的频率范围。

例如,一个时钟频率为33MHz的数字系统,它的三次谐波分量接近100MHz。电路板上的元件、走线、封装、连接器等互连结构在33MHz时可能不会带来问题,但是对于100MHz的谐波,趋肤效应、传输线效应开始出现,并影响信号的完整性。随着频率的升高,一段不起眼的导线、一个封装引脚都可能像天线一样辐射电磁波,带来电磁兼容性问题。此外,系统互连对不同频率的衰减不同,频率越高,衰减越大,这就可能带来信号波形退化等一系列问题。

1.1.3 集总与分布参数系统

在传统的低速数字设计中,通常认为一段走线是等电位的,忽略了它对信号传输的影响,但对于高速信号就没那么简单了。

集总参数系统:对于输入的该脉冲信号,在同一时刻线上各点的瞬时电位几乎是一致的,可以近似把它看做等电位的一点,这样的系统称之为集总参数系统。

分布参数系统:随着该脉冲信号沿走线传播,走线上各个点的电位在同一时刻是不一样的。这个系统对输入脉冲的响应沿走线是分布的,所以,从时域来看,称之为分布参数系统。

1.2 无源器件的高频特性

随着时钟速率的升高,其频谱相应的电磁波波长变得可与分立电路元件的尺寸相比拟时,电路上的走线、电阻、电容和电感等这些无源器件的响应开始偏移其理想特性。这时,必须建立这些元件的适用于高速电路的理想模型。要建立这种模型,必须了解这些元件和互连结构隐藏的高频特性。

1.2.1 金属导线和走线

事实上,每个元件都有引线电感,从硅胶片的连接导线到电阻、电容器和电感线圈的引线;相互靠近的金属引线之间存在电容;而每条走线都存在寄生的电容和电感,这些寄生元件影响走线的阻抗并且对频率敏感。

在低频段,导线主要呈现电阻特性,传导电流几乎均匀地分布在导体的横截面上。

但随着信号频率的升高,电流趋于导体表面,此时一段导体同时表现出电阻和电感特性。

随着频率的升高,导线的寄生电感效应逐渐占主导地位。

1.2.2 电阻

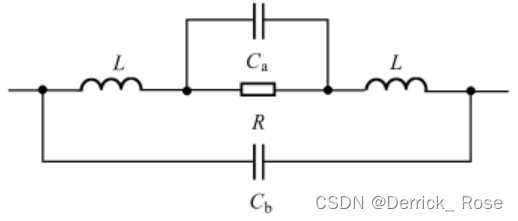

电阻的高频等效电路

L为两个金属引脚的电感;电容Ca为电阻内部的寄生电容;Cb为两个金属引脚间的寄生电容(可忽略)。

一般说来,较小的“SMD”封装的寄生参数较小,比如0603的封装比1206的封装更适合于高速的高频电路。

1.2.3 电容

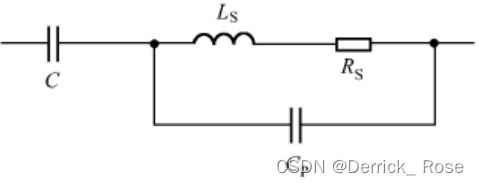

RS为等效串联电阻(ESR);LS为等效串联电感(ESL);CP为并联寄生电容(可忽略)。

1.2.4 电感和磁珠

电感线圈主要用来控制PCB内的“EMI”(电磁骚扰)。

电感的感抗是和频率成正比,XL=2πfL。

一个高速信号通过电感,会造成信号波形的失真,信号质量下降,所以电感线圈的高频特性限制了它只能用于1MHz频率以下。高频下通常采用磁珠代替电感线圈工作。

事实上,高速电路带来的问题并不是实际的电感线圈,高频电流流过导体时会产生电感。电流在PCB走线及电源/地网络上流动时同样会产生电感。

1.3 高速电路设计面临的问题

信号完整性、电源完整性和电磁兼容这三个方面是互相作用和影响的。

1.3.1 电磁兼容性

电磁兼容:“设备或系统在其电磁环境中能正常工作且不对该环境中的任何事物构成不能承受的电磁骚扰的能力。”

包括两方面的含义:

①设备、分系统或系统不应产生超过标准或规范规定的电磁骚扰发射限值。(发射干扰)

②设备、分系统或系统应满足标准或规范规定的电磁敏感性限值或抗扰度限值的要求。(抗干扰)

电磁敏感性:存在电磁骚扰的情况下,设备不能避免性能降低的能力。

抗扰度:设备面临电磁骚扰不降低运行性能的能力。

电磁骚扰发射:从骚扰源向外发出电磁能量的现象。这就是引起电磁干扰的原因。

电磁兼容设计分为3个层次:器件及PCB一级的设计、接地系统的设计及屏蔽系统设计和滤波设计。

1.3.2 信号完整性

信号完整性:信号在信号线上的质量,即信号在电路中以正确的时序和电压作出响应的能力。

高速PCB的信号完整性问题主要包括信号反射、串扰、信号延迟和时序错误。

1.3.3 电源完整性

电源完整性:系统运行过程中电源波动的情况,或者说电源波形的质量。

原文见《高速电路PCB设计与EMC技术分析》

3243

3243

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?