转载自:点击打开链接

1 testbench 的技巧

1)如果激励中有一些重复的项目,可以考虑将这些语句编写成一个 task,这样会给书写和仿真带来很大方便。例如,

一个存储器的 testbench 的激励可以包含 write, read 等 task。

2)如果 DUT 中包含双向信号(inout),在编写 testbench 时要注意。需要一个 reg 变量来表示其输入,还需要一个 wire

变量表示其输出。

3)如果 initial 块语句过于复杂,可以考虑将其分为互补相干的几个部分,用数个 initial 块来描述。在仿真时,这些

initial 块会并发运行。这样方便阅读和修改。

4)每个 testbench 都最好包含$stop 语句,用以指明仿真何时结束。

5)加载测试向量时,避免在时钟的上下沿变化,比如数据最好在时钟上升沿之前变化,这也符合建立时间的要求。

2 一个简单的例子

DUT:

testbench:

3 双向端口

这个没用过,从网上找的,如果有问题,大家再讨论吧芯片外部引脚很多都使用 inout 类型的,为的是节省管腿。一般信号线用做总线等双向数据传输的时候就要用到 INOUT

类型了。就是一个端口同时做输入和 输出。 inout 在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻

'Z'。当 inout 端口不输出时,将三态门置高阻。这样信号就不会因为两端同时 输出而出错了,更详细的内容可以搜索一

下三态门 tri-state 的资料

1 使用 inout 类型数据,可以用如下写法:

inout data_inout;

input data_in;

reg data_reg;//data_inout 的映象寄存器

reg link_data;

assign data_inout = link_data ? data_reg : 1’bz; //link_data 控制三态门

对于 data_reg,可以通过组合逻辑或者时序逻辑根据 data_in 对其赋值.

通过控制 link_data 的高低电平,从而设置 data_inout

是输出数据还是处于高阻态,如果处于高阻态,则此时当作输入端口使用.link_data 可以通过相关电路来控制.

2 编写测试模块时,对于 inout 类型的端口,需要定义成 wire 类型变量,而其它输入端口都定义成 reg 类型,

这两者是有区别的.

当上面例子中的 data_inout 用作输入时,需要赋值给 data_inout,其余情况可以断开.

此时可以用 assign 语句实现:assign data_inout = link ? data_in_t : 1’bz;

其中的 link ,data_in_t 是 reg 类型变量,在测试模块中赋值.

另外,可以设置一个输出端口观察 data_inout 用作输出的情况:

也就是说, 在内部模块最好不要出现 inout,如果确实需要,那么用两个 port 实现,到顶层的时候再用三态实现。理由

是:在非顶层模块用双向口的话,该双向口必然有它的上层跟它相连。既然是双向口,则上层至少有一个输入口和一

个输出口联到该双向口上,则发生两个内部输出单元连接到一起的情况出现,这样在综合时往往会出错。

对双向口,我们可以将其理解为 2 个分量:一个输入分量,一个输出分量。另外还需要一个控制信号控制输出分量何

时输出。此时,我们就可以很容易地对双向端口建模。

例子:

CODE:

可见,此时 input_of_inout 和 output_of_inout 就可以当作普通信号使用了。

在仿真的时候, 需要注意双向口的处理。如果是直接与另外一个模块的双向口连接,那么只要保证一个模块在输出的

时候,另外一个模块没有输出(处于高阻态)就可以了。

如果是在 ModelSim 中作为单独的模块仿真,那么在模块输出的时候,不能使用 force 命令将其设为高阻态,而是使用

release 命令将总线释放掉

很多初学者在写 testbench 进行仿真和验证的时候,被 inout 双向口难住了。仿真器老是提示错误不能进行。下面是我个

人对 inout 端口写 testbench 仿真的一些总结,并举例进行说明。在这里先要说明一下 inout 口在 testbench 中要定义为

wire 型变量。

先假设有一源代码为:

方法一:使用相反控制信号 inout 口,等于两个模块之间用 inout 双向口互连。这种方法要注意 assign 语句只能放在 initial

和 always 块内。

方法二: 使用 force 和 release 语句,但这种方法不能准确反映双向端口的信号变化,但这种方法可以反在块内。

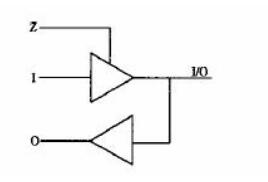

很多读者反映仿真双向端口的时候遇到困难,这里介绍一下双向端口的仿真方法。一个典型的双向端口如图所示。

典型的双向端口可以用 Verilog 语言描述如下:

仿真时需要验证双向端口能正确输出数据,以及正确读入数据,因此需要驱动 out_en 端口,

当 out_en 端口为 1 时,testbench 驱动 inner_port 端口,

然后检查 outer_port 端口输出的数据是否正确;

当 out_en 端口为 0 时, testbench 驱动outer_port 端口,

然后检查 inner_port 端口读入的数据是否正确。由于 inner_port 和 outer_port 端口都是双向端口 (在 VHDL

和 Verilog 语言中都用 inout 定义),因此驱动方法与单向端口有所不同。

用 Verilog 代码编写的 testbench 如下,其中使用了自动结果比较,随机化激励产生等技术。

638

638

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?