在大部分的电源滤波电路中,滤波电容通常是一大一小两个不同容值的电容并联组成,那么原因在哪里呢?能否用一个电容代替呢?下面我们就来简单探讨一下这些问题。

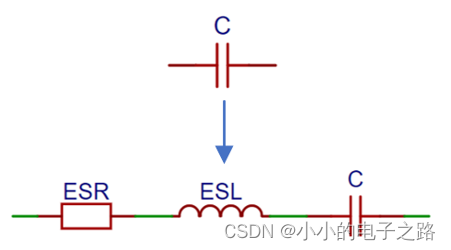

在解决上面的问题之前,我们必须要了解一下电容的高频等效模型。

随着半导体工艺的发展,我们大家都“被高频”或者“被高速”了,这使得按理想条件处理的器件,在实际使用中变得不再理想了。对于电容来说,在高频的条件下,它就不仅仅再是一颗电容了,而是一个由电阻、电容和电感组成的复合体,如下图所示,图中的电阻为等效串联电阻(ESR),电感为等效串联电感(ESL)。可以看出,C与ESL、ESR恰好组成了一个RLC串联谐振回路。

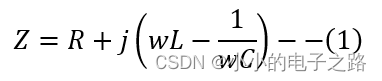

在这样的情况下,这一回路的阻抗可以表示为:

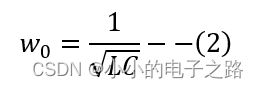

易知该谐振回路的谐振频率

这个频率称为该电容的自谐振频率。

若信号频率w<w0,此时电路的电抗小于0,电压落后于电流,电路呈容性。

若信号频率w>w0,此时电路的电抗大于0,电压超前于电流,电路呈感性。

分析到这里,我们要清楚一点,上面所分析的电路是电容的高频等效模型,也就是说,大家所看到的只是一颗电容。所以,现在我们就可以解释文章开头所提出的问题了。

在电容滤波电路中,一旦噪声频率过高,超出了电容的自谐振频率,那么此时的电容就不再是一颗电容了,而是相当于一颗电感,此时就不再具备我们想要的滤波能力了,因此我们需要一个小电容,其自谐振频率大于该噪声频率,这样才能滤去该噪声。这就是为何滤波电容通常由一大一小两个电容并联组成,而且通过上面的分析我们也应该明白,这两个电容是不能用一个电容代替的。

1583

1583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?