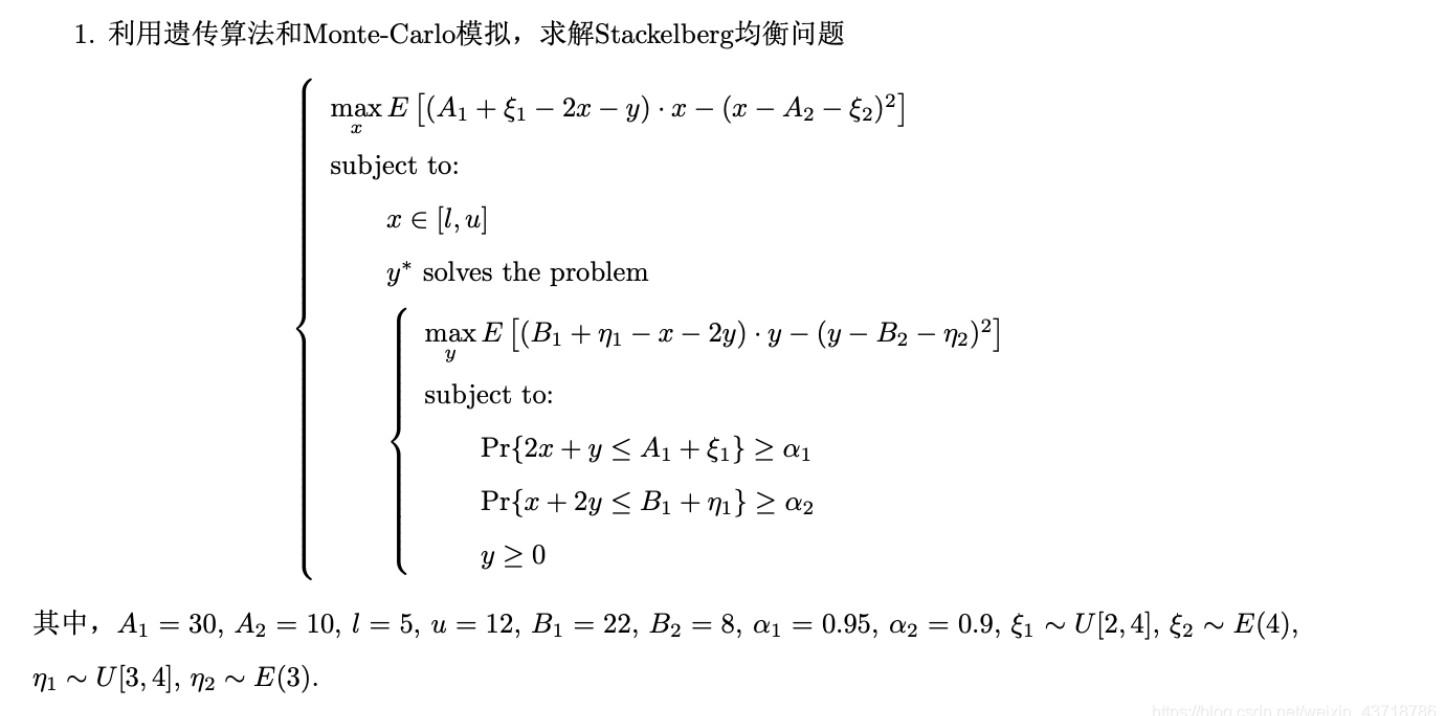

遗传算法,求解Stackelberg斯塔克伯格 均衡问题(主从博弈)

带概率约束条件

返回python代码和注释,可自行运行

ID:97900744228132315

code

模拟IC设计:深入探究9-12位SAR ADC与三阶Sigma-Delta调制器的设计实践

在现代集成电路设计中,模拟IC设计占据了举足轻重的地位。本文将聚焦于模拟IC设计中的关键领域,特别是针对9-12位SAR ADC(逐次逼近型模数转换器)以及与之紧密相关的三阶Sigma-Delta调制器的设计进行深入探讨。借助标准工艺,结合动态比较器和栅压自举开关等模块的应用,通过配套的完整测试电路,我们可以在Cadence仿真环境中实现对整个设计流程的模拟与优化。

一、SAR ADC概述及设计要点

SAR ADC作为现代模拟IC设计中的核心组件之一,其性能直接影响到整个系统的精度和稳定性。SAR ADC的基本原理是利用逐次逼近法完成模数转换,其设计过程中需关注位数选择、转换速度、功耗与面积优化等方面。本文将聚焦于9-12位SAR ADC的设计,探讨如何在保证性能的同时实现优化。

二、三阶Sigma-Delta调制器的原理及应用

三阶Sigma-Delta调制器在SAR ADC中扮演着关键角色,其性能直接影响到系统的噪声性能和动态范围。本文将介绍三阶Sigma-Delta调制器的基本原理、结构及其在SAR ADC中的应用,分析如何通过优化调制器参数来提升系统性能。

三、标准工艺与关键模块的应用

在现代模拟IC设计中,标准工艺的应用是实现设计效率与性能的关键。本文将探讨如何在标准工艺下,结合动态比较器和栅压自举开关等模块的应用,实现SAR ADC和Sigma-Delta调制器的优化设计。动态比较器的设计是实现快速、准确模数转换的关键,而栅压自举开关则有助于提高电路的可靠性和稳定性。

四、Cadence仿真环境中的应用实践

Cadence仿真环境是模拟IC设计中的关键工具,通过配套的完整测试电路,我们可以实现对SAR ADC和Sigma-Delta调制器的全面仿真与优化。本文将介绍如何在Cadence仿真环境中进行模拟IC设计,包括电路搭建、仿真验证、性能分析等环节,探讨如何通过仿真优化来提升设计性能。

五、设计流程中的挑战与对策

在SAR ADC和Sigma-Delta调制器的设计过程中,我们面临着诸多挑战,如噪声、失真、功耗等问题。本文将分析这些挑战的产生原因,并探讨相应的解决对策。通过优化电路设计、改进工艺方法、提高仿真精度等手段,我们可以有效地应对这些挑战,提升设计性能。

六、总结与展望

本文详细探讨了模拟IC设计中9-12位SAR ADC与三阶Sigma-Delta调制器的设计实践。通过标准工艺的应用、关键模块的结合以及Cadence仿真环境的实践,我们可以实现对整个设计流程的模拟与优化。面对未来的技术挑战与发展趋势,我们需要不断深入研究、创新技术,以推动模拟IC设计的不断进步。

相关的代码,程序地址如下:http://matup.cn/744228132315.html

7042

7042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?