一、 实验目的

1. 学习UART接口时序协议

2. 掌握FPGA/CPLD实现异串行通信模块的设计与实现方法。

3. 对UART通信接口电路进行功能模块划分,对各模块进行详细的功能定义;对划分好的功能模块进行详细编程设计及仿真设计,包括定时计数、显示、时间调整、响铃等;分析仿真结果,并进行顶层模块设计及功能测试。

完整可执行工程文件见文末。

二、 实验过程步骤

1、模块功能要求

(1)硬件工作原理

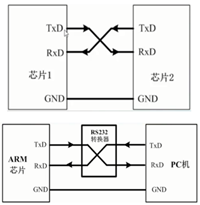

UART引脚连接方法,如下图所示:

RXD:数据输入引脚,接收数据信号;TXD:数据发送引脚,发送数据信号。

对于两个芯片之间的连接,两个芯片GND共地,同时TXD和RXD交叉连接。这里的交叉连接的意思就是,芯片1的RxD连接芯片2的TXD,芯片2的RXD连接芯片1的TXD。这样,两个芯片之间就可以进行TTL电平通信了。若是芯片与PC机(或上位机)相连,除了共地之外,就不能这样直接交叉连接了。 尽管PC机和芯片都有TXD和RXD引脚,但是通常PC机(或上位机)通常使用的都是RS232 接口(通常为DB9封装),因此不能直接交叉连接。RS232接口是9针(或引脚),通常是TxD和RxD经过电平转换得到的。故,要想使得芯片与PC机的RS232接口直接通信,需要将芯片的输入输出端口电平转换成rs232类型,再交叉连接。经过电平转换后,芯片串口和rs232的电平标准是不一样的:控制器件如FPGA/CPLD或者单片机的电平标准(TTL电平):+5V表示1,0V表示0;Rs232的电平标准:+15/+13 V表示0,-15/-13表示1。RS-232通讯协议标准串口的设备间通讯结构图如下:

2、实验步骤

(1)利用wizard新建项目,所选器件为

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2422

2422

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?