时源芯微 每天一个EMC小知识 根据真实经验编写 需要EMC整改 欢迎咨询

在时钟信号中使用RC滤波电路时,需在抑制噪声和保持信号完整性之间谨慎权衡。以下是设计要点、参数选择及优化方案:

一、时钟信号滤波的核心矛盾

-

时钟信号特性:

-

高频(MHz~GHz)、快速边沿(ns级)、周期性方波。

-

关键参数:上升时间(tr)、过冲(Overshoot)、抖动(Jitter)。

-

-

滤波需求:

-

滤除高频噪声(如开关电源耦合、EMI干扰)。

-

但RC滤波会减缓边沿速度,可能引发时序问题(如建立/保持时间违例)。

-

二、RC滤波电路设计要点

1. 参数选择

-

截止频率(fc):

-

原则:fcfc应高于时钟基频,但低于需滤除的噪声频率。

示例: -

时钟频率50MHz(基频),噪声在200MHz以上,选fc=100MHz。

-

若R=50Ω,则C≈32pF。

-

-

电阻(R)与电容(C)的权衡:

-

小R值(如10~50Ω):减少信号压降,但需更大C才能达到相同fcfc。

-

小C值(如10~100pF):减小对边沿时间的劣化,但高频滤波能力弱。

-

2. 对信号边沿的影响

-

上升时间延长:

tr,RC≈2.2RC

RC电路将时钟边沿近似为指数曲线,等效上升时间为:示例:R=50Ω,C=10pF → tr,RC=1.1ns。

-

若原时钟边沿tr=0.5ns,滤波后总边沿时间:

-

需确保总边沿时间小于系统时序余量(如小于时钟周期的10%)。

-

-

过冲抑制:

RC滤波可阻尼反射引起的过冲,但需避免过度减缓边沿导致信号幅值不足。

三、优化方案

1. 分段滤波(针对宽频噪声)

-

高频噪声:并联小电容(如1~10pF陶瓷电容)就近放置在时钟源端。

-

低频噪声:串联稍大电容(如100pF)靠近负载端。

示例拓扑:时钟源 → [10pF] → [50Ω] → [100pF] → 负载

2. 阻抗匹配与端接

-

端接电阻:

在RC滤波后增加端接电阻(如50Ω),抑制反射,减少振铃。

示例:RC滤波 → 端接电阻 → 负载

3. 替代方案

-

磁珠+电容滤波:

-

磁珠(如600Ω@100MHz)串联,电容(如10pF)对地,针对性抑制特定频段噪声。

-

优点:高频阻抗高,对边沿时间影响较小。

-

-

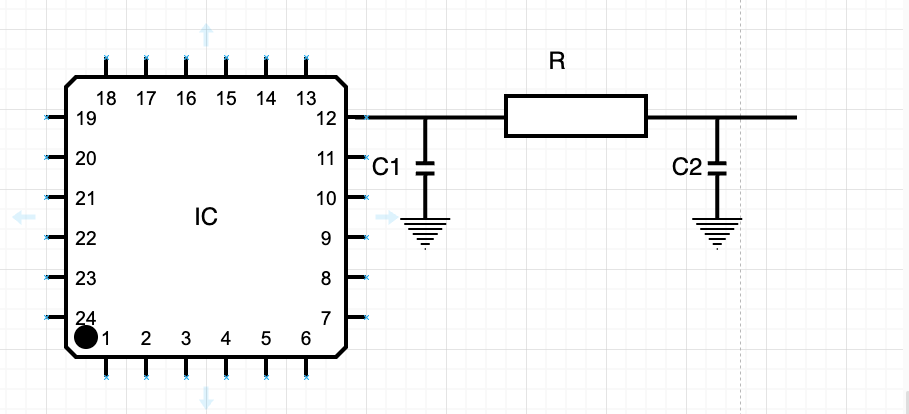

π型滤波:

使用两级电容(如C1=10pF, C2=10pF)和电阻(R=50Ω),提升高频抑制能力。

四、布局与实测验证

1. 布局规则

-

最短路径:RC电路尽量靠近时钟源或噪声注入点。

-

避免跨分割:滤波电路的地回路需连接至同一低阻抗地平面。

-

隔离敏感线路:时钟排线远离电源或高速数据线,间距≥3倍线宽。

2. 实测验证

-

工具:

-

示波器(测量边沿时间、过冲)。

-

频谱分析仪(检测噪声抑制效果)。

-

-

关键步骤:

-

测量滤波前后的时钟边沿时间(trtr)和抖动(RMS Jitter)。

-

对比时序余量(如Setup/Hold Time)。

-

用近场探头扫描排线,确认噪声衰减是否达标。

-

五、典型应用场景

1. 单片机时钟滤波

-

场景:STM32的8MHz外部时钟受开关电源噪声干扰。

-

方案:

-

R=33Ω,C=15pF → fc≈320MHz。

-

实测结果:200MHz以上噪声衰减20dB,边沿时间从2ns增至2.5ns(可接受)。

-

2. 高速SerDes参考时钟

-

场景:PCIe 100MHz参考时钟需抑制10GHz以上噪声。

-

方案:

-

磁珠(2000Ω@1GHz)串联 + 0402封装2.2pF电容对地。

-

边沿时间几乎不变,10GHz噪声衰减40dB。

-

3. 长距离时钟传输

-

场景:10MHz时钟通过0.5m排线传输至多设备,存在反射过冲。

-

方案:

-

源端串联R=22Ω + 负载端C=22pF。

-

过冲从30%降至5%,时序抖动改善50%。

-

六、总结

时钟信号RC滤波需严格平衡噪声抑制与信号完整性:

-

低频时钟(≤50MHz):可适当使用RC滤波,优先选小R值(10~50Ω)和小C值(10~100pF)。

-

高频时钟(≥100MHz):建议改用磁珠或π型滤波,减少边沿劣化。

-

关键验证指标:上升时间、过冲、抖动、时序余量。

-

替代方案:磁珠、端接电阻、屏蔽排线结合使用,综合优化EMC性能。

1341

1341

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?