hello,这里是晴空-Tiso~

本篇博客我们介绍一下模块库中的iic主机驱动,iic在基本通信里面其实是一个稍微复杂一些的内容,比起SPI难度要高上一些,但是我们这边还是一样将其包装成了一个能让大家简易使用的模块,阿空为了能既让模块简易使用,又能灵活适配上IIC通信本身的复杂协议功能,其实也是费了一番心思,在这里详细的来跟大家解说一下我们模块的端口设计和对应的使用方式。

如果这个模块对您有所帮助,您也可以去看看我们的模块库哔哩哔哩工房 (bilibili.com),让它来为您的FPGA电子世界添砖加瓦,再次感谢大家~

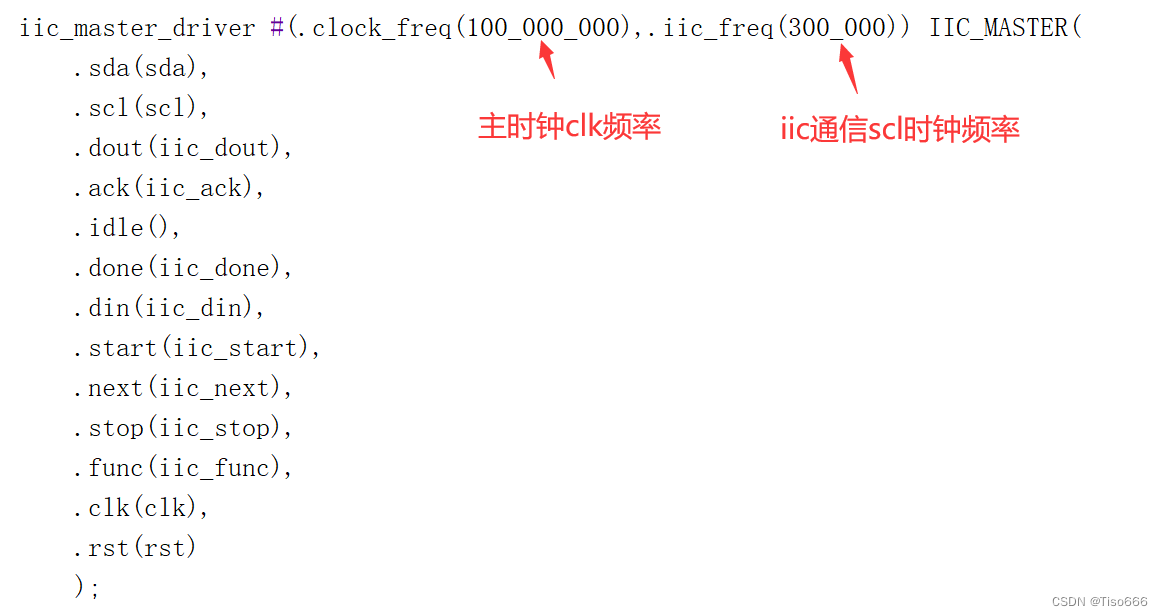

首先我们还是先来看一下我们的参数设置,我们首先需要先给定我们的主时钟频率,主时钟我们一般会选择使用50或者100M晶振直接接入,或者锁相环等时钟模块生成后的时钟接入,这个参数只需要根据对应的时钟频率填写就可以了。IIC通信时钟则是我们scl的一个时钟频率,这个一般对应的器件会有一定的上限,iic器件本身也分低速、中速和高速。那么我们根据对应从机器件速度类型,自己给定合适的频率参数,模块就会自动生成。

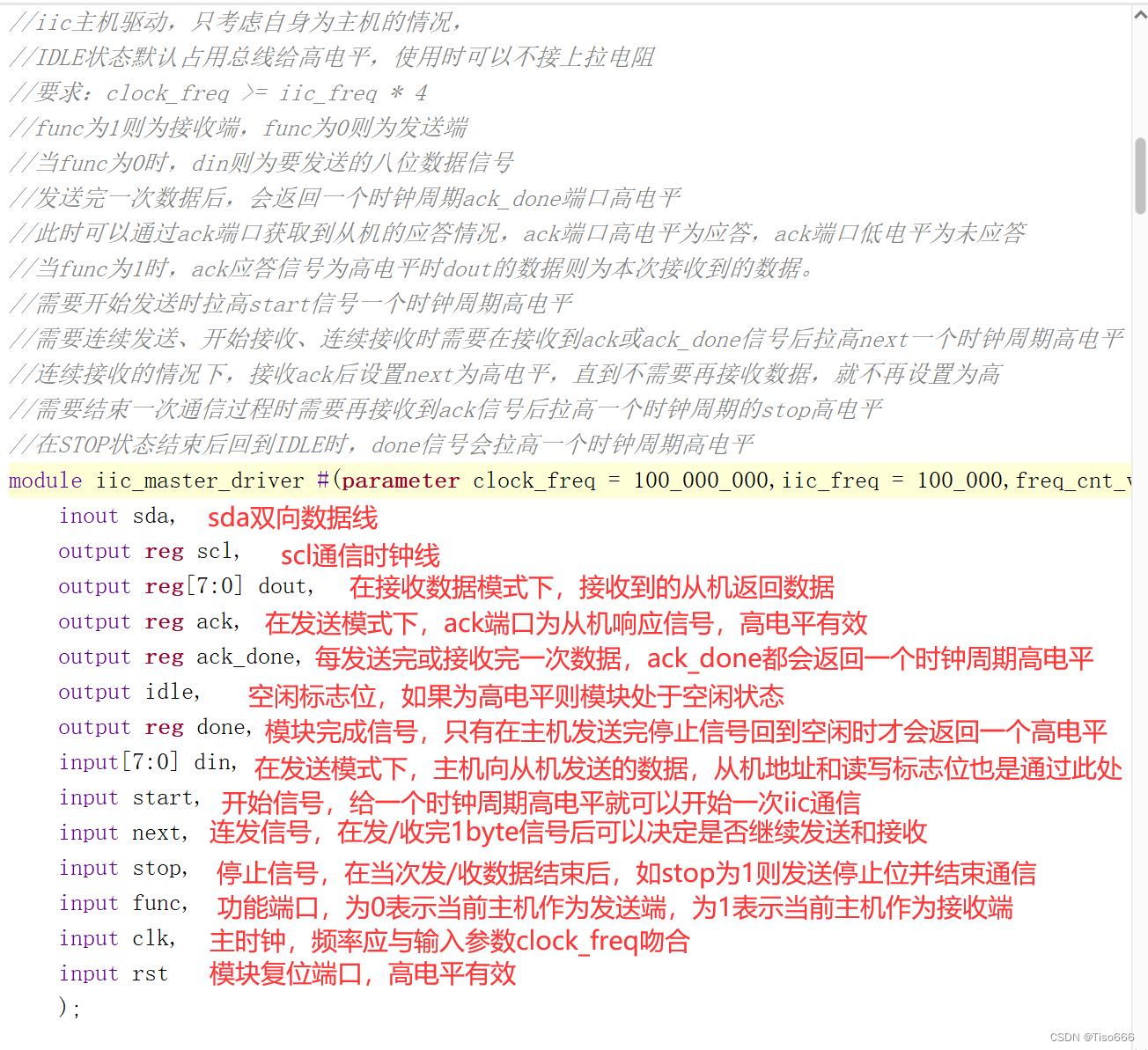

接下来我们就需要来看对应的端口列表了,上面的注释也是一些说明书一样的内容,大家感兴趣的话可以看一下。我们在这里对几个重要的控制端口来进行一下描述说明,首先,毫无疑问,sda和scl直接与从机连接,start端口控制主机模块发起一次通信,此时,主机驱动就会开始发送开始位。发送完开始位之后就会将din的数据(此时是地址位+读写控制位)发送出去,此时,func要设置为0(发送模式)。在接收到ack_done高电平的时候判断ack是否也为高电平(从机是否做了应答),如果从机应答了,next设置为1(因为IIC通信第一个byte数据必定为地址位,所以如果要收发数据一定要继续通信),func根据是要进行发送还是读写进行设置。如果是主机发送数据给从机,则发送的数据在din端进行输入更新,如果是主机接收从机发回的数据,则在ack_done到来的时候通过dout获取从机发回来的1byte数据。

而当通信需要结束的时候,则可以将stop端口设置为1,发送IIC停止位并结束此次通信,通信彻底接收回到空闲状态时,done信号会返回一个时钟周期高电平,idle信号则会在处于空闲时一直为高电平。

本次我们介绍了我们模块库里的IIC主机驱动功能,下次我们再向大家展示一下使用该模块的具体例化过程。

写FPGA参数化模块,阿空是很认真的,也希望这份认真可以帮助到更多热爱FPGA的小伙伴。

模块库目前已售出超过两百份,非常感谢大家的支持,阿空也会努力继续给大家更新更多的模块~

CSDN上的解说文档主要是向购买了模块库的小伙伴对各个模块的使用介绍和答疑

也希望阿空模块库的各个参数化模块能像一块块积木一样,帮助各位热爱FPGA的小伙伴们搭建起来自己的逻辑电路城堡!

模块库获取链接(B站工房):哔哩哔哩工房 (bilibili.com)

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?