本文使用的环境为:Diamond 3.9 modelsim se 10.0c。具体安装步骤请参考相关文档,modelsim在安装后需要配置好环境变量。

其中modelsim se 10.0c版本相对较低,请参考本文的设计者选择更高版本。

主要分成以下几个步骤:

- 建立仿真库

- 编译库

- 建立Diamond关联modelsim

- 仿真

step1 . 建立仿真库

在使用modelsim的时候,经常需要建立不同厂商的仿真库,例如Xilinx,Altera,Lattice等,推荐在modelsim安装根目录下新建对应厂商仿真库文件夹。以Lattice为例,在X:\modeltech_10.0c下建立文件夹Lattice.

step2 . 去掉modelsim安装根目录下modelsim.ini的只读属性,以方便在编译库的时候自动添加仿真库信息。

step3 . 设置仿真库存放的路径。打开modelsim,File >> change directory,选择在第1步新建的文件夹“Lattice”,如下图所示:

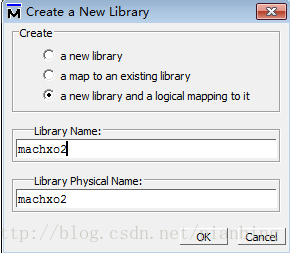

step4 . 根据实际开发的Lattice Device的Family来确定需要编译的库,然后在modelsim中输入对应的库的名称。例如在本文中使用的器件为ECP3系列器件,在modelsim中选择File >> New >> Library中的Library Name中输入ECP3

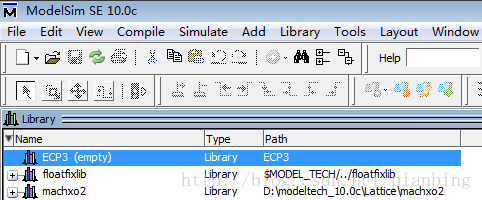

输入完成后,ECP3库变成如下形态(empty)

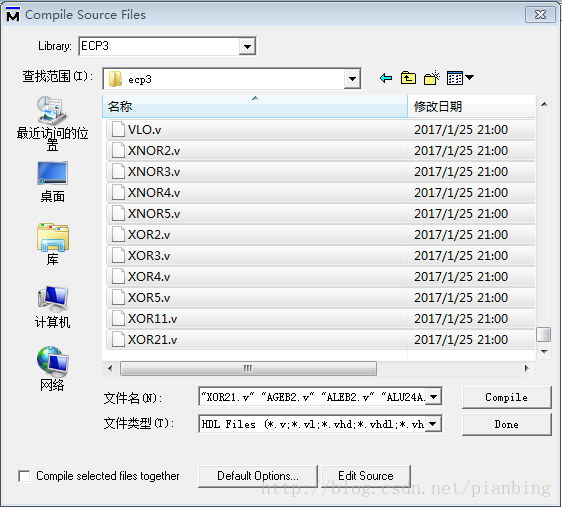

step5 . 选中空库(ECP3(empty)),在modelsim的菜单栏中选择Compile >> Compile,出现如下对话框,注意在Library中选择刚才新建的库(ECP3),在“查找范围”中,选择Lattice对应Family的器件需要编译的文件,在编译的时候一般需要编译两个文件夹下的子文件,在本例中一个为ecp3文件夹下的所有文件,另一个为pmi文件夹下的所有文件。在编译以前,一定要确认需要仿真的顶层文件是verilog还是VHDL。如果是verilog文件,那么需要编译的库文件的路径为:X:\lscc\diamond\3.9\cae_library\simulation\verilog

若顶层仿真文件为VHDL,那么路径为:C:\lscc\diamond\3.9\cae_library\simulation\vhdl

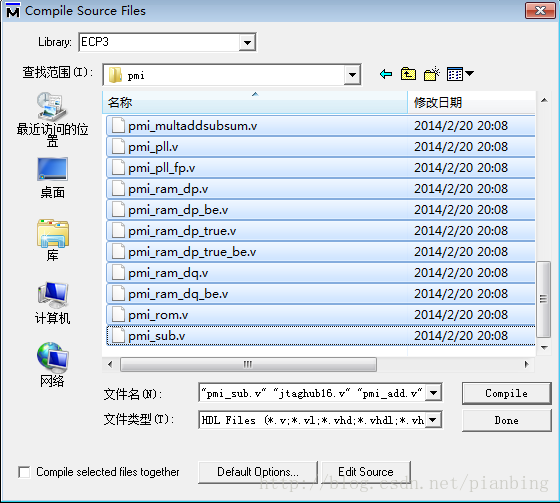

在这两个文件夹下,分别有ecp3和pmi文件。pmi文件夹中的文件,主要为一些ip core的仿真库。

另外,如果选择其他family的device,在编译的时候,最好即编译family仿真库文件,也编译pmi文件。例如如果选择的时machxo2 family device,在编译的时候,既编译上面两个路径下的machxo2,也需要编译pmi。以防止出现不可预测的错误。

step6 . 选择ecp3下的所有文件,点击Compile.

查看modelsim最下方的Transcript信息中,当编译无错后,选择编译pmi中的所有文件

编译完成,在Transcript中没有错误出现后。点击Done,退出Modelsim.

step7 . 打开modelsim.ini文件(推荐使用UE打开),在[Library]部分的最后,[vcom]的上方,会发现有一行:ECP3 = ECP3,修改这一行为:ECP3 = X:\modeltech_10.0c\Lattice\ECP3,其功能为指定仿真库的路径。修改完成后保存退出,并添加modelsim.ini的只读属性,防止错误修改。

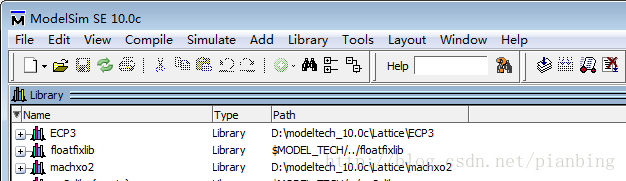

打开modelsim后,查看仿真库的状态,如下状态为正常。

至此,modelsim部分的设置就已经全部完成。接下来需要设置Diamond。

step8 . 在Diamond中选择 Tools > Options > Environment > Directories,在Simulation的Modelsim/QuestaSim选择modelsim的安装路径:X:/modeltech_10.0c/win32

step9 . Diamond中的File List中的Input Files,右键选择Add > New File > Verilog Files.在新建的verilog中编写testbench. 在我的工程中,需要仿真的文件名称为start_up.v,所以新建的testbench文件名称取为start_up_tb.v.

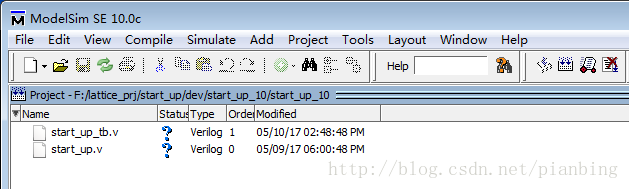

step10 . 在Diamond的菜单栏中选择Tools > Simulation Wizard. 输入仿真工程名以及路径,选择仿真工具Modelsim.在点击Finish后会自动启动modelsim,并跳转到project栏,出现如下画面:

编译全部文件,在这个过程中如果出错,请修改。

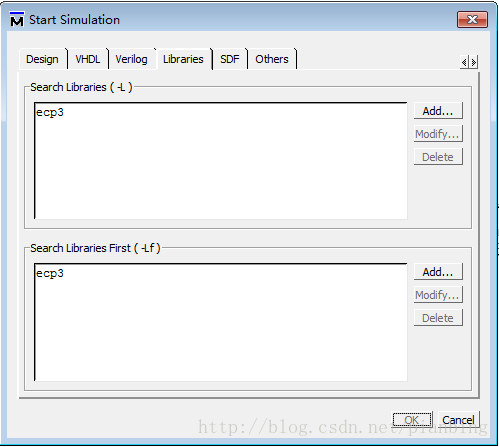

在modelsim的菜单栏中选择Simulate > Start Simulate

在Libraries中选择需要添加的仿真库,这个仿真库必须与所选用的器件是同一Family的,并点击OK

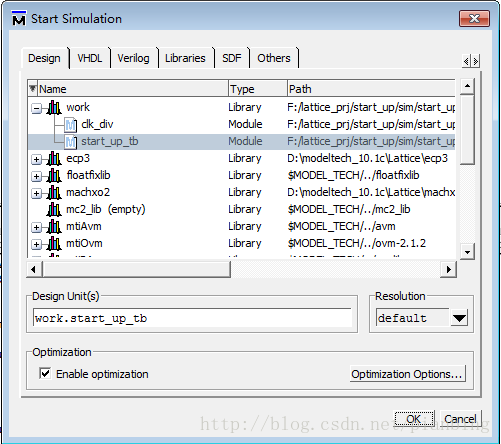

然后再点击Design选项卡,选择work中的start_up_tb.v文件,点击OK,开始仿真。

step11 . 需要查看的信号添加到wave窗口。退出仿真工程的时候,可以在Transcript中输入quit -sim退出。

注意,在编写testbench的时候需要添加一下两段代码:

• GSR GSR_INST(.GSR(1'b1));

• PUR PUR_INST(.PUR(1'b1));

- 1

- 2

这是因为有些LATTICE 的 FIFO_DC IP核这个IP核的子模块中使用了DIAMOND的全局GSR_INST 变量 ,其实还有一个PUR_INST变量。这时由于仿真不具有这个全局变量 我们就在顶层文件的模块中添加上面两段代码。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?