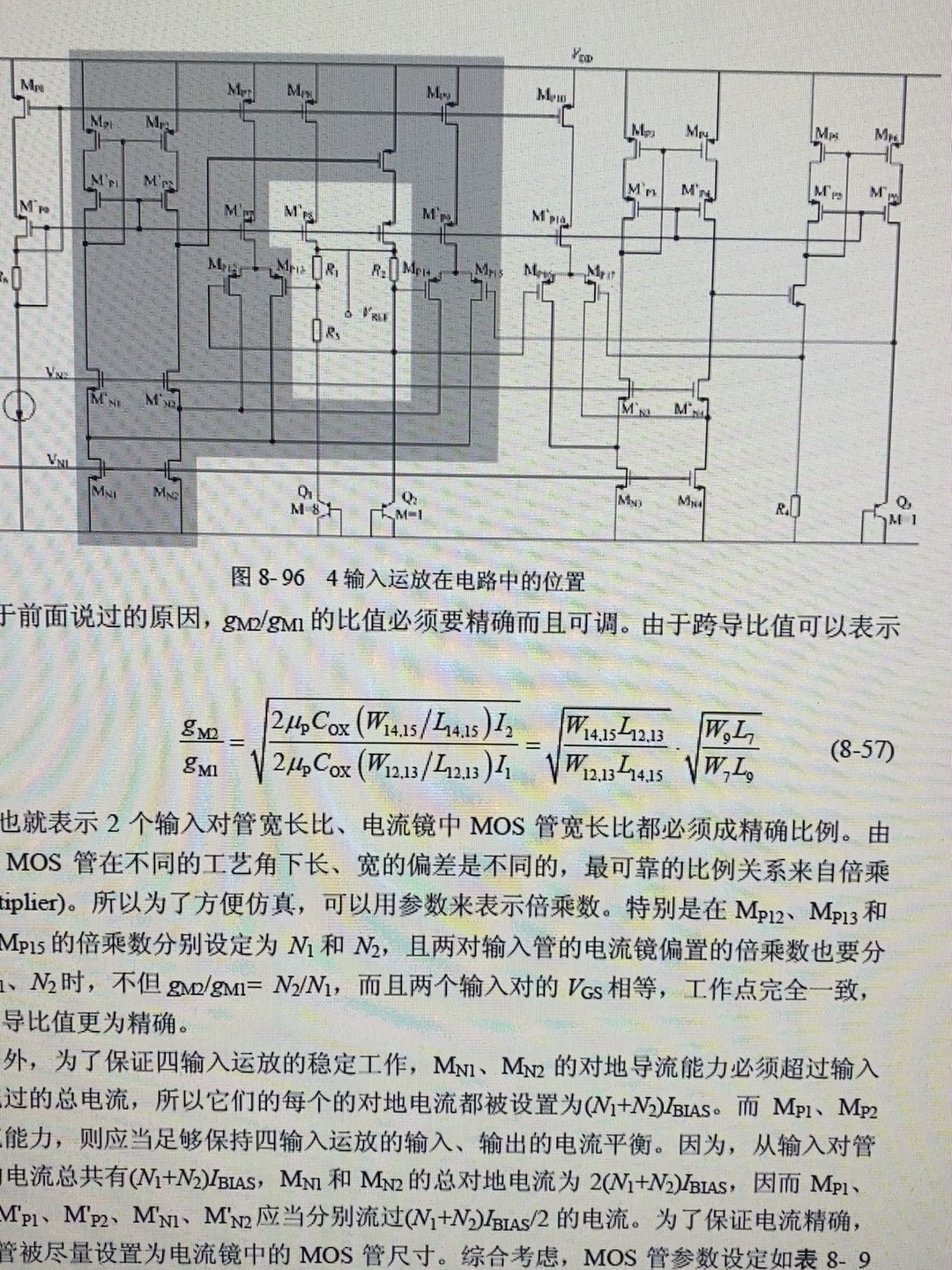

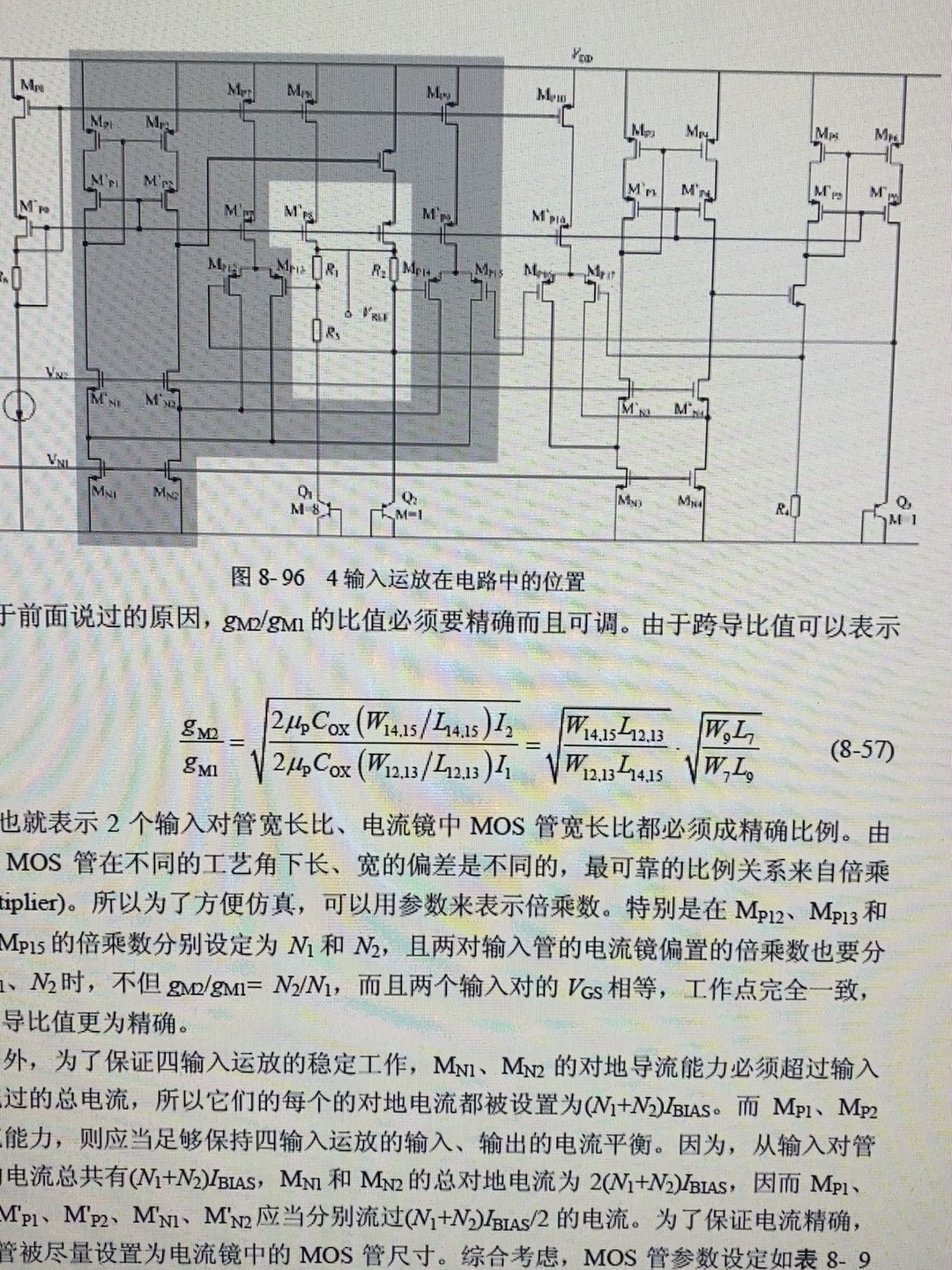

超低温漂,带隙基准,高电源抑制比,低功耗,高阶温度补偿带隙基准,cadence

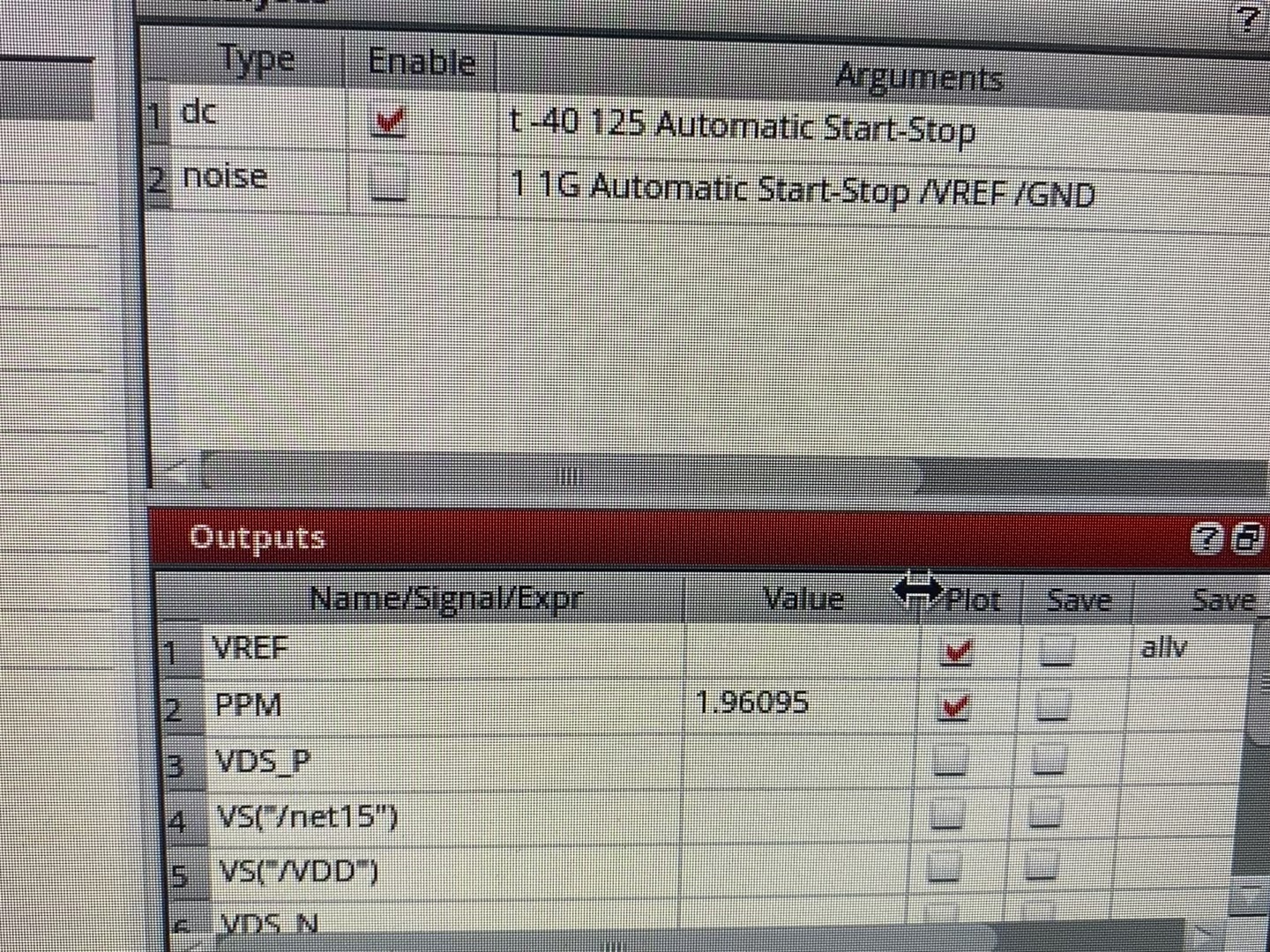

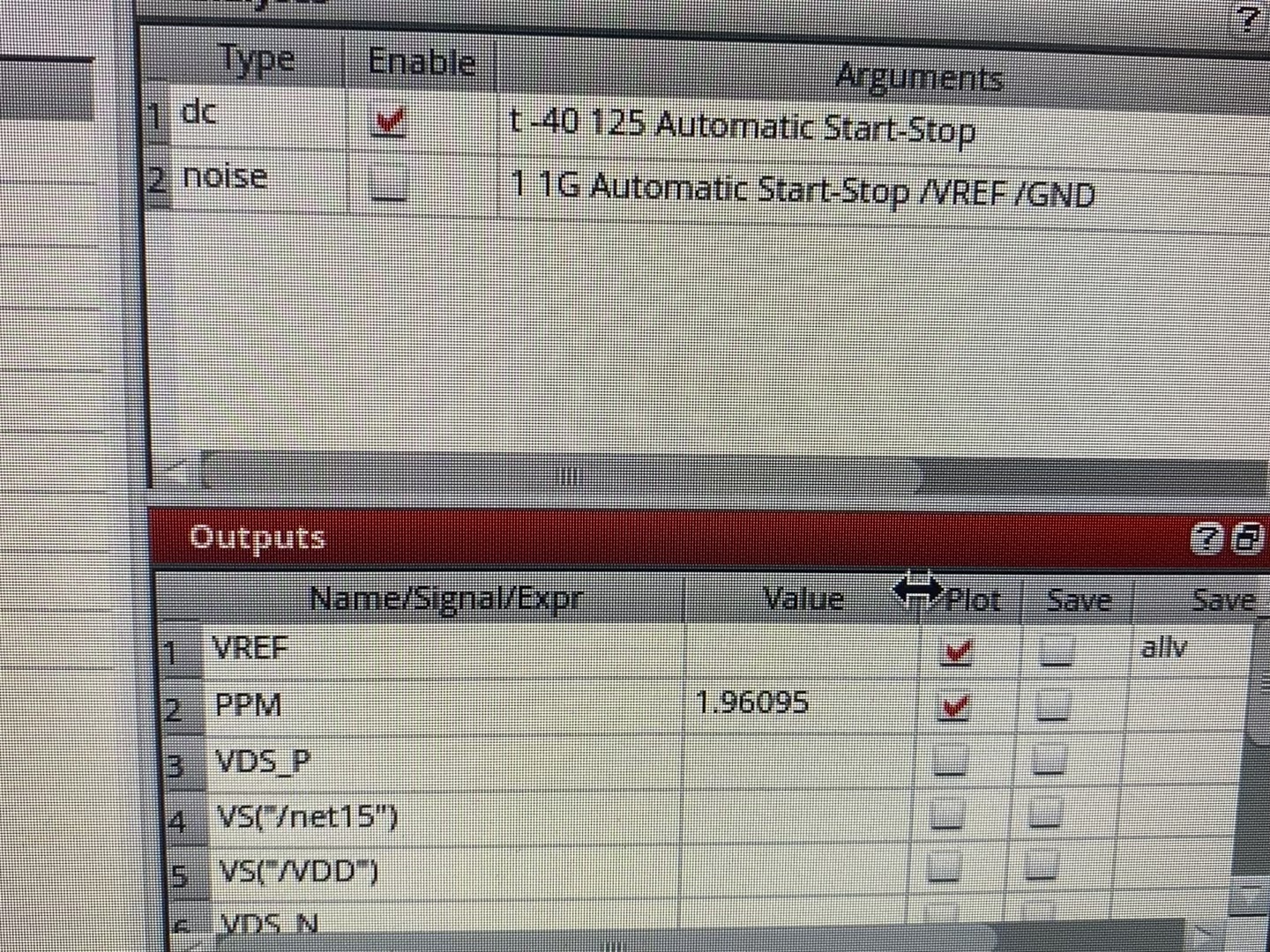

ppm:1.9

psrr:-90dB

电流:14.47uA

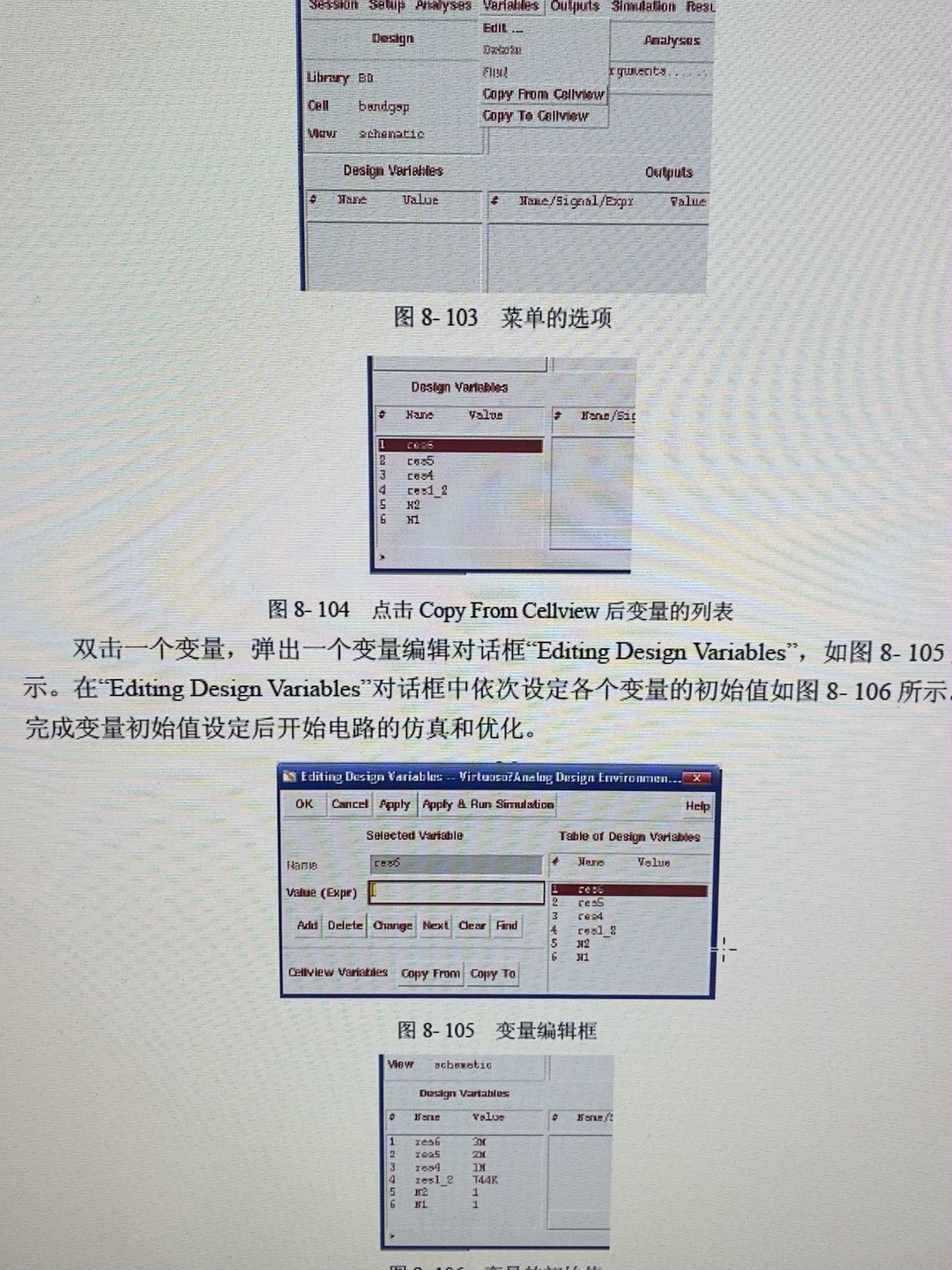

1.带37页设计文档PDF,有推导过程和调试过程,以及仿真设置

2.带工艺库打包,都是61OA格式,可以提供虚拟机和cadence618,包安装调试

3.过程截图和电路截图

关联词:cadence电路设计,带隙基准,bandgap,低温漂,高阶温度补偿

ID:75199711391537726

老王模拟IC

超低温漂,带隙基准,高电源抑制比,低功耗,高阶温度补偿带隙基准,cadence

ppm:1.9

psrr:-90dB

电流:14.47uA

1.带37页设计文档PDF,有推导过程和调试过程,以及仿真设置

2.带工艺库打包,都是61OA格式,可以提供虚拟机和cadence618,包安装调试

3.过程截图和电路截图

关联词:cadence电路设计,带隙基准,bandgap,低温漂,高阶温度补偿

ID:75199711391537726

老王模拟IC

1003

1003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?