由于在最近的项目中需要用到 floating-point IP中的 fix2float功能以及乘法功能,在使用前对其进行基本的仿真测试。

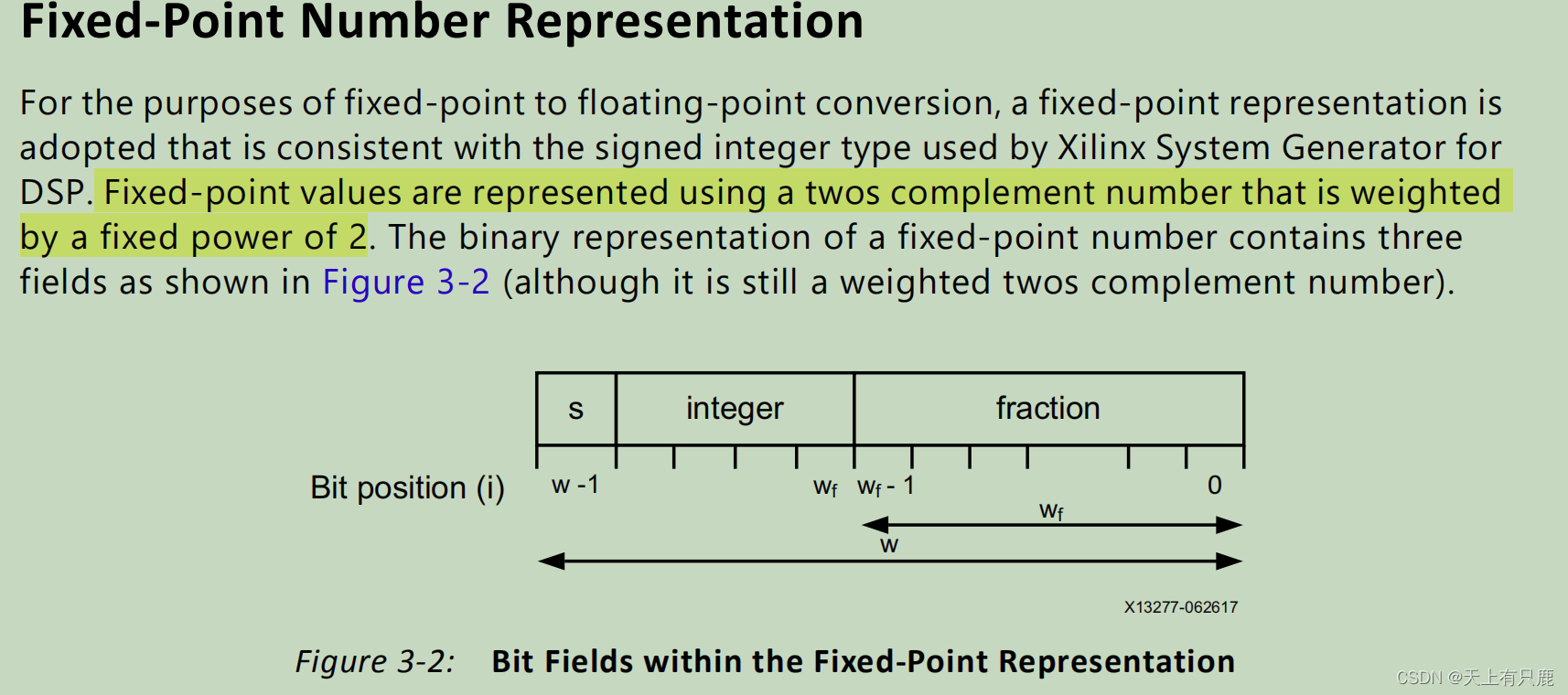

fix2float功能使用前需要知道的(标黄部分:

IP对定点数的格式要求如上图所示,编码类型为:二进制补码

IP核设置:

左侧可以看到输入输出接口的细节,右侧值得注意的是输入输出端口的延时设置(在这里设置为7个时钟延时)

仿真代码如下:

//~ `New testbench

`timescale 1ns / 1ps

module tb_float_point_wrapper;

// float_point_test_wrapper Parameters

parameter PERIOD = 10;

// float_point_test_wrapper Inputs

reg M_AXIS_RESULT_0_tready = 1 ;

reg [15:0] S_AXIS_A_0_tdata = 16'd12 ;

reg S_AXIS_A_0_tvalid = 0 ;

reg aclk_0 = 0 ;

// float_point_test_wrapper Outputs

wire [31:0] M_AXIS_RESULT_0_tdata ;

wire M_AXIS_RESULT_0_tvalid ;

wire S_AXIS_A_0_tready ;

initial

begin

forever #(PERIOD/2) aclk_0=~aclk_0;

end

float_point_test_wrapper u_float_point_test_wrapper (

.M_AXIS_RESULT_0_tready ( M_AXIS_RESULT_0_tready ),

.S_AXIS_A_0_tdata ( S_AXIS_A_0_tdata [15:0] ),

.S_AXIS_A_0_tvalid ( S_AXIS_A_0_tvalid ),

.aclk_0 ( aclk_0 ),

.M_AXIS_RESULT_0_tdata ( M_AXIS_RESULT_0_tdata [31:0] ),

.M_AXIS_RESULT_0_tvalid ( M_AXIS_RESULT_0_tvalid ),

.S_AXIS_A_0_tready ( S_AXIS_A_0_tready )

);

initial

begin

#55

S_AXIS_A_0_tvalid = 1;

end

endmodule

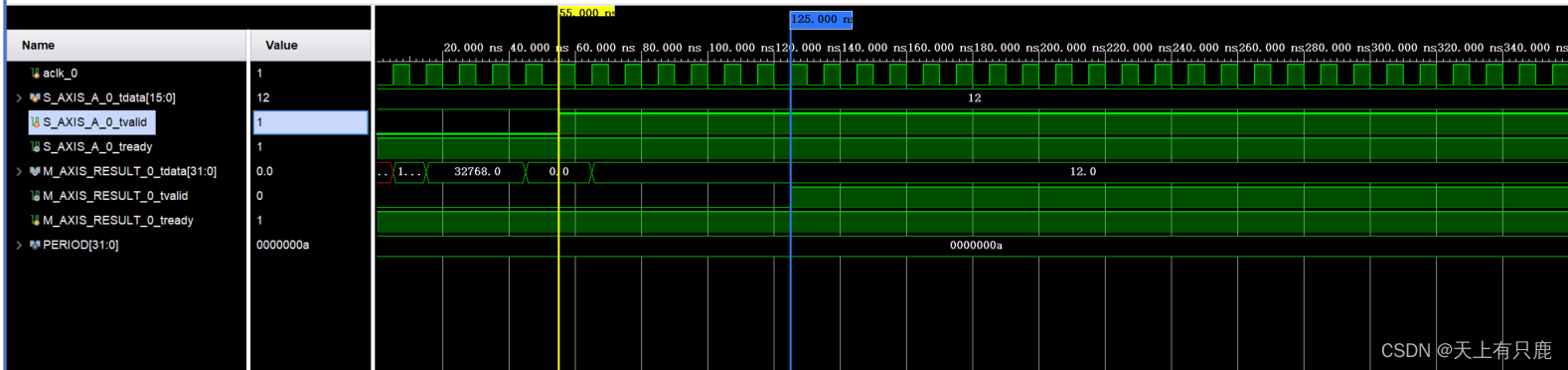

仿真结果如下图所示:

可以看到:数据以及延时均符合预期。同时注意到数据在延时一个周期时就已经准备好了,后续M_AXIS_TVALID的拉高时间更晚是我们人为设置所导致的。

下面仿真其浮点数乘法功能,由于在最后项目中主要运用该功能实现FFT的加窗部分,所以仿真也直接将FFT原始数据拿来用了。

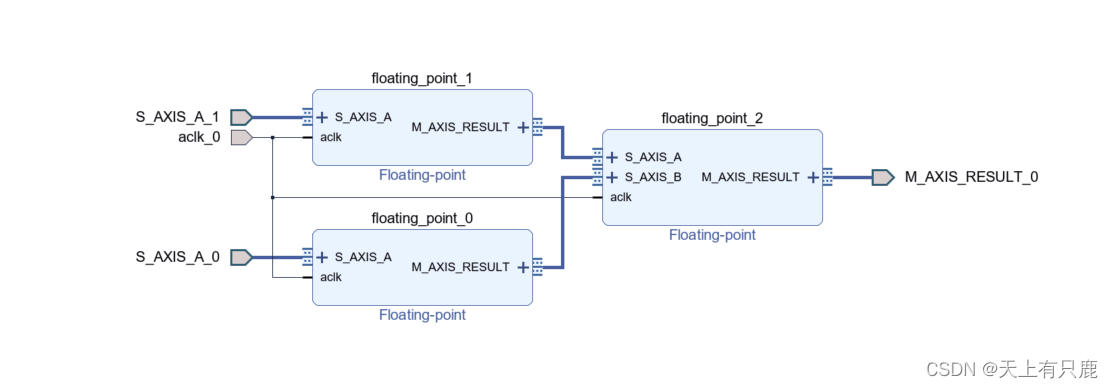

顶层模块如下:

前级为转换部分,后级为浮点数乘法部分,两个输入通道分别同步地输入原始波形数据,窗函数数据,编码类型为二进制补码。

仿真代码如下:

//~ `New testbench

`timescale 1ns / 1ps

module tb_float_point_test_wrapper;

// float_point_test_wrapper Parameters

parameter PERIOD = 10;

reg [15:0] Time_data_I[1023:0];

reg [15:0] win_data_I[1023:0];

// float_point_test_wrapper Inputs

reg M_AXIS_RESULT_0_tready = 1 ;

reg [15:0] S_AXIS_A_0_tdata

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?