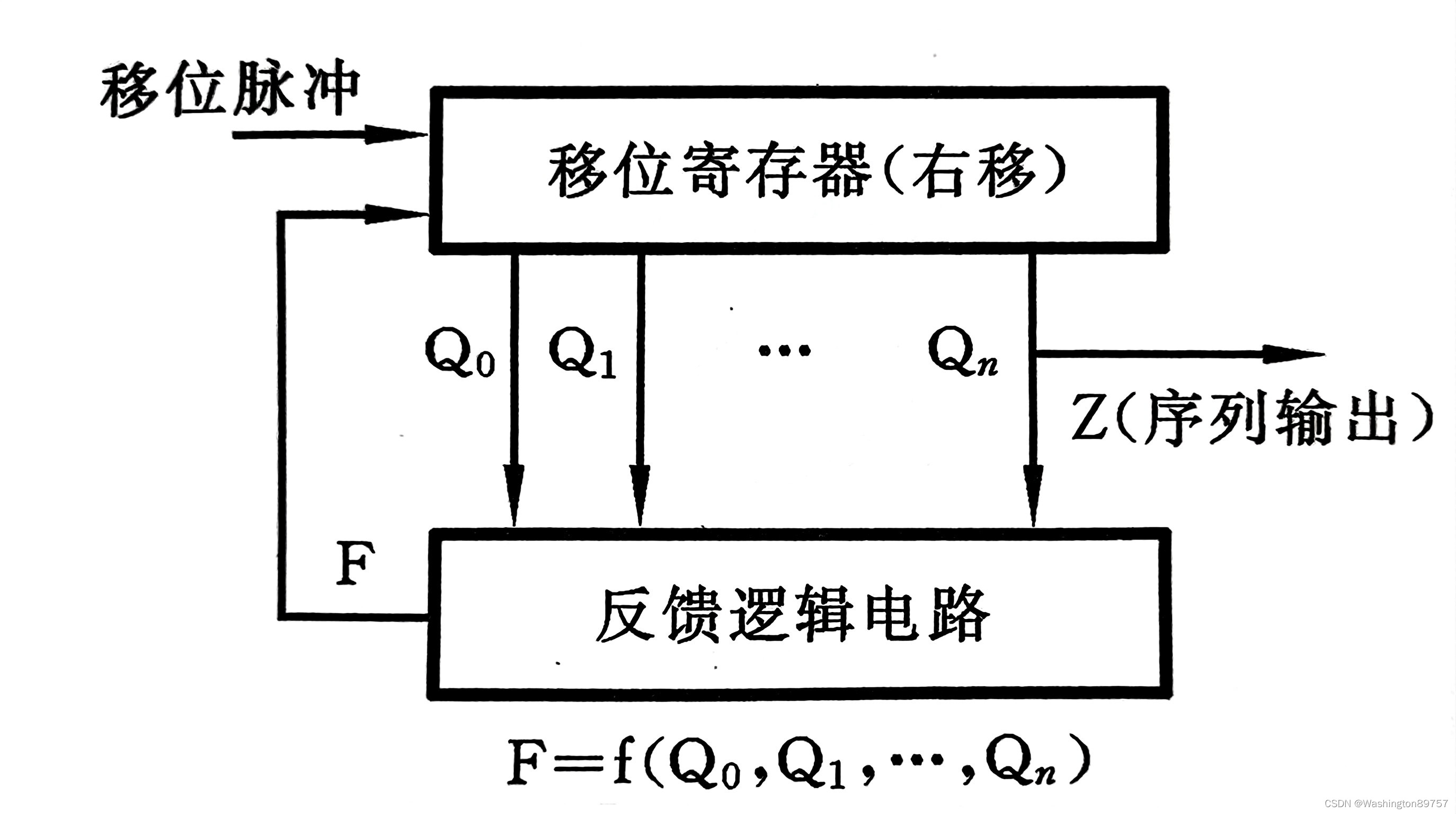

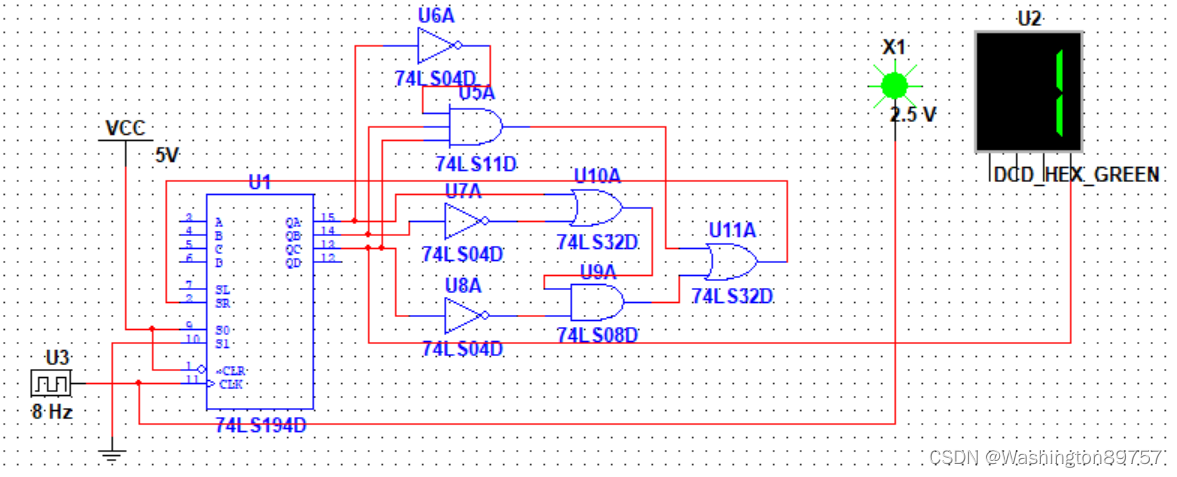

序列信号发生器可由移位寄存器(74194)和反馈逻辑电路构成,如下图所示:

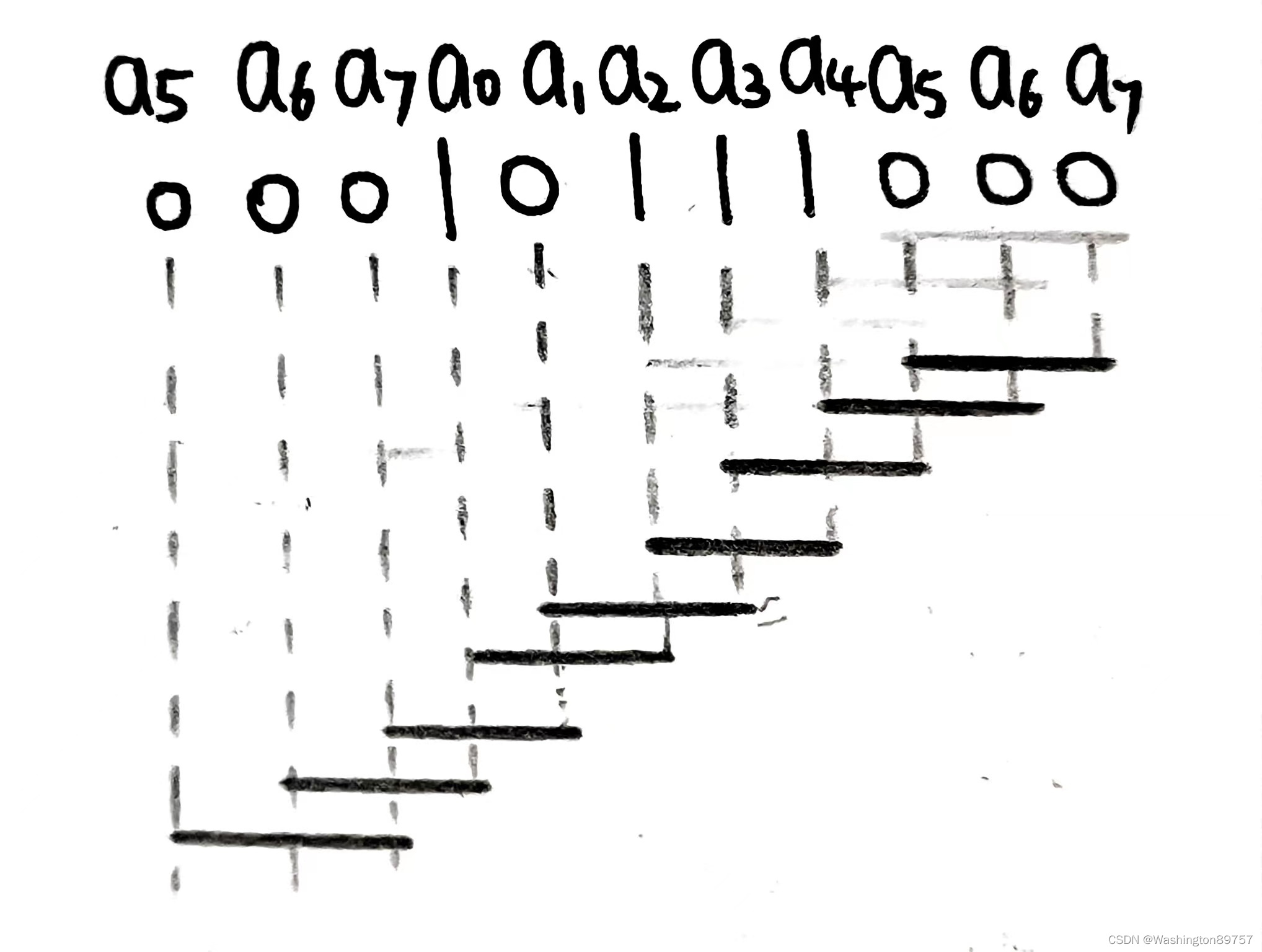

一、列出所要产生的序列(周期为8,最右边信号先输出)与移位寄存器状态的关系

如上图,序列下面的线段所对应的数码表示移位寄存器的状态 。a5 a6 a7 = 000 为寄存器初始状态,从最右端产生输出,由反馈电路形成右移串行输入端的输入。这样,便可在时钟脉冲作用下产生规定的输出序列。

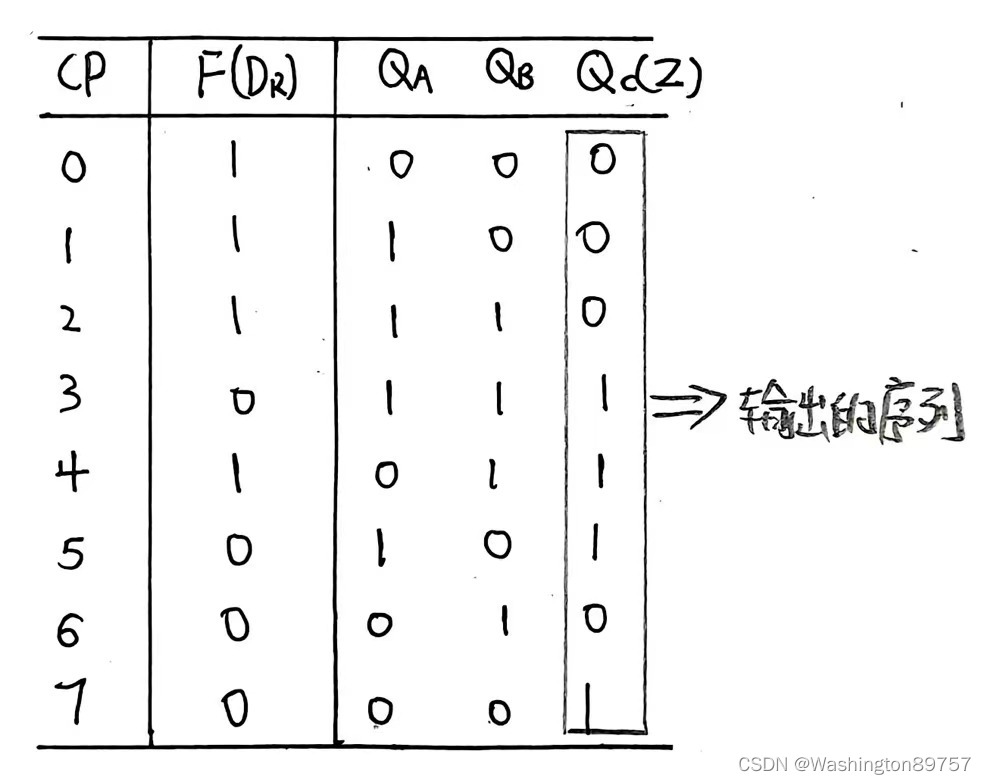

二、作出电路状态变化表

电路在时钟作用下的状态变化过程及右移输入值如下表所示:

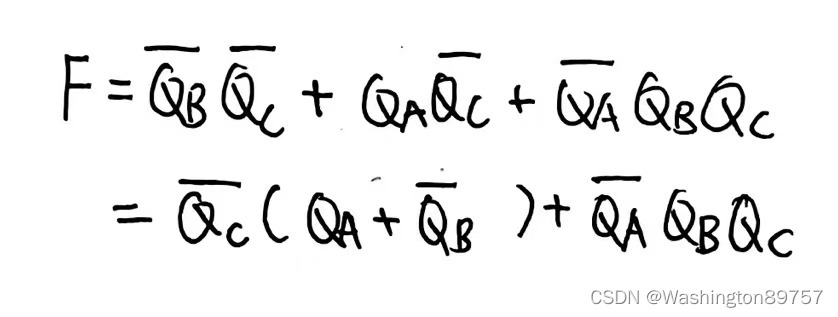

三、求出反馈函数的逻辑表达式

由表可得反馈函数F的逻辑表达式:

四、在Multisim上完成电路

如上图,探针X1与时钟脉冲相连,每亮一次就说明时钟脉冲作用一次(0→1),也代表着输出一个数字。探针右边显示数字0或1,表示输出的数字。这样,探针每亮8次就完成一个周期,然后继续循环下去。

五、总结与反思

本电路总体的设计方法,可以参照教材,“照葫芦画瓢”,可以说并不算太难。但是在模拟软件上连接电路时,出现了诸多问题,导致花费了大量时间和精力。以下是三点经验:

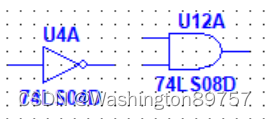

第一,两个元件在连接过程中,看起来是接在一起了,实际上是断开的,如下图所示。

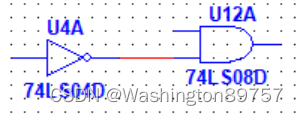

这启示我们,尽量不要直接将两个元件相连,最好是分隔一定距离,再用导线连接,如下图。

第二,电路运行结果与预期不符,且从电路设计中找不出问题时,要学会从电路的每一个部分去排查错误,可运用探针等工具来输出中间结果, 如下图黑色框内的探针。

第三,Multisim中的芯片引脚可能与教材有所不同,不能一味照搬教材。拿74194的输出端举例,教材中从左到右是QD、QC、QB、QA,而Multisim中是QA、QB、QC、QD,两者刚好相反。如果不注意到这一点,实验就难以完成。具体请看我的另一篇文章:https://blog.csdn.net/Washington89757/article/details/130712176

本文如有错漏之处,敬请指正,同时也欢迎交流学习、共同进步。

本文详细介绍了如何使用74194移位寄存器和反馈逻辑电路构建一个序列信号发生器,包括列出序列与移位寄存器状态关系、制作电路状态变化表、求解反馈函数逻辑表达式以及在Multisim软件上的电路实现。在Multisim操作中遇到的问题,如元件实际未连接、排查电路错误和芯片引脚差异等,作者给出了宝贵的解决经验和教训。

本文详细介绍了如何使用74194移位寄存器和反馈逻辑电路构建一个序列信号发生器,包括列出序列与移位寄存器状态关系、制作电路状态变化表、求解反馈函数逻辑表达式以及在Multisim软件上的电路实现。在Multisim操作中遇到的问题,如元件实际未连接、排查电路错误和芯片引脚差异等,作者给出了宝贵的解决经验和教训。

5037

5037

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?