一、缓冲驱动器

缓冲驱动器通常用于隔离、电平转换等应用场景。在使用时,需要关注的点较多,如电平范围、频率范围、延时、控制方式、方向以及输入输出状态。通常,比较容易忽略的地方就是输入输出状态。下面会通过一个实例来介绍。

二、实例分析

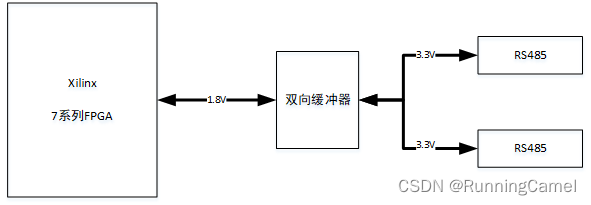

1.硬件结构

主控为Xilinx 7系列FPGA,通过双向缓冲器,连接RS485芯片。如下图示:

2.问题描述

板卡上电后,FPGA未加载位流时,RS485通讯会不通。但是当下载完位流后,RS485能够正常通讯。

3.原因分析

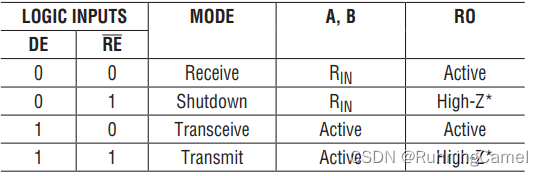

由于下载位流后可以功能正常,因此,排除了芯片、焊接、原理设计上面的问题。因此就定位到RS485工作模式。查阅使用的芯片手册,发现DE为高时,RS485会处于发送状态。由于RS485总线形式存在,此时会将总线挂起。接下来就分析为什么DE会处于高电平。

4.原因定位

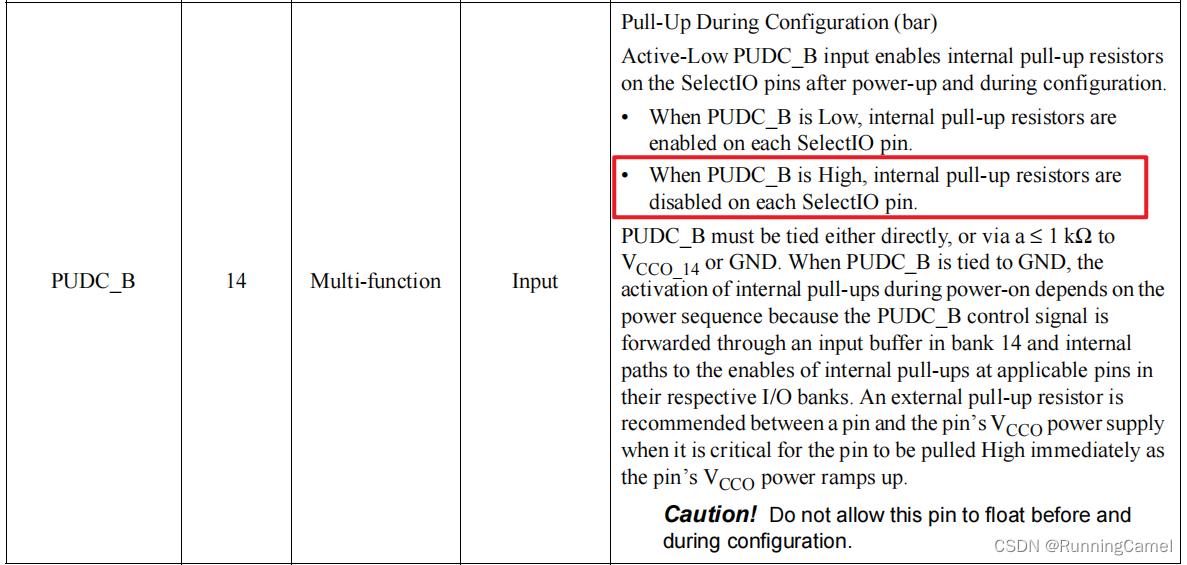

首先主控FPGA上电未加载位流时,IO状态由PUDC_B引脚状态决定。本案例中,PUDC_B引脚是上拉之VCCO_0,因此此时IO状态应为高阻态。理论上,不会引起DE为高。 UG470。

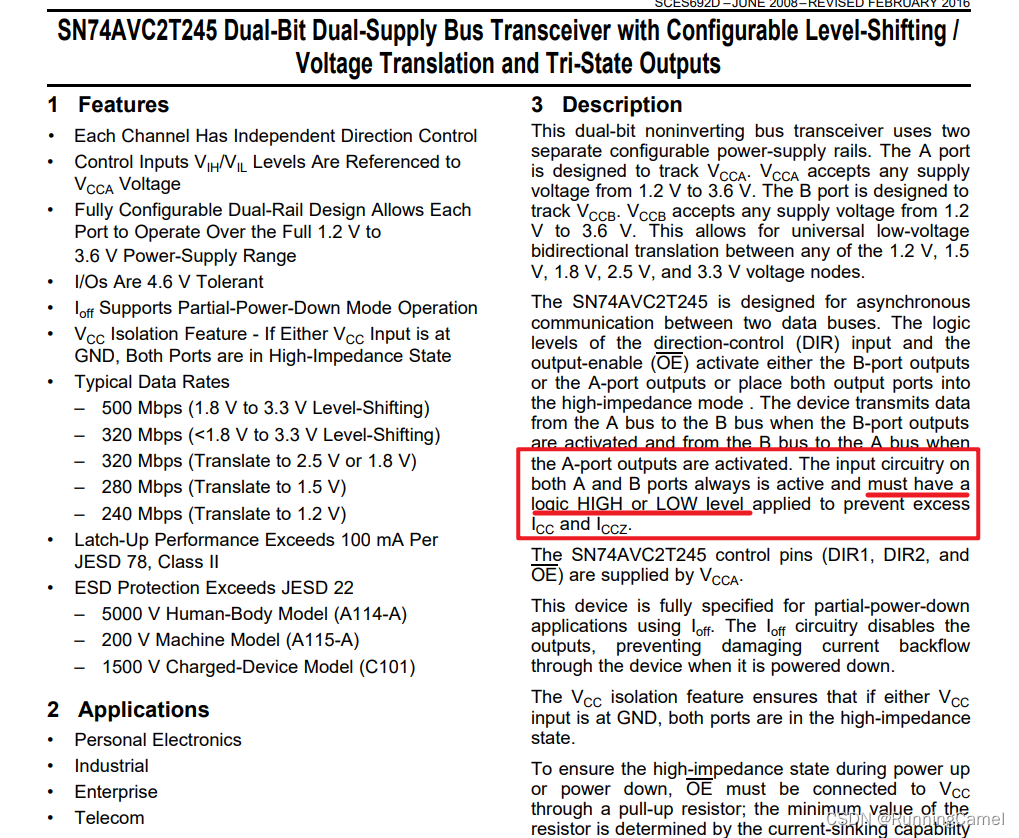

但是,本案例中,经过一级缓冲器进行了电平转换,因此,查阅了缓冲器的特性,发现输入不能为高阻态。因此,定位到是由于缓冲器的输入为高阻态,导致了缓冲器的输出高高电平,从而使得RS485出现挂死现象。

三、结论

在使用缓冲器时,需要特别注意输入悬空状态时输出状态。通常的缓冲器时不推荐输入悬空的,此时需要在输入端上拉、或者下拉,使得输入状态稳定。

不稳定的输入状态,也会是的缓冲器的静态电流出现不稳定的情况,需要重点关注。

E N D ! \color{#4285f4}{\mathbf{E}}\color{#ea4335}{\mathbf{N}}\color{#fbbc05}{\mathbf{D}}\color{#4285f4}{\mathbf{!}} END!

590

590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?