Pcie 3.0 xilinx v7 加Aurora 40g 全部源代码加设计方案以及电路原理图

ID:4920000682647682639

gaoisgod

Pcie 3.0是一种高速、可扩展的计算机接口技术,常被应用于高性能计算、数据中心和网络设备等领域。而Xilinx V7则是一种先进的可编程逻辑芯片,具备强大的计算和处理能力。本文将结合这两项技术,探讨如何在Pcie 3.0接口中加入Aurora 40G协议,以及相关的全部源代码、设计方案和电路原理图。

首先,我们需要了解Pcie 3.0接口的基本原理。Pcie 3.0接口是一种串行接口技术,通过包络传输和差分信号传输来实现高速数据传输。与之前的版本相比,Pcie 3.0接口在传输速率、效率和可靠性等方面都有了显著提升。它支持多通道传输和数据包重组,能够有效地满足高性能计算和数据中心等应用的需求。

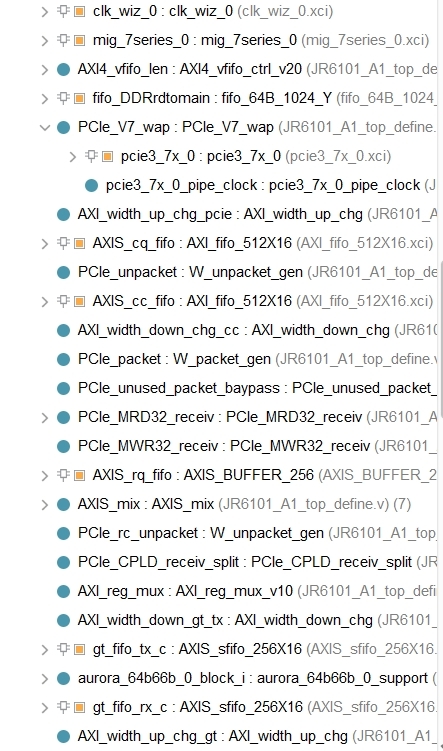

接下来,我们将Pcie 3.0接口与Xilinx V7相结合,进一步提升系统的计算和处理能力。Xilinx V7是一种基于FPGA的可编程逻辑芯片,具备高度灵活性和可扩展性。它采用了先进的硬件描述语言进行编程,可以根据具体需求自定义各种计算和处理功能。通过将Xilinx V7与Pcie 3.0接口相结合,我们可以实现高速数据传输和高性能计算的完美融合。

在将Pcie 3.0接口与Xilinx V7相结合的过程中,引入Aurora 40G协议可以进一步提升系统的通信能力。Aurora 40G是一种高速串行通信协议,支持数据传输速率高达40Gbps。它具备低延迟、高可靠性和高带宽等特点,适用于高性能计算和数据中心等领域。通过将Aurora 40G协议加入到Pcie 3.0接口中,我们可以实现高速数据传输和可靠通信的双重优势。

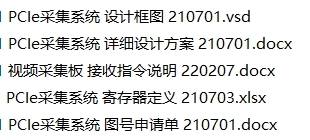

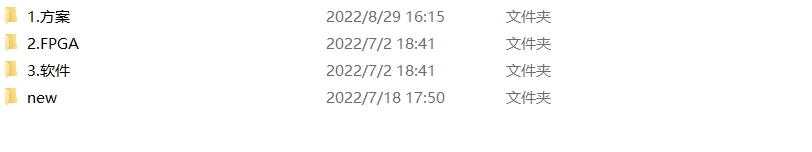

为了实现Pcie 3.0接口与Xilinx V7的整合,我们需要依据系统需求进行设计方案的制定。设计方案应包括硬件设计和软件设计两个方面。在硬件设计方面,我们需要根据具体的接口规范和信号需求,设计适配器电路和接口电路等硬件模块。同时,还需要制定电路原理图,确保硬件设计的准确性和可靠性。在软件设计方面,我们需要根据Xilinx V7的编程规范,进行逻辑设计和软件开发。通过编写相关的源代码,实现计算和处理功能的定制化。

综上所述,将Pcie 3.0接口、Xilinx V7和Aurora 40G协议相结合,可以实现高速数据传输和高性能计算的双重优势。通过对硬件设计方案和软件开发的深入研究,我们可以实现系统的定制化需求,提升系统的计算和处理能力。希望本文的内容对读者在Pcie 3.0接口和Xilinx V7的应用中有所帮助,并引发更多关于高性能计算和数据中心的讨论和研究。

相关的代码,程序地址如下:http://fansik.cn/682647682639.html

454

454

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?