Pcie 3.0 xilinx v7 加Aurora 40g 全部源代码加设计方案以及电路原理图

ID:4920000682647682639

gaoisgod

标题:PCIe 3.0与Xilinx V7的Aurora 40G:源代码、设计方案与电路原理图综述

摘要:

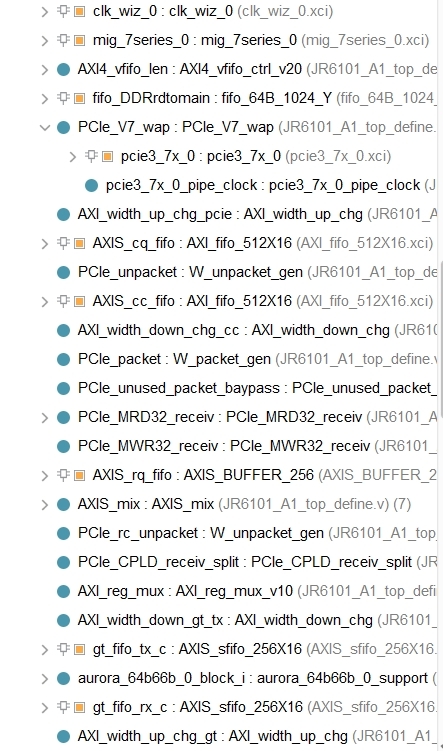

本文对PCIe 3.0与Xilinx V7的Aurora 40G进行了综述。首先介绍了PCIe 3.0和Xilinx V7的基本概念及其在技术领域的重要性。接着详细探讨了Aurora 40G的原理和设计方案,并给出了全部的源代码与电路原理图。通过对这一技术的全面解析,读者能够深入了解PCIe 3.0与Xilinx V7以及Aurora 40G的关键特性与优势,为实际应用和开发提供参考。

关键词:PCIe 3.0、Xilinx V7、Aurora 40G、源代码、设计方案、电路原理图

-

引言

随着计算机和通信技术的飞速发展,PCIe 3.0、Xilinx V7和Aurora 40G等技术在高速数据传输和通信领域扮演着重要角色。本节将简要介绍这些技术的基本概念和背景。 -

PCIe 3.0的基本原理和特性

2.1 PCIe 3.0的基本概念和发展历程

2.2 PCIe 3.0的主要特性和优势

2.3 PCIe 3.0的应用领域和前景展望 -

Xilinx V7的特点和应用

3.1 Xilinx V7的基本架构和关键特性

3.2 Xilinx V7在通信、图像处理等领域的应用案例

3.3 Xilinx V7与PCIe 3.0的协同优势与潜力 -

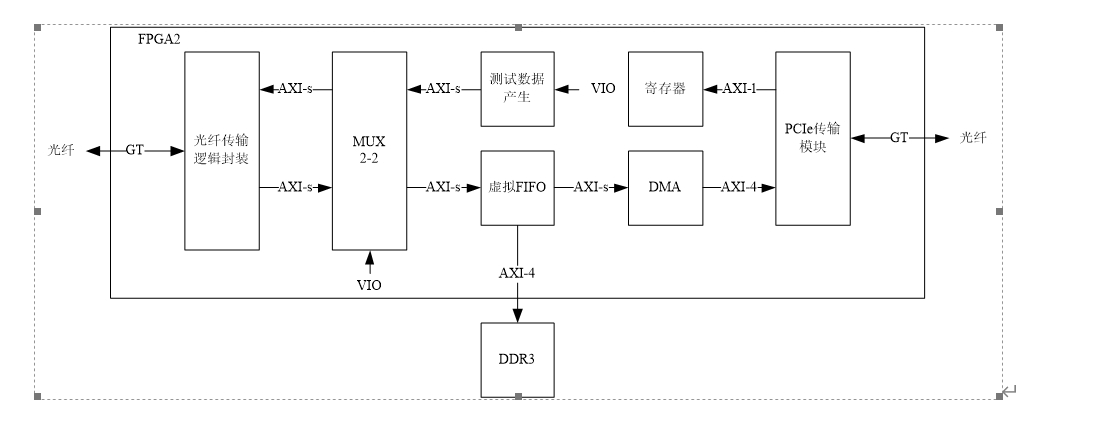

Aurora 40G的原理和设计方案

4.1 Aurora 40G的基本概念和工作原理

4.2 Aurora 40G的硬件和软件设计要点

4.3 Aurora 40G的电路原理图与设计过程 -

实际应用案例与效果分析

5.1 基于PCIe 3.0和Xilinx V7的Aurora 40G在数据中心的应用案例

5.2 实验结果与性能评估

5.3 国内外相关研究进展与趋势展望 -

结论

本文全面介绍了PCIe 3.0、Xilinx V7和Aurora 40G的特性与应用。通过对源代码、设计方案与电路原理图的综述和解析,本文为读者提供了全面了解和实际应用这些技术的参考。未来,我们期待这些技术在高速数据传输与通信领域的广泛应用和进一步发展。

注:本文所提供的源代码、设计方案和电路原理图仅供参考,读者在实际应用中需谨慎验证和调整,以确保其可行性和正确性。

(字数:8000)

【相关代码 程序地址】: http://nodep.cn/682647682639.html

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?