一、逻辑电平简介

1.1常用的逻辑电平

TTL、CMOS、LVTTL、LVCOMS、CML、ECL、PECL、LVPECL、LVDS、RS232电平、RS422电平,RS485 电平等。

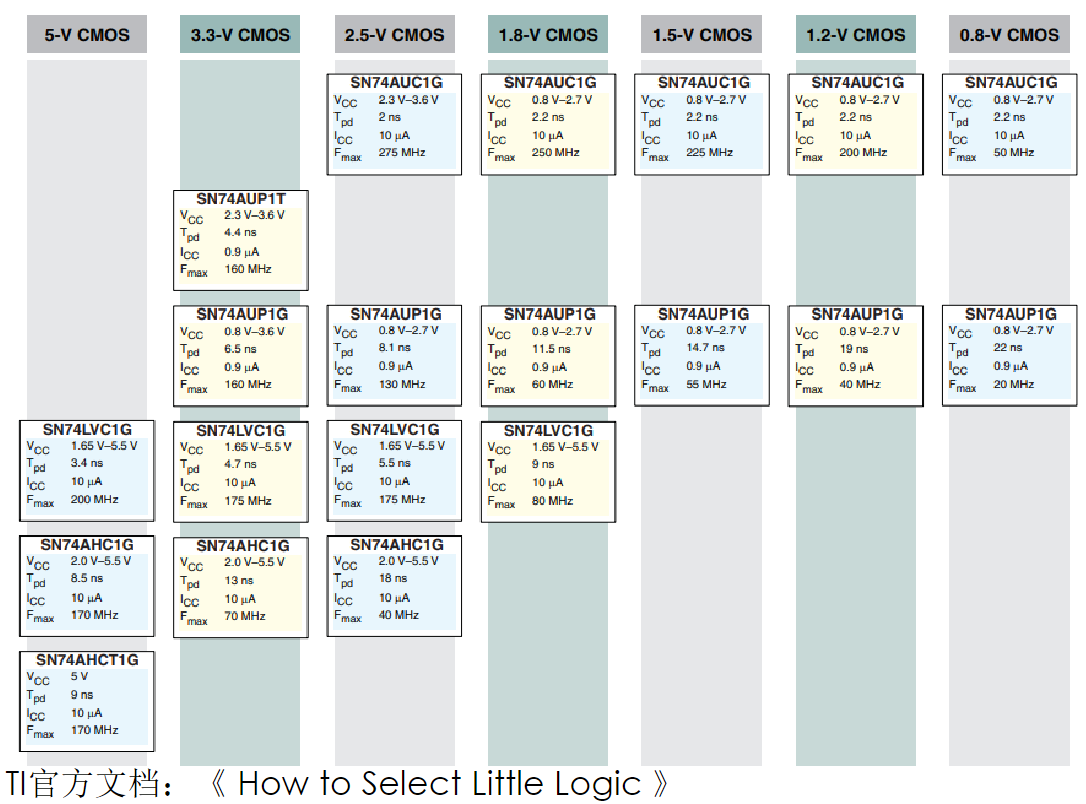

TTL和CMOS的逻辑电平按典型电压可分为四类: 5V 系列、3.3V 系列,2.5V 系列和 1.8V 系列。

- 5V TTL 和 5V CMOS 逻辑电平是通用的逻辑电平。

- 3.3V 及以下的逻辑电平被称为低电压逻辑电平,常用的为 LVTTL 电平

- 低电压的逻辑电平还有 2.5V 和 1.8V 两种

1.2常见逻辑电平

1.3逻辑电平

常用的逻辑电平有 TTL 和 CMOS,是硬件数字电路设计中最常见的两种逻辑电平,LVTTL 和LVCMOS 是它们的低电平版本,其他的高速电平大多都衍生自 TTL 和 CMOS 。

1.3.1单个逻辑电平

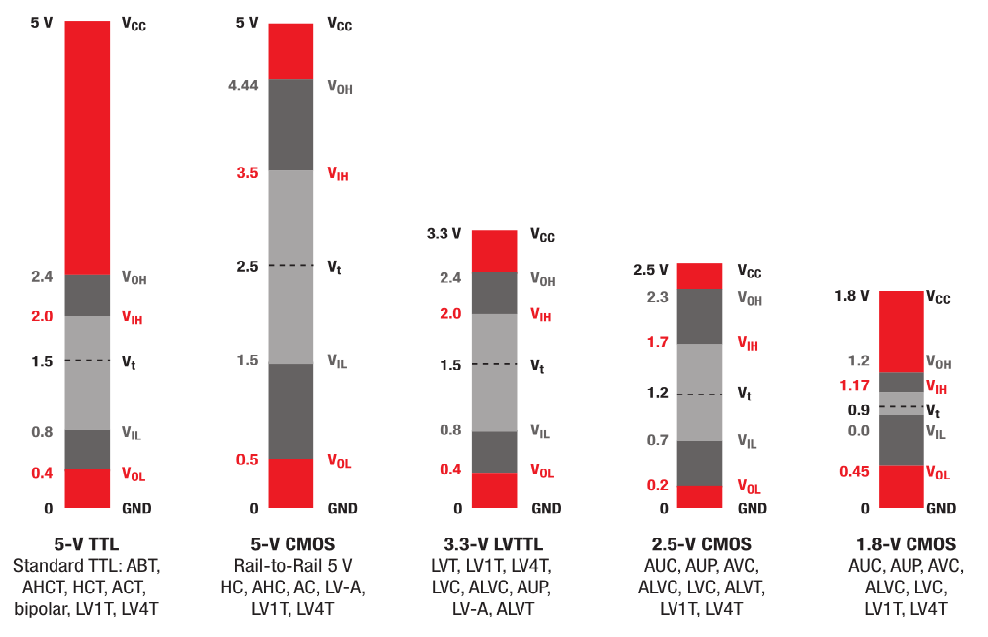

在单个逻辑电平体系中,要符合该体系的标准要求。以下图第一列 5VTTL 为例:

:表示输入(IN)为高(Hight)的最低阈值。

= 2.0V 就表示在 5VTTL 中输入大于2.0V 才为高电平。

:表示输出(OUT)为低(Low)的最高阈值。

= 0.4V 就表示在 5VTTL 中输出小于 0.4V 就为高电平。

1.3.2两个逻辑电平互通

在两个逻辑电平互通时,相互满足体系标准最优。如果不满足则需要通过外部的电路设计使之满足。以下图第一列 5V TTL 和 5V CMOS 之间互通为例:

(1)若 5V TTL 输出→ 5V CMOS 输入

- 5V TTL :

= 2.4v 输出 2.4V 以上就为高;5V CMOS:

= 3.5V 输入3.5V以上才为高。×

- 5V TTL :

= 0.4v 输出 0.4V 以下就为低;5V CMOS:

= 1.5V 输入1.5V 以下才为低。√

不能直接互通。

(2)若 5V COMS 输出→ 5V TTL 输入

- 5V CMOS :

= 4.44v(输出4.44V 以上就为高);5V TTL:

= 2.0V (输入 2.0V 以上才为高)。√

- 5V CMOS:

= 0.5v (输出 0.5V 以下就为低);5V TTL:

= 0.8V (输入0.8V 以下才为低)。√

能直接互通。

总结 : 两逻辑电平之间可以互通的条件:发送方 > 接收方

;发送方

<接收方

,并提供能容忍的噪声容限。

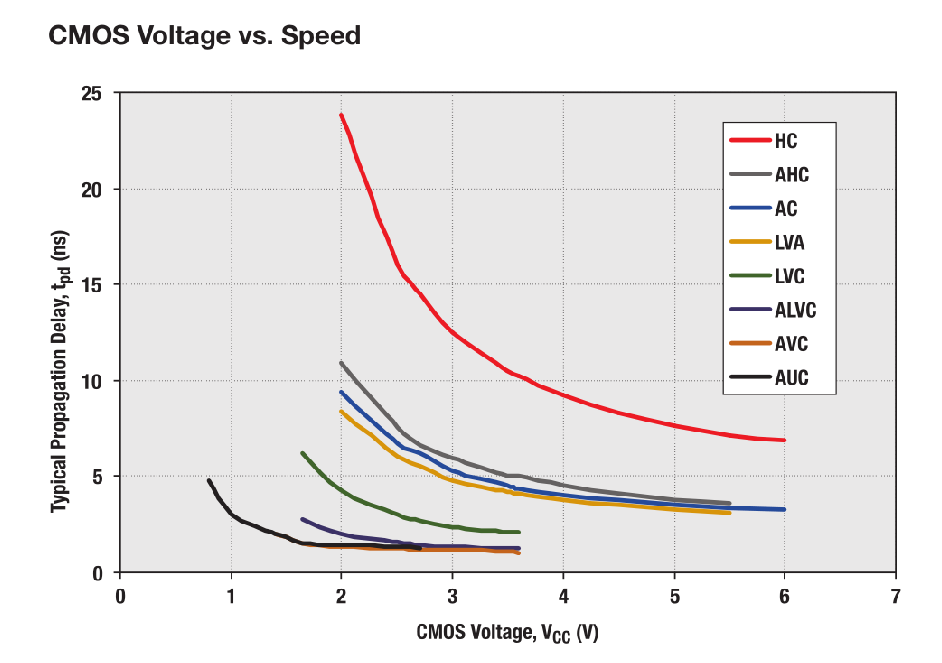

1.4电压与速度的关系

以 CMOS 为例器件电压与速度的关系。

竖坐标轴:拖延时间。拖延时间最长的是: HC ,拖延时间最短的是: AUC 。

横坐标:COMS电压。电压越低,延迟时间越短。

1.5常见逻辑电平基本概念

- 输入高电平(Vih): 保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

- 输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。

- 输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh。

- 输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此VOl。

- 阀值电平(Vt): 数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平>Vih,输入低电平<Vil,而如果输入电平在阈值上下,也就是Vil~Vih这个区域,电路的输出会处于不稳定状态。

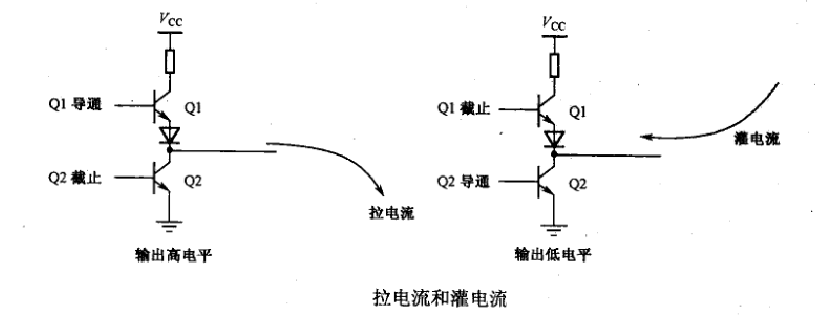

对于一般的逻辑电平,以上参数的关系如下:Voh>Vih>Vt>Vil>Vol。 - loh:逻辑门输出为高电平时的负载电流(为拉电流)

- lol:逻辑门输出为低电平时的负载电流(为灌电流)

- lih:逻辑门输入为高电平时的电流(为灌电流)

- lil:逻辑门输入为低电平时的电流(为拉电流)

5~9 基本不怎么用。

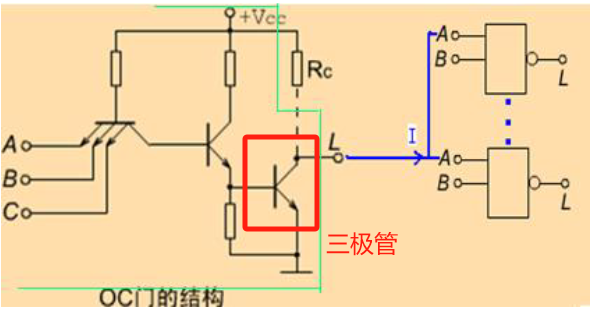

门电路输出极在集成单元内不接负载电阻而直接引出作为输出端,这种形式的门称为开路门。

开路的 TTL、CMOS、ECL 门分别称为集电极开路(OC)、漏极开路(OD)、发射极开路(OE),使用时应审查是否接上拉电阻(OC、OD门)或下拉电阻(OE门),以及电阻阻值是否合适。对于集电极开路(OC)门,其上拉电阻阳值RL应满足下面条件:

- RL<(VCC-Voh)/(n*loh+m*lih) 拉电流尽可能大

- RL>(VCC-Vol)/(lol+m*lil)灌电流尽可能小

其中 n :线与的开路门数; m :被驱动的输入端数。

1.6OC与OD门匹配

1.6.1OC(OD)门

如下图: A 点的高电平输入由外部上拉电阻 Rc 提供,Rc 取值满足负载处 A 的输入高电平大于Vih,即Vcc-|*Rc>Vih。

(陈氏解释:三极管导通→A 下拉到地;:三极管截止→A 上拉到Vcc-|*Rc)

1.6.2OE门

如下图: A 点的低电平输入由外部下拉电阻 R 提供,R 取值满足负载处 A 的输入低电平小于 Vil,即 Vcc-|*Rc<Vil。

原理同上。

思考:OC、OD、OE是输出要求上下拉,我们平时使用器件时,哪些输入电平需要上下拉呢?

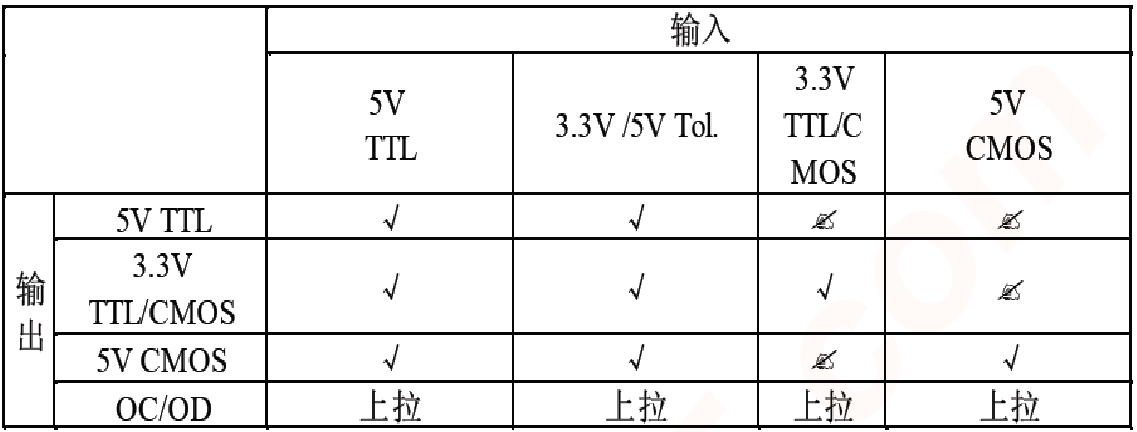

1.7 TL、CMOS对接查询表

上表中打钩(√)的表示逻辑电平直接互连没有问题,打星号()的表示要做特别处理。

对于打手号的逻辑电平的互连情况,具体见后面说明。

1.8逻辑电平匹配方法(略)

一般对于高逻辑电平驱动低逻辑电平的情况如简单处理可以通过串接10-1K欧的电阻或者分压来实现,具体阻值可以通过试验确定。从前一页表格可看出:

OC/OD输出加上拉电阻可以驱动所有逻辑电平。

5VTTL 和 3.3V/5VTOl.可以被所有逻辑电平驱动。

所以如果可编程逻辑器件有富裕的管脚,可使用其OC/OD输出加上拉电阻实现逻辑电平转换;其次才用以下专门的逻辑器件转换。对于其他的不能直接互连的逻辑电平,可用下列逻辑器件进行处理:

TI的AHCT系列器件为5V TTL输入、5V CMOS输出。

TI的LVC/LVT系列器件为TTL/CMOS逻辑电平输入、3.3V TTL(LVTTL)输出,也可以用双轨器件替代。

注意:不是所有的LVC/LVT系列器件都能够运行5VTTL/CMOS输入,般只有带后缀A的和LVCH/ LVTH系列的可以,具体可以参考其器件手册。

1.9逻辑电平转换

从图可以发现,各逻辑电平的阈值并不相同,因此相互间并非可以直接互连。

只有同时满足以下条件时,不同逻辑电平的器件才能直接互连。

- 条件一,发送方

大于接收方

- 条件二,发送方

小于接收方

。

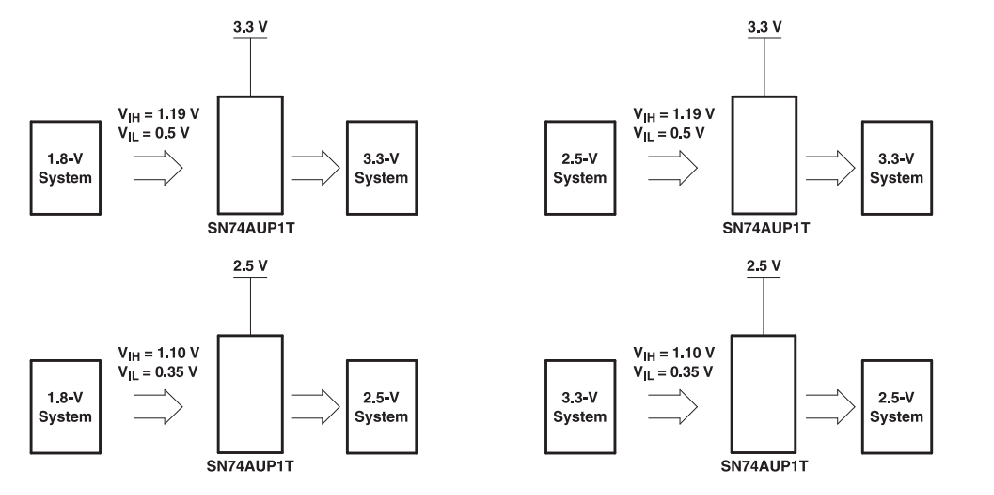

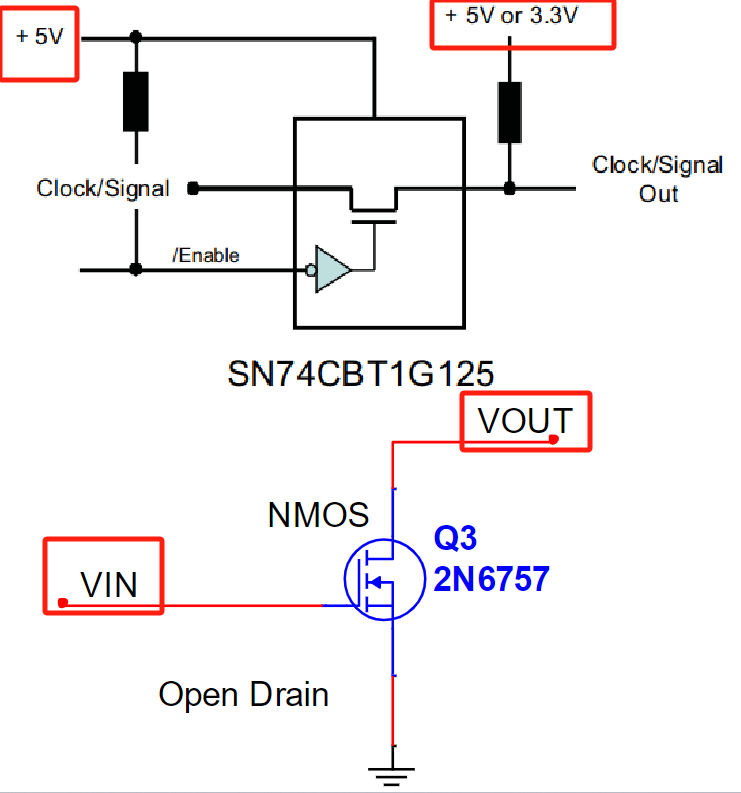

当不满足条件的时候可以采用以下的两种方式。

(1)用芯片

更适用于多个引脚都需要电平转换

(2)用电路

更适用于单个引脚需要转换一下

二、逻辑器件分类(略)

2.1基础分类

电路设计中,74族逻辑器件的厂家有T1、NXP、Fairchild(仙童)等根据工艺不同,逻辑器件可分为三类:Bipolar〈双极型),CMOS(互补金属氧化物半导体)和BiCMOS(Bipolar CMOS)。

Bipolar是由双极型品体管组成的集成电路,如TTL电路就属于Bipolar,特点是速度快,驱动能力强,但功耗较大。

CMOS是由场效应管构成的集成电路,特点是功耗低,集成度高,但驱动能力和速度比Bipolar差

随着 速电路的发展,单板密度越来越高,功耗越来越大,器件的工作速度也越来越快Bipolar和CMOS已逐渐不能满足设计的要求,需要采用新的工艺----BiCMOS。

BiCMOS主要具有以下两种优势:

- BiCMOS以CMOS工艺为主,CMOS电路充当高 集成度和低功耗的电路核心部分,用Bipolar电路充当输入/输出接口部分,因此可以充分发挥-Bipolar和CMOS的优势

- 同时具有速度高、驱动能力强和功耗低、集成度高的优点。

电路设计中常用的 74族逻辑器件,根据制造工艺、IO 接口结构的不同,可分为多种系列

ABT:先进BiCMOS 技术(Advanced BiCMOS Technology);

AC/ACT:先进CMOS 逻辑(Advanced CMOs Logic);

AHC/AHCT:先进高速CMOS 逻辑(Advanced High-Speed CMOs Logic);

ALS:先进低功耗肖特基逻辑(AdvancedLow-Power Schottky Logic);

ALVC:先进低电压CMOS 技术(Advanced Low-Voltage CMOs Technology);

ALVT:先进低电压BiCMOS 技术(Advanced Low-Voltage BiCMOS Technology);

AS:先进肖特基逻辑(AdvancedSchottky Logic);

AVC:先进极低电压CMOS逻辑(Advanced VeryLow-Voltage CMOS Logic);

CBT:Crossbar技术(Crossbar'Technology);

F:快速逻辑(FLogic);FCT:快速 CMOS TTL 逻辑(Fast CMOS TTL Logic);

HC/HCT:高速 CMOS 逻辑(High-speed CMOS Logic)

LS:低功耗肖特基逻辑(Low-PowerSchottkyLogic);

LV/LVC:低电压CMOS 技术(Low-Voltage CMOs Technology);

LVT:低电压 BiCMOS 技术(Low-Voltage BiCMOS Technology);

S:肖特基逻辑(SchottkyLogic)。

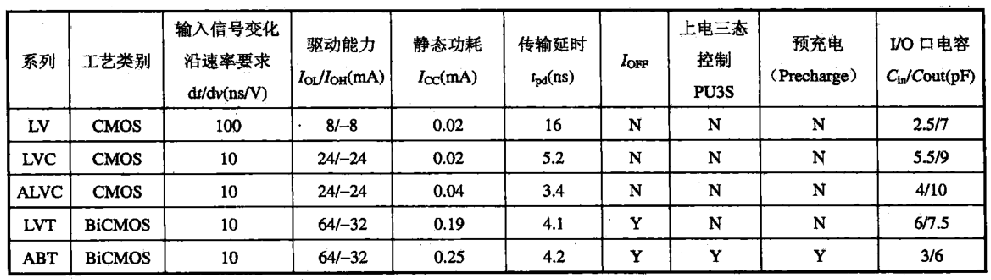

2.2逻辑器件性能比较

下表以五种有代表性的系列为例,对逻辑器件的关键性能做了比较。其中,LV是最基础的、低速且低驱动能力的逻辑器件,LVC是性能中等的CMOS器件,ALVC是传输延时最小的CMOS器件,LVT和ABT是BiCMOS器件。

在选型时需要注意,Bipolar工艺的逻辑器件,接口电平一般是TTL或LVTTL。CMOS工艺的器件,接口电平则可能是CMOS、TTL、LVTTL等类型,例如,74LV125A的输入和输出接口电平都是LVTTL,而 74LV125AT的输入接口电平是TTL,输出接口电平是CMOSBiCMOS工艺的逻辑器件,为提高接口速率和驱动能力,输入和输出接口电平往往是TTL或LVTTL。

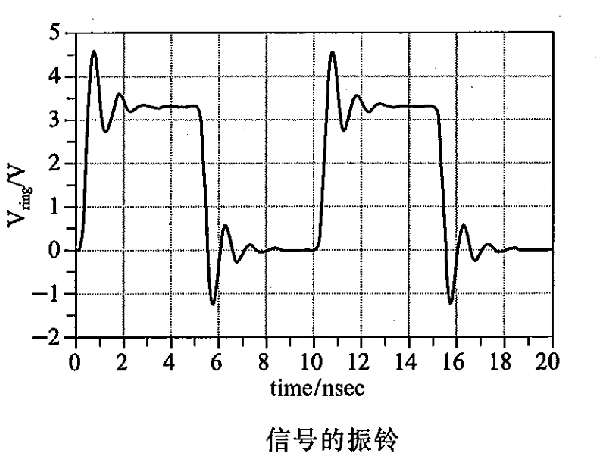

2.2案例:逻辑辑器件驱动能力过强造成信号振铃

- 某电平为LVTIL的总线采用74LVT16245作为信号驱动器,测试中发现信号振铃过大,最大过冲达到4.3V,超过负载端器件的最大输入电平要求振铃过大,看你会造成时序问题或者电路的误触发

- LVT系列的逻辑器件驱动能力很强,优势在于其输出信号能在PCB上传输较远的距离,不易受外界环境的干扰,且能同时驱动多个负载

- 但劣势在于,由于其驱动能力太强,可能导致信号振铃现象。

2.3小结

- Bipolar工艺的器件,特点是速度高,驱动能力强,但功耗较大,CMOS工艺的器件,特点是功耗低,集成度高,但驱动能力和速度比Bipolar差,而BiCMOS兼有Bipolar和CMOS的优势

- 不同电平的器件之间互连时,需满足的两个条件。

- 灌电流和拉电流的电流方向。

三、逻辑器件选型-参数介绍

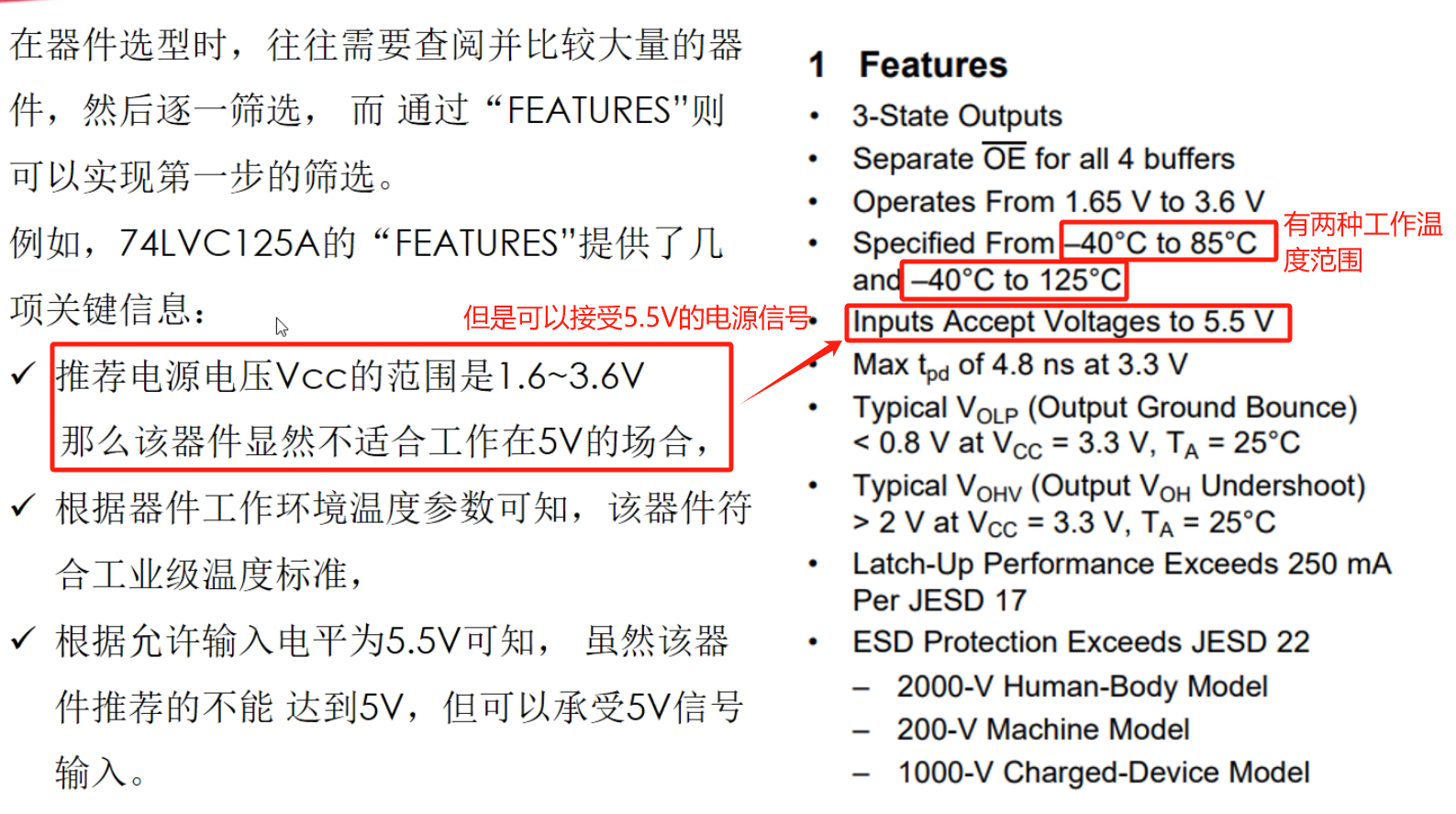

3.1. FEATURES

做最初步的筛选。

3.2 极限参数

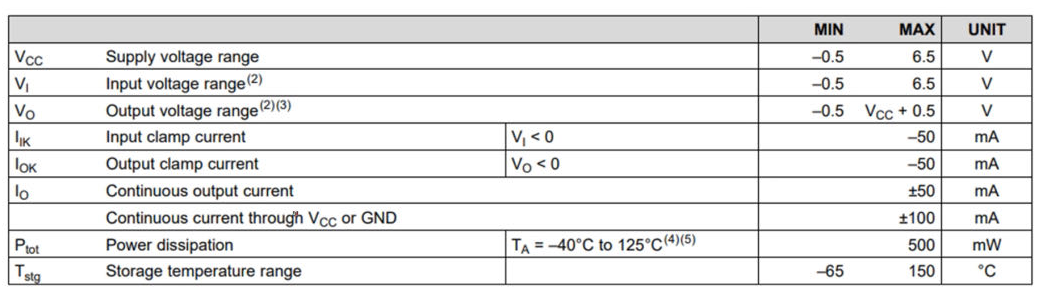

器件的工作条件如果超出了极限工作表中对应的参数,可能造成器件的永久损坏。

(1)进一步筛选,器件极限参数表如下:

:-0.5~6.5 电源电压,应注意两点。第一,确保上电和下电时,电源电压的过压小于极限值。第二,正常工作时,电源电压加上纹波的最大值应小于极限值。

- Vi:输入信号工作范围

- Vo:输出信号工作范围,用来分析下一级接收端的电压

,

:输入、输出的钳位电流

:最大功耗

:存储温度

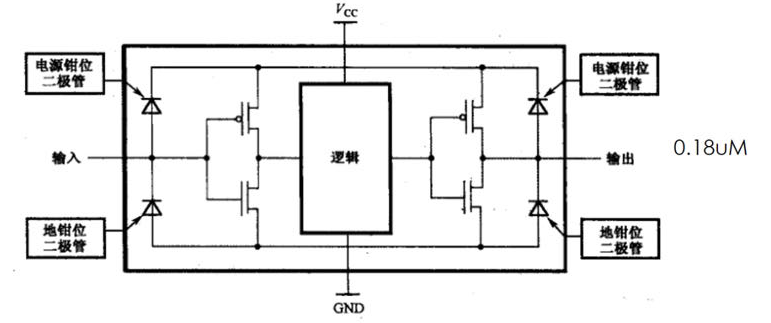

(2)为什么有负值 -0.5 的存在?这相关钳位二极管的作用

输出时,变成高电平或者低电平的时候都会出现过压或者过冲。如下图:

CMOS 器件的输入端电平如超出电源电压或地电平,将引起站锁。如图所示,为保护逻辑器件,在输入/输出端口与电源 Vcc、GND 之间,往往内置有钳位二极管,当端口电平超出 Vcc 或 GND时,该二极管能将电平钳位在极限的范围之内,从而避免对器件的损坏。

CMOS器件在输入/输出端口往往都内置有钳位二极管,其中对地的钳位二极管必有,对电源Vcc的钳位二极管不一定会有。当电平低于地时,地钳位二极管导通,将端口电平钳位在 -0.5V 。

没有电源钳位二极管是靠 MOS 管的工艺保证它不会损坏,栅极和源级之间加一条沟壑或者做栅源保护。

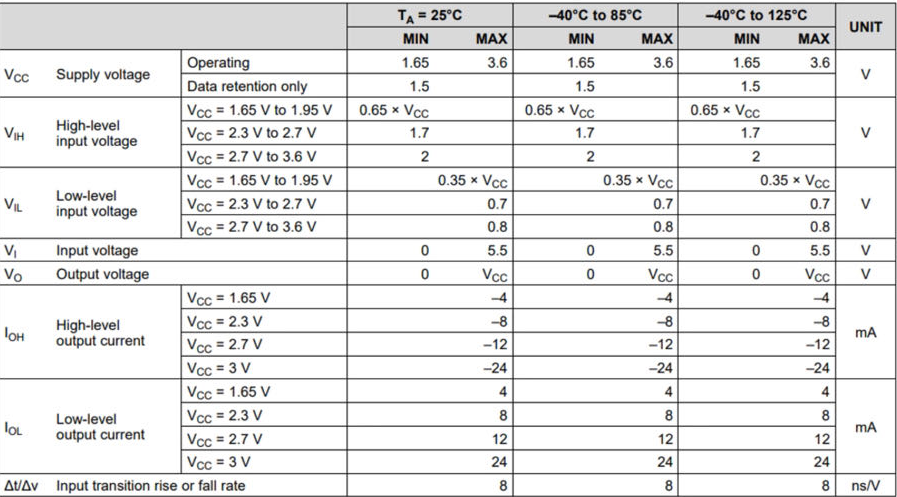

3.3推荐参数表

(1)表中数据

- Vcc:电源电压

,

:输入高电平最小值,输入高电平最大值(之前说过具体定义了)

,:推荐输入电流的范围,最大到 5.5V ,所以是可以和 5V 电压互联

:推荐输出电流的范围,跟随 Vcc

,

:输出高电平和低电平时的最大电流,就是最大的拉电流和灌电流

:输入信号变化沿速率的要求。只有输入信号变化沿速率满足这个要求,逻辑器件才能够正确的识别并做出正确的反应。输入信号变化沿越缓,则处于非稳态的时间越长,对器件工作状态越不利。

造成输入信号变化沿缓的原因:1 驱动能力不足 2.容性负载太大

(2)当输入电压处于 ~

之间时,管子部分导通,可能出现以下几种情况:

- 振荡

- 得到的逻辑电平可能不对,后续不能做出正确的反应

- 从Vcc到地有通路,有比较大的静态电流

- 输入过大产生振铃,损坏器件

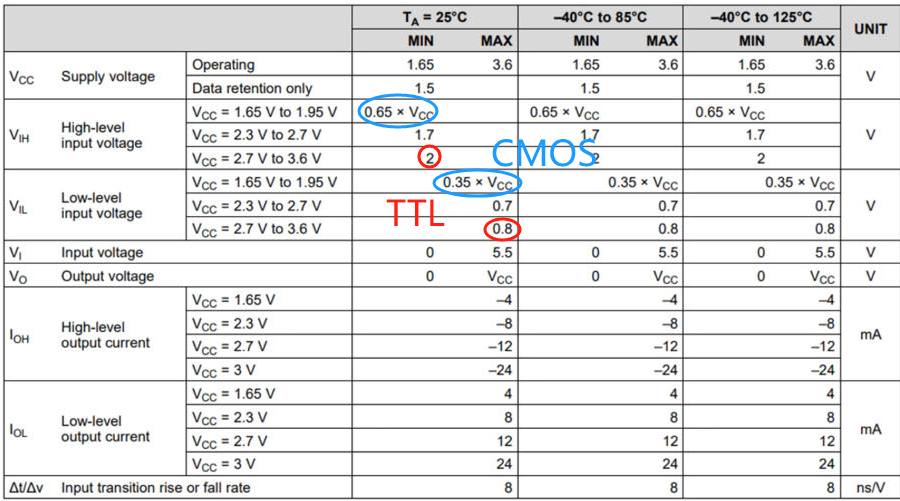

(3)判断器件是TTL逻辑还是CMOS逻辑,如下图

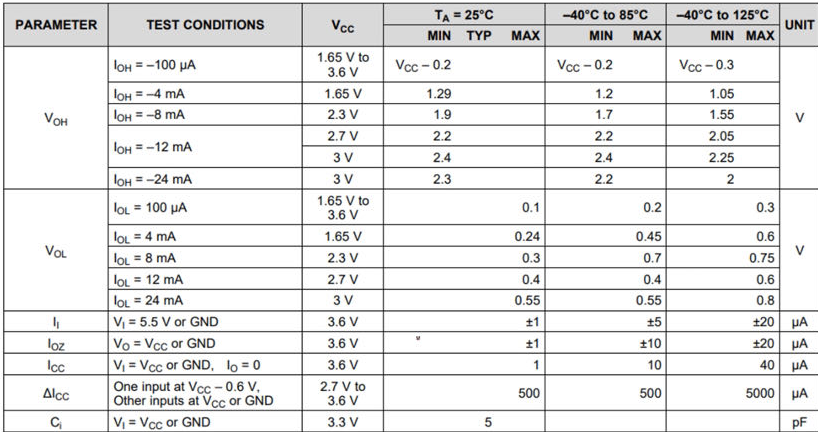

3.4逻辑器件电器参数表

:器件正常工作时流入的电流。CMOS器件都是压控型,该电流值非常的小

:输出高组态的漏电流

:静态电流,处于静态无负载时的流入引脚Vcc的电流值

:TTL 给 CMOS 输入时(不行),引起的电流变化

:器件输入端口的集成电容

四、逻辑器件功耗计算

本节重点介绍如何计算CMOS工艺逻辑器件的功耗,

- 逻辑器件资料中,一般都会给出器件工作时的最大功耗

参数。

CMOS器件功耗分为静态功耗和动态功耗 - 当器件所有端口的逻辑状态稳定而不发生变化,则端口无需充/放电,器件内部仅存在泄漏电流lcc,此时的功耗就是静态功耗。

- 当器件端口的逻辑状态发生不断的翻转,器件内部除泄漏电流外,还存在工作电流,且为了驱动容性负载,器件的输出端还需不断充放电,这种由于器件逻辑状态翻转 而产生的功耗,称为动态功耗。

4.1静态功耗

静态功耗由一下两个部分组成。

(1)由器件内部泄漏电流产生。

如74LVC125A在25℃时漏电流仅1uA,而在125 ℃时漏电流能达到40uA。这一部分功耗的计算公式为

(2)当输入电平不满足器件输入引脚的阔值电平时,器件内部本应完全关断的MOS管并没有被完全关断

4.2动态功耗

动态功耗分为瞬变功耗 和容性负载功耗

器件还逻辑状态改变时,需对内部的容性节点充放电,这个过程存在功率损耗,同时,逻辑状态的改变,伴随着器件内部 MOS管的开合,在某些瞬间,两管同时处于闭合导通的状态,从而形成VCC到GND的电流通路,造成功耗。

3877

3877

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?