一、逻辑电平

逻辑电平是指一种可以产生信号的状态,通常由信号与地线之间的电位差来体现。逻辑电平的浮动范围由逻辑家族中不同器件的特性所决定。

1、地线

地线是在电系统或电子设备中,接大地、接外壳或接参考电位为零的导线。一般电器上,地线接在外壳上,以防电器因内部绝缘破坏外壳带电而引起的触电事故。地线是接地装置的简称。

2、电势差(电压)

电势差,是衡量单位电荷在静电场中由于电势不同所产生的能量差的物理量。此概念与水位高低所造成的“水压”相似。

需要指出的是,“电压”一词一般只用于电路当中,“电动势”和“电位差”则普遍应用于一切电现象当中。

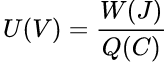

电压的国际单位是伏特(V)。1伏特等于对每1库仑的电荷做了1焦耳的功,即

3、常用的逻辑电平

单端:TTL、CMOS、LVTTL、LVCMOS、GTL、BTL、ETL、GTLP、SSTL2-I、SSTL2-II、SSTL3-I、SSTL3-II、HSTL-I、HSTL-II、HSTL-III、HSTL-IV、HSUL_12、POD12、POD10等

差分:ECL、PECL、LVPECL、LVDS、BLVDS、LP-LVDS、CML、DIFF_HSTL、DIFF_SSTL、DIFF_HSUL、TMDS、PPDS、RSDS等。

4、通用逻辑电平

5vTTL逻辑电平和5vCMOS逻辑电平

5、相关术语

(1).输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。

(2).输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。

(3).输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh。

(4):输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol。

(5).阈值电平(Vt):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平> Vih,输入低电平 <Vil。

对于一般的逻辑电平,Vih,Vil,Voh,Vol以及Vt的关系可表示如下:

Voh> Vih > Vt > Vil > Vol。

(6).Ioh:逻辑门输出为高电平时的负载电流(为拉电流)。

(7).Iol:逻辑门输出为低电平时的负载电流(为灌电流)。

(8).Iih:逻辑门输入为高电平时的电流(为灌电流)。

(9).Iil:逻辑门输入为低电平时的电流(为拉电流)。

6、常见的逻辑电平标准

RS232:ANSI/TIA/EIA-232-F-1997

RS422:ANSI/TIA/EIA-422-B

RS485:ANSI/TIA/EIA-485-A

LVTTL/LVCMOS:JESD8-5,JESD8-B

SSTL:JESD8-8,JESD8-9B,JESD8-15

HSTL:JESD8-6

POD12:JESD8-24

LVDS:ANSI/TIA/EIA 644

SCI-LVDS:IEEE 1596.3

MLVDS:ANSI/TIA/EIA 899-2001

7、电平通常标准参数

(具体芯片建议参考Datasheet)

8、逻辑电平的转换

这块内容我也不太懂,就不献丑了哈,总之挺关键的

二、逻辑器件的分类

常见的有“与”门、“或”门、“非”门、“与非”门及“或非”门等。 利用这些门可以组成电子计算机所需的各种逻辑功能电路。

最常用的就是74~逻辑器件

1、与门:利用内部结构,使输入两个高电平(1),输出高电平(1),不满足有两个高电平(1)则输出低电平(0)。

2、或门:利用内部结构,使输入至少一个输入高电平(1),输出高电平(1),不满足有两个低电(0)输出高电平(1)

2、或门:利用内部结构,使输入至少一个输入高电平(1),输出高电平(1),不满足有两个低电(0)输出高电平(1)

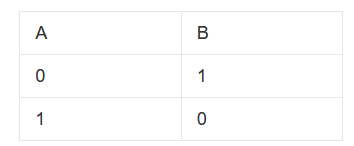

3、非门:利用内部结构,使输入的电平变成相反的电平,高电平(1)变低电平(0),低电平(0)变高电平(1)。

3、非门:利用内部结构,使输入的电平变成相反的电平,高电平(1)变低电平(0),低电平(0)变高电平(1)。

4、与非门:利用内部结构,使输入至多一个输入高电平(1),输出高电平(1),不满足有两个高电平(1)输出高电平(1)。

4、与非门:利用内部结构,使输入至多一个输入高电平(1),输出高电平(1),不满足有两个高电平(1)输出高电平(1)。

5、或非门:利用内部结构,使输入两个输入低电平(0),输出高电平(1),不满足有至少一个高电平(1)输出高电平(1)。

6、异或门:当输入端同时处于低电平(0)或高电平(1)时,输出端输出低电平(0),当输入端一个为高电平(1),另一个为低电平时(0),输出端输出高电平(1)。

7、同或门:当输入端同时输入低电平(0)或高电平(1)时,输出端输出高电平(1),当输入端一个为高电平(1),另一个为低电平时(0),输出端输出低电平(0)。

逻辑电路按其工作性质可分为组合电路和时序电路两大类:

组合逻辑电路

任何时刻输出信号的逻辑状态仅取决于该时刻输入信号的逻辑状态,而与输入信号和输出信号过去状态无关的逻辑电路。由于组合逻辑电路的输出逻辑状态与电路的历史情况无关,所以它的电路中不包含记忆性电路或器件。门电路是组合逻辑电路的基本单元。当前组合逻辑电路都已制成标准化、系列化的中、大规模集成电路可供选用。

时序逻辑电路

任何时刻的输出状态不仅与该时刻的输入有关,而且还与电路历史状态有关的一种数字逻辑电路。时序逻辑电路具有记忆输入信息的功能,由于它的引入使得数字系统的应用大大增强。常用的有计数器、寄存器和脉冲顺序分配器等。

也可以按照原件对逻辑电路进行分类,例如:电阻-晶体管逻辑电路、二极管-晶体管逻辑电路、发射极功能逻辑电路、发射极耦合逻辑电路、高阈值逻辑电路、集成注入逻辑电路、晶体管-晶体管逻辑电路。

三、逻辑器件的参数选择参考

(1)电源及地的引脚较近和/或多个电源及地线引脚。

(2)输出电压波动性——————小

(3)可控开关速率

(4)与传输线匹配的I/0电路

(5)差动信号传输

(6)地线反射——————较低

(7)对ESD及其他干扰现象具各抗扰性

(8)输入电容——————小

(9)输出级驱动能力不超过最大实际应用的需求

(10)电源瞬态电流——————低

注意事项

注意事项

1、根据需要选型,不建议盲目地选择性能最好的器件。以驱动能力为例,设计中盲目选择驱动能力最强的器件,一方面可能造成辐射增大,产生EMI(电磁干扰)问题,另一方面也可能导致输出信号过冲太大,超出接收器件输入电平的范围;

2、时序设计中不能依赖逻辑器件的延时。逻辑器件都具有片内传输延时,但是该参数的器件间差异性较大,不能在设计中被利用;

3、使用具有总线保持功能的器件时,外部上、下拉不能太弱(即电阻阻值不能太大);

4、未用的输入端口电平为CMOS时,需要做上、下拉处理;

5、电源上电速率、输入信号边沿速率应满足器件资料中对应参数的要求;

6、在热插拔接口器件的应用中,为防止冲击,输出端一般应串联50Ω的电阻,输入端一般应串联100~200Ω的电阻。此时,应确认串联电阻不会对信号电平产生分压影响,以致输入端电平不能满足要求;

7、当存在热插拔要求时,应根据热插拔的级别,选择对应的器件。

2092

2092

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?