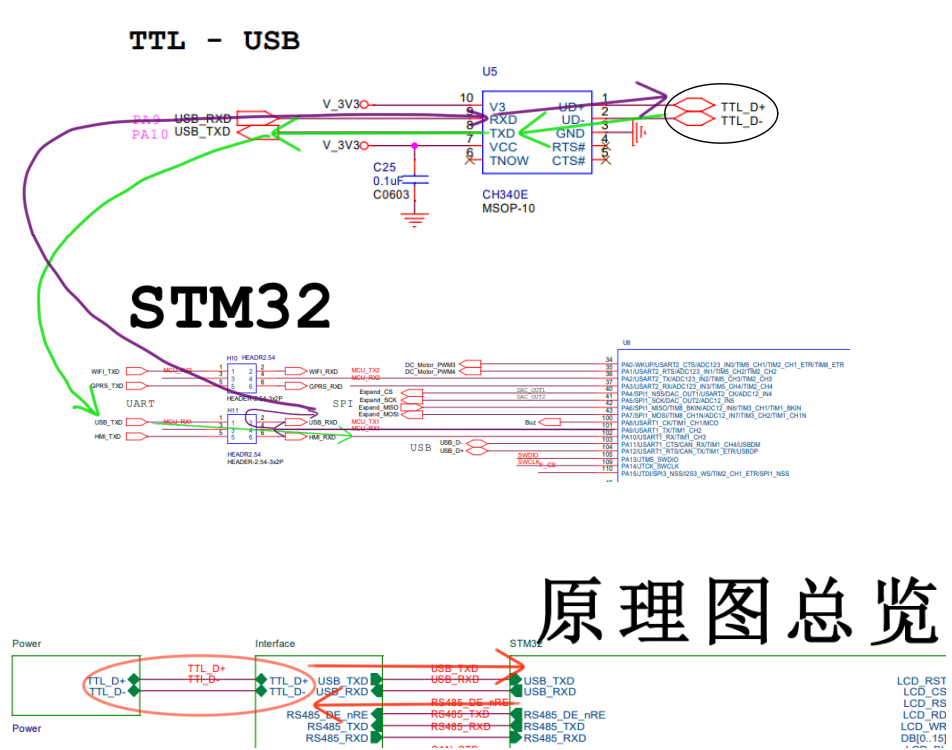

一、TTL 转 USB 驱动电路设计

1.1指路

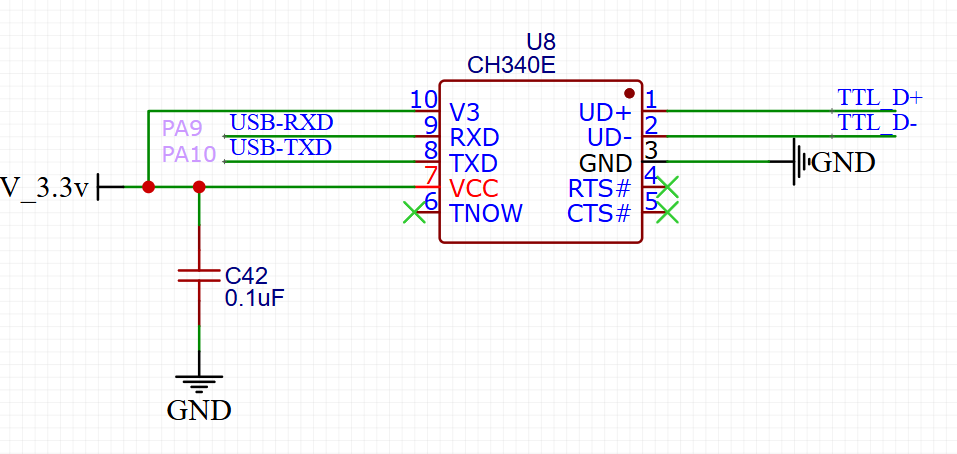

延续使用芯片 CH340E 。

1.2数据手册重要信息提炼

1.2.1概述

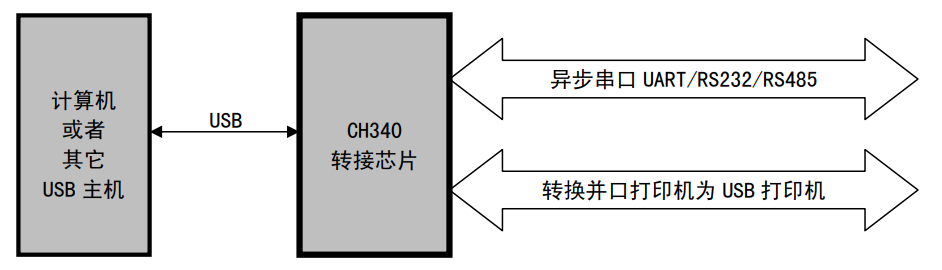

CH340 是一个 USB 总线的转接芯片,实现 USB 与串口之间的相互转化。

1.2.2特点

- 支持常用的 MODEM 联络信号 RTS(请求发送)、DTR(数据终端就绪)、DCD(数据载波检测)、RI(振铃指示)、DSR(数据设备就绪)、CTS(清除发送)。

- 通过外加电平转换器件,提供 RS232、RS485、RS422 等接口。

- 支持 5V 电源电压和 3. 3V 电源电压。

- CH340C/N/K/E/X/B 内置时钟,无需外部晶振。

1.2.3引脚

| 引脚号 | 引脚名称 | 类型 | 引脚说明 |

| 1 | UD+ | USB信号 | 直接连到 USB 总线的 D+ 数据线,不要串联电阻 |

| 2 | UD- | USB信号 | 直接连到 USB 总线的 D- 数据线,不要串联电阻 |

| 3 | GND | 电源 | 公共接地端,直接连到 USB 总线的地线 |

| 5 | |||

| 6 | |||

| 7 | VCC | 电源 | 3.3V 正电源输入端,需要外接 0.1uF 电源退耦电容 |

| 8 | TXD | 输出 | 串行数据输出 |

| 9 | RXD | 输入 | 串行数据输入,内置可控的上拉和下拉电阻 |

| 10 | V3 | 电源 | 在 3.3V 电源电压时连接 VCC 输入外部电源 在 5V 电源电压时外接容量为 0.1uF 退耦电容 |

1.2.4其他说明

- CH340 未用到的 I/O 引脚可以悬空。

- CH340 芯片支持 5V 电源电压或者 3.3V 电源电压。

当使用 5V 工作电压时,CH340 芯片的 VCC 引脚输入外部 5V 电源,并且 V3 引脚应该外接容量为 0.1uF 的电源退耦电容。当使用 3.3V 工作电压时,CH340 芯片的 V3 引脚应该与 VCC 引脚相连接,同时输入外部的 3.3V 电源,并且与 CH340 芯片相连接的其它电路的工作电压不能超过 3.3V。 - CH340 芯片内置了 USB 上拉电阻,UD+ 和 UD- 引脚应该直接连接到 USB 总线上。

- 异步串口方式下 CH340 芯片的引脚包括:数据传输引脚、MODEM 联络信号引脚、辅助引脚。

- 数据传输引脚包括: TXD 引脚和 RXD 引脚。串口输入空闲时,RXD 应为高电平。串口输出空闲时,CH340G/C/N/E/X/B/T 芯片的 TXD 为高电平。

- TNOW 引脚以高电平指示 CH340 正在从串口发送数据,发送完成后为低电平,在 RS485 等半双工串口方式下,TNOW 可以用于指示串口收发切换状态。

1.3原理图

1.3.1 v1.0

存在的错误:

(1)5V 供电

- 你的依靠原理不成立:虽然之前电源原理图中 USB 口进行了 5V 供电,但是 5V 供电是为了全局供电,其中的 TTL_D+、TTL_D- 是单纯的数据传输。

- 元器件浪费:5V 供电除了 0.1uF 电容滤波之外(数据手册的意思),还需要 100uF 铝电解大电容或10uF 电容滤波。

- 数据手册中说:3.3V 供电时与 CH340 芯片相连接的其它电路的工作电压不能超过 3.3V。

信息传输后一级的 STM32 和其他主要组件工作在 3.3V,应当选择3.3V供电,而不是 5V 。

(2)TNOW 引脚

无需进行串口正在发送状态指示,可以悬空,不用接电阻耗能。

1.3.2 v2.0

1.4 USB信号的全局理解

- USB 的 “写” 是 STM32 的 “读串口”,USB 的 “读” 是 STM32 的 “写串口”。

- STM32 原理图部分应该是通过跳线帽的方式来确认数据的路线。

- USB 部分既可以用来供电,又可以用来数据的两方向传输。

二、RS-485 接口设计

2.1指路

延续使用芯片 SP3485EEN,封装为SOP-8。

2.2数据手册

一定一定要去看之前的笔记,详细的讲解了这款芯片。UART、RS232、RS485基础知识+硬件知识_uart rs485-CSDN博客

2.2.1功能

将外界采用 RS485 通信的设备转成 串口 通信,得以和单片机进行通信。

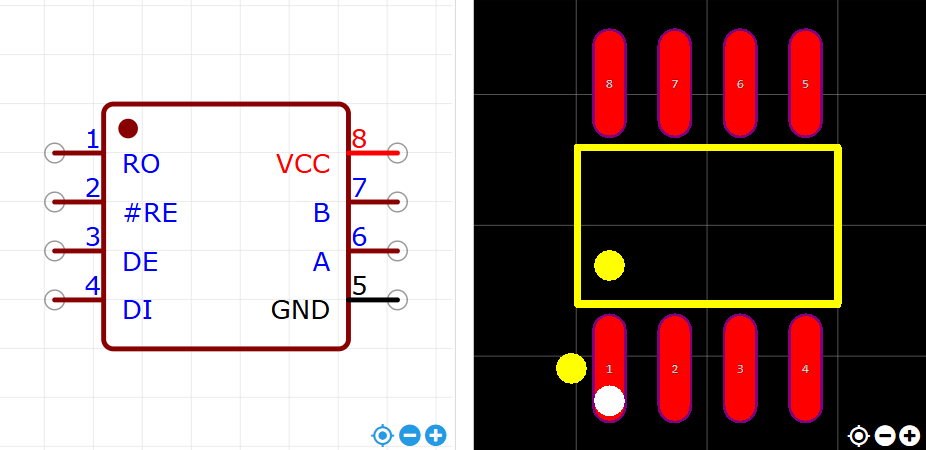

2.2.2引脚

| 序号 | 引脚名称 | 功能介绍 |

| 1 | RO | 接收器输出 当 |

| 2 | 接收器输出使能控制 当 | |

| 3 | DE | 驱动器输出使能控制 当DE为高电平时,驱动器输出可用。 当DE为低电平时,输出处于高阻抗状态。 |

| 4 | DI | 驱动器输入 当DE为高电平时, DI低电平迫使非反相驱动器输出A为低电平,反相驱动器输出B为高电平; Dl高电平迫使非反相驱动器输出A为高电平,反相驱动器输出B为低电平。 |

| 5 | GND | 地面 |

| 6 | A | 非反相接收器输入和非反相驱动器输出 |

| 7 | B | 反相接收器输入和反相驱动器输出 |

| 8 | VCC | 电源供应 |

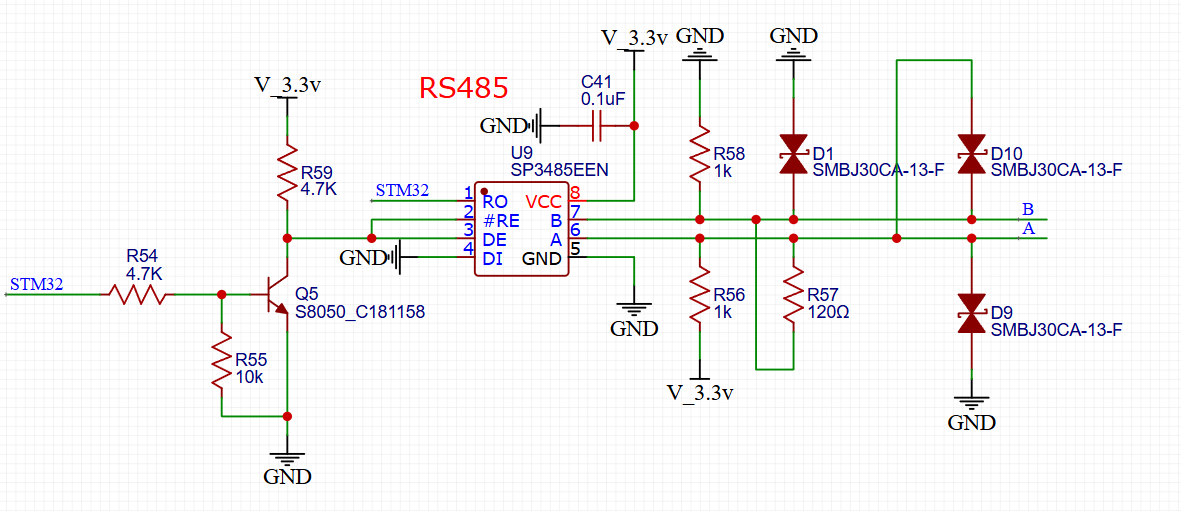

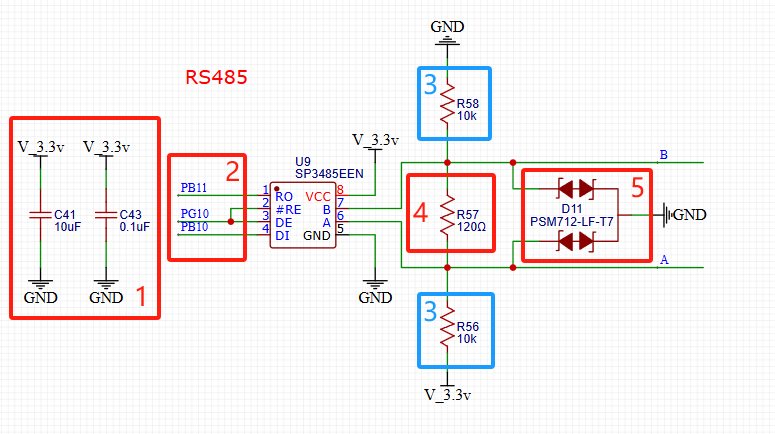

2.3原理图V1.0

自己根据之前的笔记设计:

(见UART、RS232、RS485基础知识+硬件知识_uart rs485-CSDN博客)

2.4原理图V2.0

2.4.1滤波电容

我知道你肯定好奇:都是3.3V供电,为什么有的模块滤波要 0.1uf ,10uf,0.1uf +10uf 滤波?

在这里我只解释这个模块的原因,后面再写博客统一归纳总结。

- 0.1μF电容:通常用于高频滤波,抑制高频噪声。它们具有较低的等效串联电感(ESL),适合滤除电源线上高频噪声和瞬态干扰。

- 10μF电容:主要用于低频滤波,提供较大的电流储备,能够平滑电压波动,稳定电源供应。

- 组合使用 0.1μF 和 10μF 电容:RS-485 通信需要稳定的电源来保证长距离传输的可靠性。0.1μF 电容用于高频滤波,而 10μF 电容则提供低频稳定性和电流储备,从而避免电源波动影响通信质量。

2.4.2引脚

单片机的引脚足够,不需要 V1.0 的方案来节约引脚,DI 直接接到单片机引脚上,在电路 V1.0 中我选择是 1K ,老师选择的是 10K ,分析如下:

2.4.3上下拉电阻

上拉和下拉电阻用于在 RS-485 总线空闲时将总线保持在一个已知的状态。

(1)10KΩ电阻

陈氏:电阻大,电流小,影响小,功耗低。远距离或设备多时,可能不足以提供足够的电流。

优点:功耗较低,适用于大多数情况下的偏置电阻。由于阻值较大,它不会对通信信号产生明显的负载影响。缺点:在长距离传输或总线电容较大时,可能不足以提供足够的偏置电流,导致总线状态不稳定。

(2)1KΩ电阻

陈氏:电阻小,电流大,影响大,功耗高。远距离或设备多时,提供更足够的电流。

优点:提供更强的偏置电流,在长距离和较大电容负载情况下能更好地保持总线稳定。缺点:功耗较高,并且在总线上的负载影响更大,可能在某些情况下影响通信信号的质量。

根据该项目的具体情况,485 设备少,距离近,选择 10K。

2.4.4 阻抗匹配

见:UART、RS232、RS485基础知识+硬件知识_uart rs485-CSDN博客

2.4.5 TVS管

参考老师建议使用 PSM712-LF-T7 (STO-23封装),该 TVS 管专用于静电和浪涌保护。数据手册中说明常应用于 RS485 端口。

三、CAN 总线接口设计

3.1指路

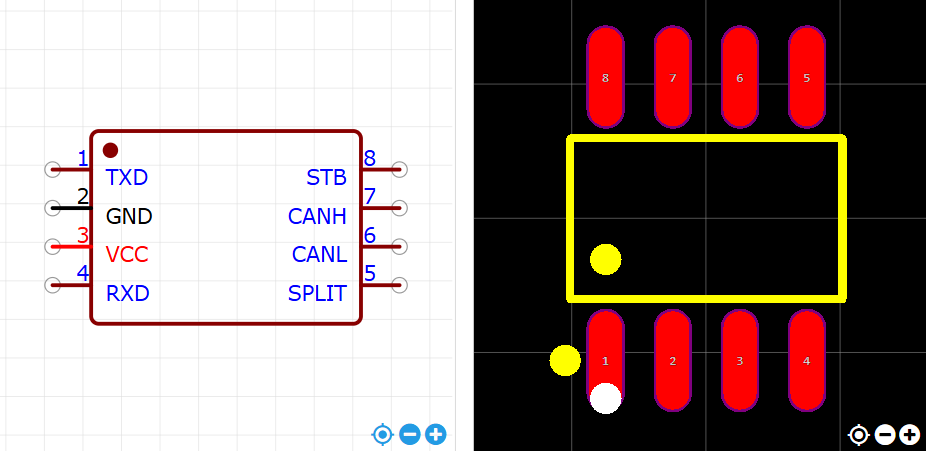

延续使用芯片 TJA1040T-JSM,封装为SOP-8。

3.2数据手册

3.2.1概述

TJA1040T 是 CAN 收发器,能够为信号传输速率高达 1Mbps 的 CAN 控制器提供差分传输和接收。

3.2.2引脚说明

| 引脚 | 符号 | 说明 |

| 1 | TXD | 传输数据输入。TXD 为高 CAN 总线输出为隐性态,TXD 为低 CAN 总线输出为显性态。 |

| 2 | GND | 地。 |

| 3 | VCC | 供电电压。 |

| 4 | RXD | 接收器数据输出。当 CAN 总线处于隐性态时候,RXD 为高电平。当 CAN 总线处于显性态时候,RXD 为低电平。 |

| 5 | SPLIT | 共模稳定输出端口。 |

| 6 | CANL | 低电平 CAN 总线端口。 |

| 7 | CANH | 高电平 CAN 总线端口。 |

| 8 | STB | 待机模式控制输入端口。 |

3.2.3 STB

STB 输入 (引脚 8 ) 用于在两个不同的运行模式之间做出选择,即高速模式或低速模式,使用中可通过将 STB 引脚接地来选择高速运行模式。

(1)正常模式

通过将 STB 引脚设置为低,选择芯片的正常工作模式。CAN 总线驱动器和接收器完全工作,CAN 总线双向通信。驱动器将 TXD 引脚的数字输入信号转换为 CANH 和 CANL 引脚的差分输出电平。接收器将来自 CANH 和 CANL 引脚的差分电平转换为 RXD 引脚的数字输出信号。

(2)待机模式

在此模式下,驱动器和接收器关闭,低功耗差分接收器监控总线状态。引脚 STB 上的高电平激活低功耗接收器和唤醒滤波器,在 tus 时间之后,CAN 总线的状态会反映在引脚 RXD 上。VCC 上的电源电流降低到最小值,以降低电磁干扰( EM ),同时对总线上唤醒标识进行辨识。在这种模式下,总线接地可将供电电流 ( lcc ) 降至最低。

(3)唤醒

在待机模式下,芯片通过低功耗差分比较器监测总线。一旦低功耗差分比较器检测到显性总线电平超过时间 tBus,引脚 RXD 将变为低电平。

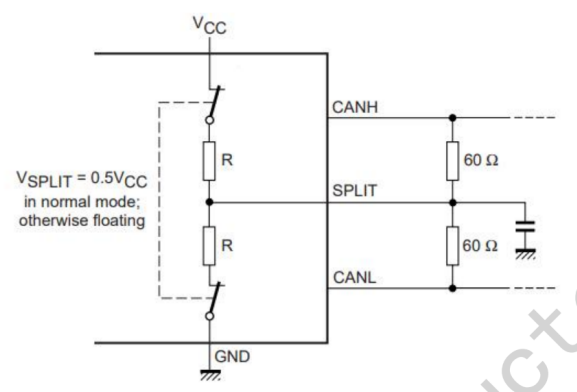

3.2.4 SPLIT

CAN 总线大量节点需要 TJA1040T 这类具有高输入阻抗和宽共模范围的收发器收发器。

- 高输入阻抗意味着收发器对总线信号的负载很小,减少了每个节点对总线的影响。在大规模网络中,如果每个节点的输入阻抗较低,会显著增加总线的负载,导致信号衰减和失真,进而影响通信的可靠性。高输入阻抗的收发器允许更多节点同时连接到总线而不会导致上述问题。

- 共模范围是指收发器能够接受的信号电压范围。宽共模范围意味着收发器能够在较大的电压范围内正确地接收信号。CAN总线通信使用差分信号线,但由于不同节点的接地电位可能存在差异,信号线上的电压可能会有共模偏移。具有宽共模范围的收发器能够在存在这些偏移的情况下仍然可靠工作,确保在复杂电气环境中的稳定通信。

ISO11898 标准规定互连为 120Ω 的双绞线缆 ( 屏蔽或非屏蔽 ) 特性阻抗 ( Zo ) ,应在线缆终端的两端使用等于线缆阻抗特性的电阻以防止信号反射,连接节点未端的接入线到总线的距离应保持尽可能短,以最小化信号反射。

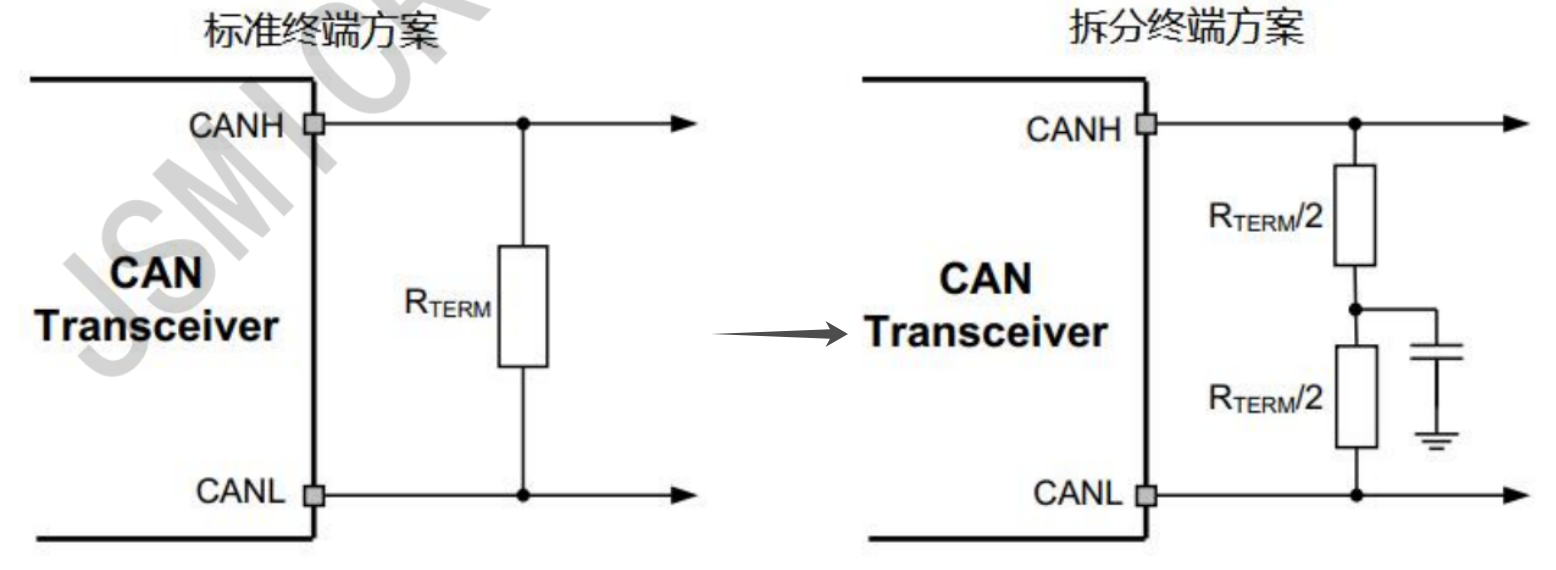

总线两端的匹配终端通常是 120Ω 电阻,如果需要对总线的共模电压进行滤波和稳定,可使用拆分终端方案(见下图)。拆分终端方案使用两个 60Ω 电阻,两个电阻中间有一个电容接地。拆分终端方案可以消除信号传输开始和结束时总线共模电压的波动,从而改善总线网络的电磁辐射。

3.3原理图V1.0

加上参考笔记画的:CAN总线基础知识+硬件知识_can总线技术基础-CSDN博客

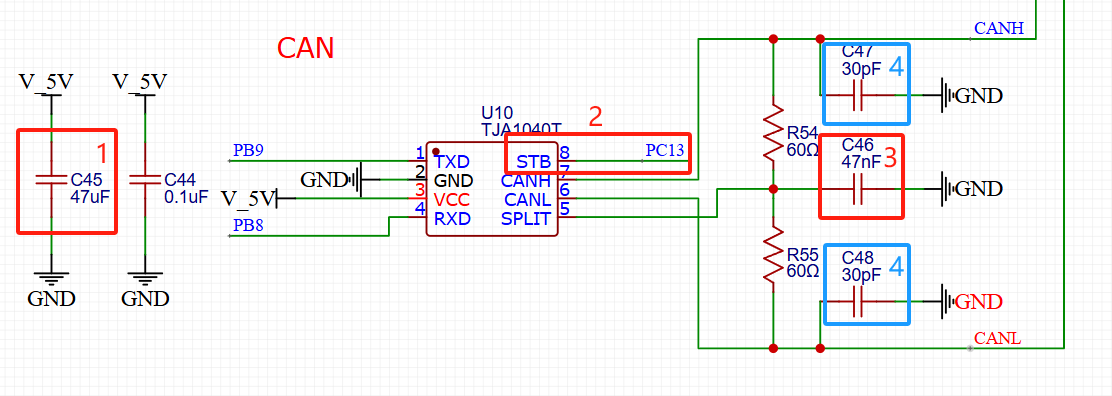

3.4原理图V2.0

第一版设计的电路并没有什么问题,只是老师设计的电路在实际调试时可能更佳。

器件的数值不用过多纠结,更多的是经验值或实际调试中效果更好。

根据老师的原理图有以下改进:

(1)47uF的电源滤波电容:更好地滤除低频噪声,稳定电源电压,尤其是在电流变化较大的情况下更为有效。

(2)STB:接入单片机引脚,改为可以由单片机选择高速模式或低速模式。

(3)47nF 电容:提供稳定的参考电压,并滤除中频噪声,可以减少电磁干扰,提高总线的信号完整性。

(4)30pF 电容:这些电容用于滤除CAN总线中的高频噪声,保护总线的信号完整性。高频噪声可能来自于外部的电磁干扰或者内部的高频开关动作,这些电容可以有效地滤除这些干扰信号,确保CAN总线通信的稳定性。

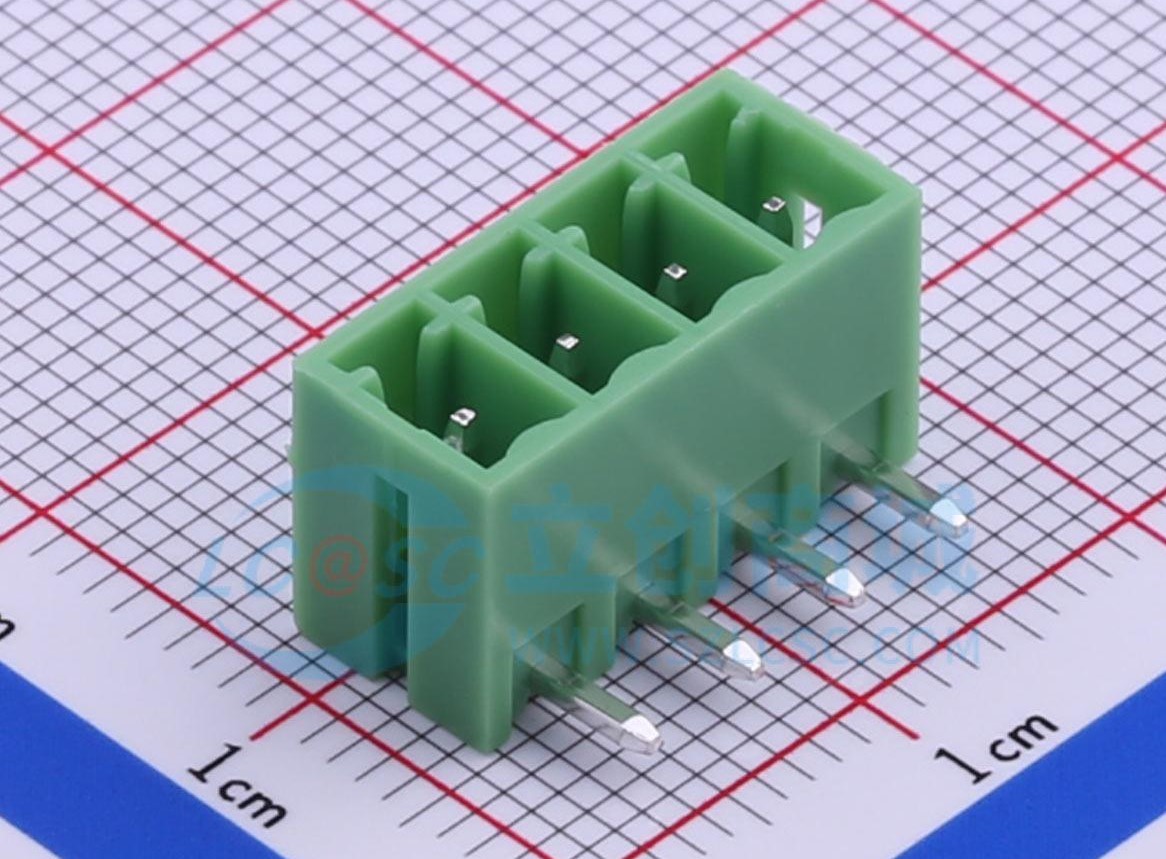

(5)最后 RS485 和 CAN 总线都连接到 KF2EDGR-3.81-4P 插拔式接线端子,方便连接、断开、调试与维护。

四、TF卡座设计

4.1指路

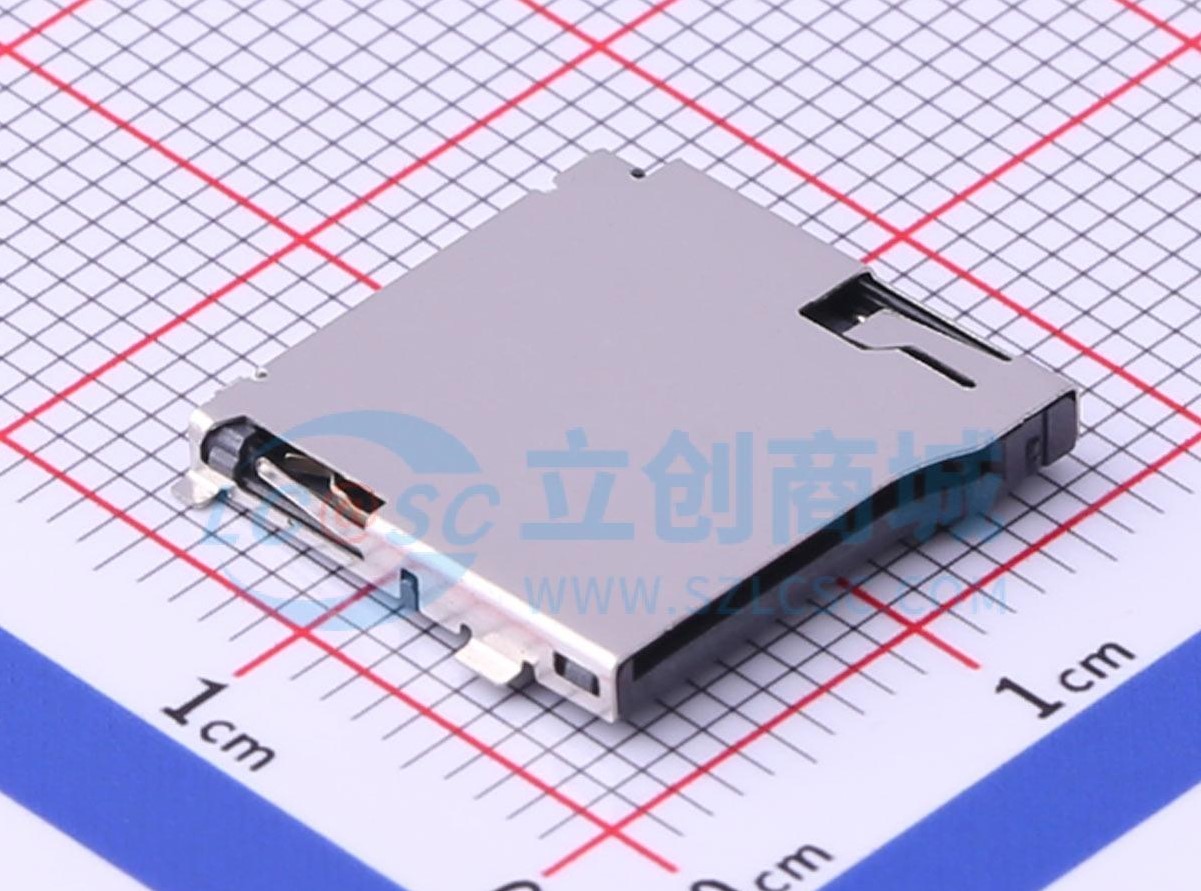

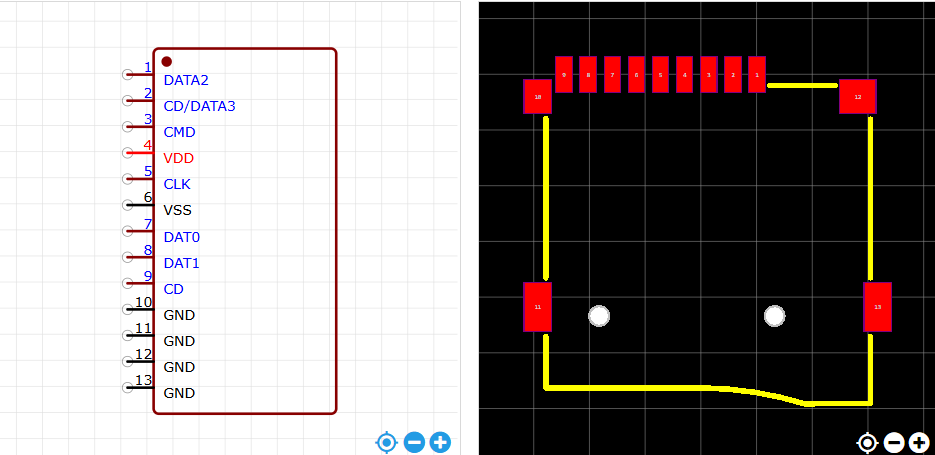

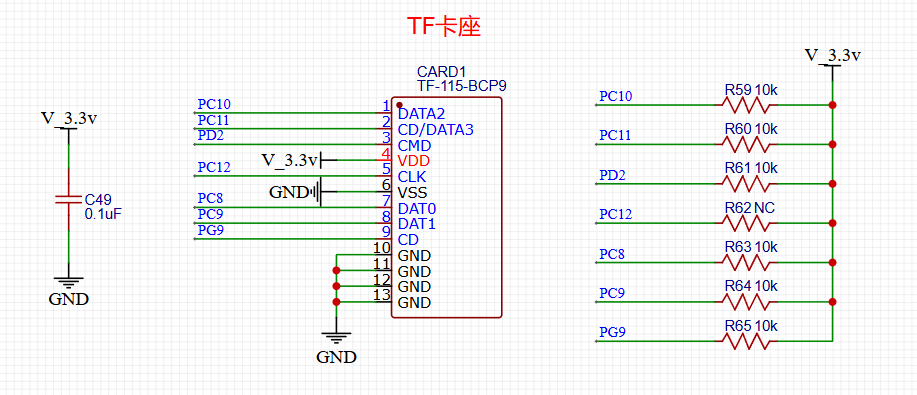

使用芯片:TF-115-BCP9 ,封装: SMD,描述: 9P 自弹式 TF 卡座,类目:SD卡/存储卡连接器。

4.2引脚说明

| 序号 | 名称 | 类型 | 说明 |

| 1 | DAT2 | I/O/PP | 数据线(位2) |

| 2 | CD/DAT3 | I/O/PP | 卡检测 / 数据线(位3) |

| 3 | CMD | PP | 命令响应 |

| 4 | VDD | S | 电源电压(3.3V) |

| 5 | CLK | I | 时钟 |

| 6 | VSS | S | 电源地 |

| 7 | DAT0 | I/O/PP | 数据线(位0) |

| 8 | DAT1 | I/O/PP | 数据线(位1) |

4.2.1“类型”说明:

- I:输入。

- O:输出。

- PP:推挽输出。表示该引脚可以输出高电平或低电平,而不是高阻态。

- S:电源引脚。

4.2.2详细说明

(1)DAT2、DAT0、DAT1 数据线

- 功能:用于与 TF 卡交换数据,其中 DAT0 是主要的数据传输线,DAT1 是一个辅助数据传输线。。

- 接线方式:通常连接到主控芯片的数据总线相应引脚。

(2)CD / DATA3 卡检测 / 数据线3

- 功能:在 SPI 模式下,作为数据线 3;在 SD 模式下,还可以用于卡插入检测。

- 说明:SPI模式适用于简单、低速通信,SD模式适用于高速、大容量存储需求。选择何种模式取决于应用需求和主控芯片的支持情况。

- 接线方法: 连接到主控芯片的数据总线或卡检测电路。

(3)CMD 命令/响应

- 功能:用于发送命令和接收来自 TF 卡的响应。

- 接线方法:连接到主控芯片的命令引脚。

(4)CLK 时钟

- 功能:提供时钟信号以同步数据传输。

- 接线方法:连接到主控芯片的时钟引脚。

4.2.3上拉电阻

该 TF 卡座,不是一直都有卡插入其中,故电路中的上拉电阻是非常必要和常见的,有以下作用:

(1)确保引脚有确定的电平:

在没有连接外部信号时,上拉电阻可以确保引脚处于一个确定的高电平(3.3V),避免浮空状态。浮空状态会导致引脚处于不确定的电平状态,可能会引发噪声和误操作。

(2)提高信号稳定性:

上拉电阻能够提升信号的抗干扰能力,增强系统的稳定性。尤其是在长线通信或高频信号环境下,上拉电阻可以减少噪声对信号的影响。

(3)预防未初始化引脚干扰:

在系统初始化过程中,如果某些引脚尚未被软件配置,外部信号未连接或信号源暂时关闭,上拉电阻可以避免这些引脚的意外翻转或错误触发。

4.2.4 NC电阻

在 CLK 电路中,电阻处标明 NC ,表示此处空贴,即此处不贴任何电子器件。如果安装的话,电路会有另外的功能,或许在性能上会有变化。

(1)时钟线(CLK)的特殊性

CLK 引脚负责传输时钟信号,这种信号通常是快速且连续的脉冲。在这种情况下,上拉电阻并不总是必要的,因为时钟信号是主动驱动的,不会处于高阻抗状态。

时钟信号由主控芯片直接驱动,当时钟线没有时钟信号时,其电平状态由主控芯片决定,不会浮动。

(2)避免不必要的干扰

由于时钟信号频率较高,上拉电阻可能会引入不必要的干扰或阻抗匹配问题,影响信号完整性。去掉上拉电阻可以减少这种可能性,提高信号的稳定性和传输质量。

(3)简化电路设计

有时候,在设计中简化电路、减少元件数量也可以提高系统的可靠性和易维护性。对于不需要上拉电阻的引脚,标记为NC可以明确设计意图,避免误操作。

4.3电路图

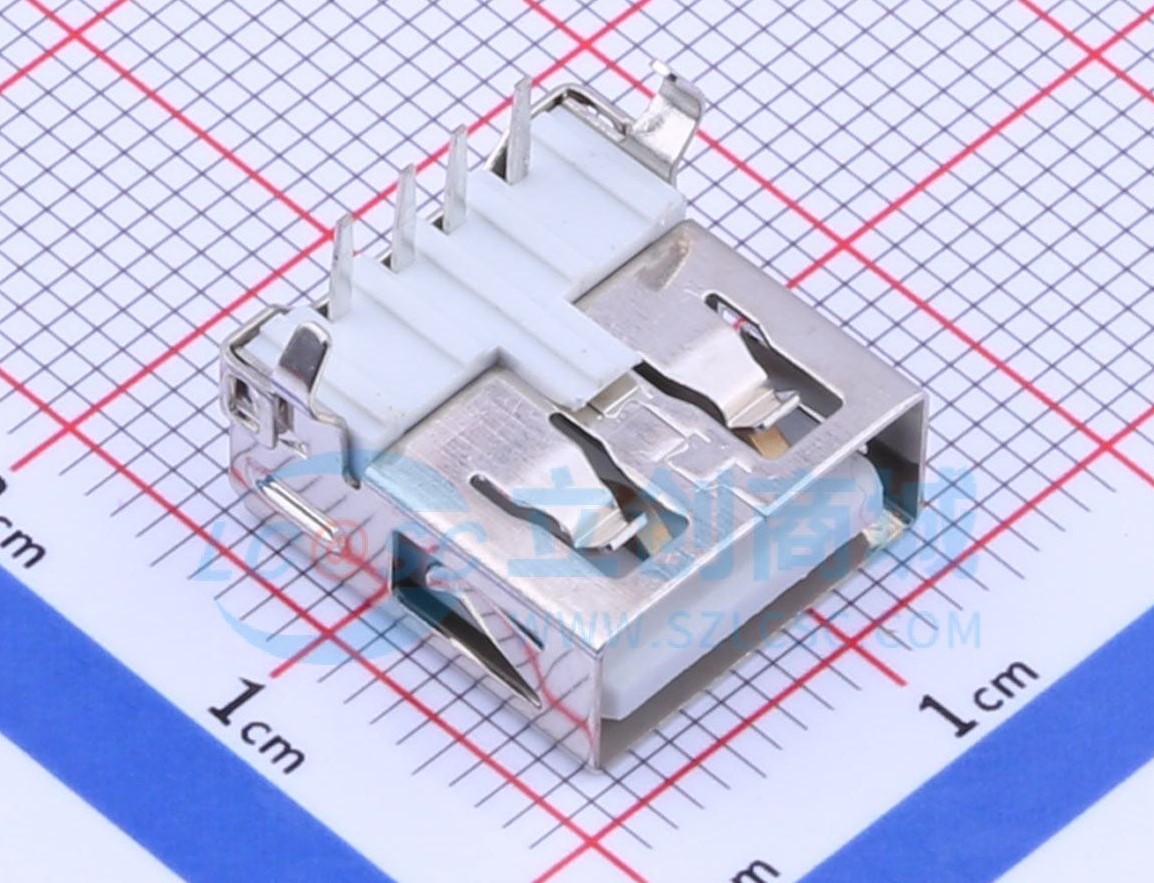

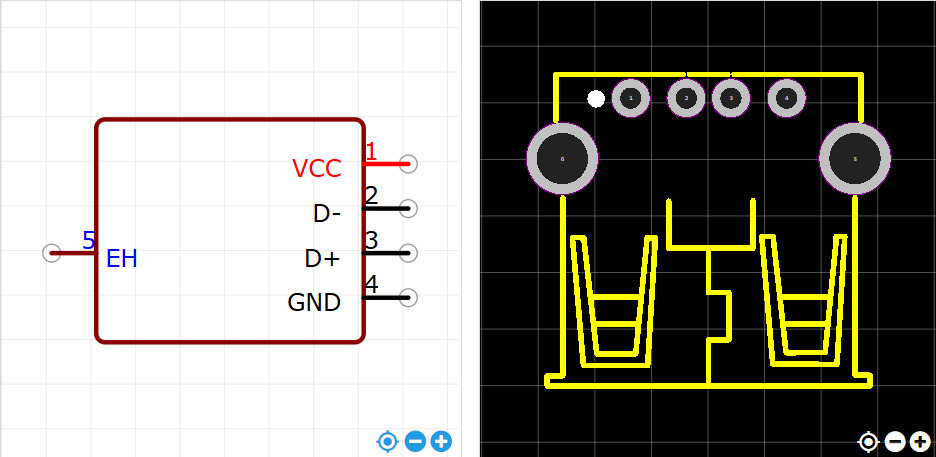

五、USB2.0 设计

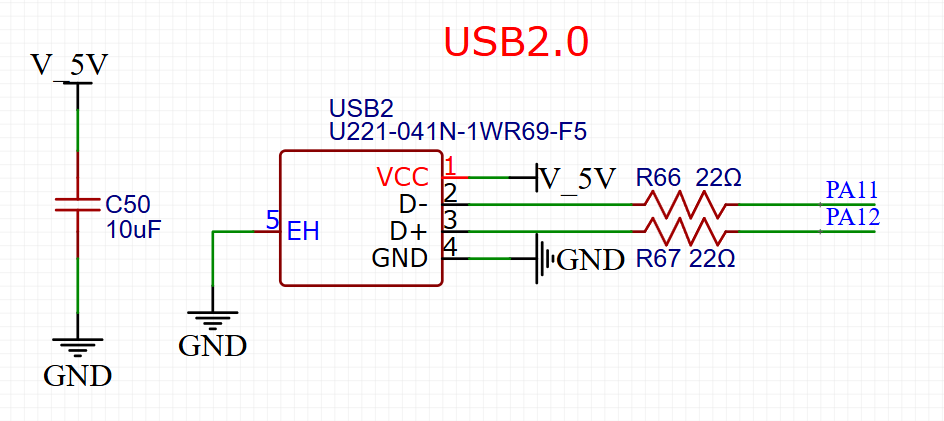

使用 U221-041N-1WR69-F5 器件,设计简单,直接上图。

D- 和 D+ 通过 22Ω 电阻连接到 PA11 和 PA12 的设计,是为了匹配阻抗、抑制噪声、保护微控制器引脚,并提高信号的完整性和稳定性。这种设计实践在 USB 2.0 应用中广泛采用,是确保高速数据传输可靠性的重要措施,后续有总结笔记总结不同的通信、接口需不需要电阻的问题。

六、IIS

6.1 IIS简介

IIS(Inter-IC Sound)是一种专门用于数字音频设备之间传输音频数据的串行总线标准。IIS协议被广泛应用于数字音频设备之间的通信,如数字音频播放器、数字音频处理器、音频解码器等。

6.1.1 IIS的特点

- 同步传输:IIS 是一种同步串行总线,利用时钟信号来同步数据的传输,保证数据的准确性和时序。

- 多声道支持:IIS 支持多声道音频数据的传输,如立体声、5.1 声道等。

- 高质量音频传输:IIS 允许高精度的音频数据传输,通常支持16位、24位甚至32位的音频数据位深。

- 分离的数据和时钟信号:IIS 使用独立的时钟信号和数据线来传输音频数据,减少了抖动和失真,保证了音频的高保真。

6.1.2 IIS接口的引脚和信号

IIS 通常有以下几个主要信号引脚:

- SCK(Serial Clock):串行时钟信号,用于同步数据传输。

- WS(Word Select):字选择信号,用于区分左声道和右声道的数据。

- SD(Serial Data):串行数据线,用于传输音频数据。

- MCLK(Master Clock,可选):主时钟信号,有些设备使用该信号作为更高频率的基准时钟。

6.1.3 IIS接口设计

(1)确定音频设备和微控制器引脚分配

- 查阅音频编解码器和 STM32 的数据手册,确定 IIS 信号(SCK、WS、SD、MCLK)的引脚。

- 在原理图中,将这些信号对应连接到 STM32 的相应引脚。

(2)时钟配置

- 配置 STM32 的外设时钟,使其满足 IIS 通信的时序要求。

(3)添加必要的电容和电阻:

- 在电源引脚(VCC 和 GND)上添加退耦电容(如 0.1uF 和 10uF)。

- 在时钟线(SCK、MCLK)和数据线(WS、SD)上添加适当的匹配电阻(如 33 欧姆)以减少信号反射。

(4)设计 PCB 布线:

- 布线时要注意减少噪声和干扰,尽量使数据线和时钟线短且直。

- 考虑在信号线上加地平面隔离,减少电磁干扰。

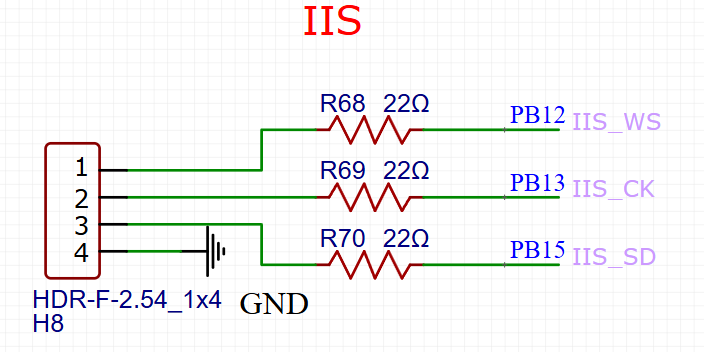

6.2原理图

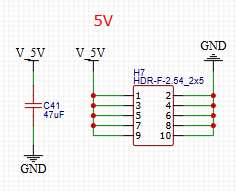

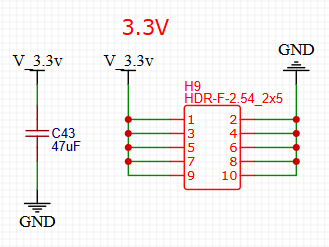

七、电源

7.1简介

(1)电源引出和分配:

- 这种电路设计通常用于为外部模块或外部电路提供电源。通过这种连接器,可以很方便地将3.3V 电源和地引出到其他电路板或模块上。

- 外部模块或电路板可以通过这个连接器获取稳定的 3.3V 电源和地,避免了需要在外部模块上单独生成电源的复杂性。

(2)电源滤波:

- 通过在 3.3V 电源上添加 47uF 的电容进行滤波,可以有效地减少电源噪声和纹波,提供更加稳定和纯净的电源。滤波电容可以去除高频噪声,平滑电源波动,从而保护电路中的敏感组件。

- 滤波电容的值(如 47uF)通常根据系统的需求和电源的噪声特性来选择。更大的电容可以滤除更低频率的噪声,但也会占用更多的空间。

(3)标准化连接器设计:

- 使用标准化的连接器(如 HDR-F-2.54_2x5)可以提高设计的模块化和可维护性。通过标准连接器,设计人员可以轻松地连接和断开模块,方便调试和维护。

- 标准化连接器也便于生产和装配,提高了系统的可靠性和一致性。

7.2电路图

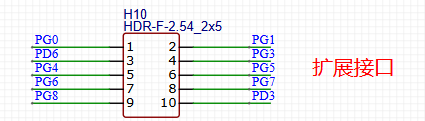

八、扩展接口

在原理图中预留了 10 个 GPIO 口用于需要的时候扩展接口。

还可以有以下扩展。

5993

5993

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?