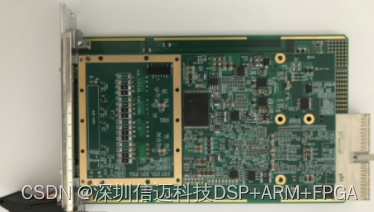

ARINC664双端口终端网卡是一款高性能ARINC664网络接口板卡,支持ARINC664网络仿真、测试及数据分析功能。AES支持2个ARINC664端口,采用RJ45插件形式,可以作为2个独立端口使用,也可以作为1对冗余端口使用。AES集成IRIG-B系统时钟,提供多个节点时钟同步功能,便于多节点仿真系统使用。ARINC664通讯规范完全符合ARINC664航空电子网络PART7协议要求。

技术规格:

| 项目 | 参数 | |

| 功能指标 | 端口数量 | 2路,2个端口互为冗余 |

| 端口速率 | 提供2个10/100M的RJ45规格ARINC664端口 | |

| 协议规范 | 支持ARINC664规范 | |

| 端口配置 | 支持128个发送端口,128个接收端口 | |

| BAG | BAG支持从0.5ms至128ms任意值 | |

| 故障注入 | 支持ARINC664网络故障注入,生成错误帧,包括CRC错、数据帧长度错等故障 | |

| 接收模式 | 支持中断、轮询方式接收 | |

| 工作模式 | 支持仿真模式、监测模式 | |

| 冗余功能 | 支持与数据帧头与负荷的纠错功能,支持端口冗余切换 | |

| 操作系统 | 提供WindowsXP、VxWorks、NI的RT系统、LInux系统板卡驱动及API | |

| ******接口 | 1路PCI/PCIe接口 2路RJ45网络接口 IRIG-B时标同步接口 | |

| 供电 | 12V供电 | |

| 尺寸 | 标准PMC板卡149.0*74.0mm,可转PCI、PCIe、PXI等板卡接口形态 | |

| 功耗 | 8W | |

| 工作环境 | 温度 | -40~+75℃ |

| 湿度 | 2%~95%(25℃),无凝结 | |

应用领域:

Ø 航空电子总线通信产品测试

Ø 船舶数据传输总线通信产品测试

Ø 航天设备总线通信产品测试

Ø 以及各类地面总线通信验证与测试系统

1907

1907

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?